【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

年前,因為一單客戶投訴,引發出了關于時鐘buffer芯片客戶端拓撲基礎應用的一些相關知識。因此,本章節就此類芯片,跟大家分享一下時鐘Buffer芯片的定義、工作原理、應用領域、特點優勢等內容。

在分享時鐘buffer芯片前,我們先梳理一下“時鐘”的起源和發展史,這樣有利于解除大家心中疑惑。

一、時鐘的起源

時鐘起源于巴比倫,六千年前的巴比倫人制作出了日晷,通過太陽影子判斷時間。后來為了彌補日晷在無光環境下的不足,設計出了滴漏,用水流速度判斷時間。1283年,英格蘭出現了首個機械時鐘,并逐漸設計出鐘樓、鐘表等計時工具。

二、時鐘的發展歷史

時鐘的發展經歷了三個階段:日晷計時、齒輪組成計時和電子芯片計時。回顧人類科學發展史,計時器的發展歷史是與整個人類文明史同步的。對于生命個體而言,時間長河托起生命之帆。正是因為有了時間測量,人類得以準確記錄下自己的生命足跡。

將石英晶體運用在鐘表上是一種現代的發明,世界上第一個石英表是瑞士在1967年7月制成的。利用石英晶體會產生規律的振動,生成電子產品所需的時鐘信號,推動著科技的高速發展。

進入二十一世紀,萬物互聯已經深入到通信、AIoT、汽車、消費、工業、醫療等眾多領域。隨之而來,不同應用場景下設備之間如何通過高精度時鐘來同步協調,時鐘產品也開始倍受廣泛關注,時鐘產品進入蓬勃發展時期,產品種類也越來越多。

常用的時鐘產品主要分六個大類:振蕩器、時鐘發生器、時鐘緩沖器、抖動衰減產品、時鐘同步產品和其它簡單的時鐘器件。

三、時鐘buffer芯片的定義

講到時鐘buffer芯片,先解釋一下這其中的“buffer”,即:緩沖器的意思。而時鐘緩沖器就是同行中常講的:Clock Buffer,主要分為扇出緩沖器和零延遲緩沖器。時鐘Buffer本身是無法產生頻率源的,它的主要作用是將晶體或晶振產生的時鐘信號進行復制、格式轉換及電平轉換。選對合適的時鐘Buffer,可以減少晶體或晶振使用,降低系統成本。

其實,講到時鐘緩沖器(Clock Buffer),我們就有必要還要認識一下時鐘發生器(Clock Generator),它是用來產生時鐘信號的器件。時鐘發生器常用于數字產品中,所有的組件根據時鐘發生器產生的時鐘信號來同步運算。數字產品必須有時鐘的控制才能精確處理數字信號。若時鐘不穩定,輕則造成數字信號傳送上的錯誤,重則導致數字設備無法正常運作。

至于這兩者具體的作用和應用情況,有興趣的朋友可以自行查閱相關資料,在此我就不過多贅述了。

四、時鐘buffer芯片的工作原理

時鐘buffer芯片的工作原理主要有以下三個:

1、信號放大

時鐘Buffer芯片接收輸入的時鐘信號,并將其放大到足夠的電壓幅度,以確保信號質量和穩定性。

2、信號恢復

在信號傳輸中可能因延遲或噪聲而導致信號失真,時鐘Buffer芯片可恢復信號的波形和周期,確保信號的準確性。

3、信號分配

時鐘Buffer芯片還可以將放大且恢復后的時鐘信號分配給多個輸出端口,保證各個部件同時接收到同步的時鐘信號。

五、扇出型時鐘buffer芯片的選型

基于非PLL的扇出型緩沖器是一種將一路時鐘源信號通過頻率復制生成多路時鐘信號的器件,通常時鐘緩沖器還兼具有時鐘分配,格式轉換和電平轉換的功能。

對于一個大型電子系統來說,需要很多不同頻點和同頻點的時鐘來保障系統的精準運行。但是,如果每個節點都選用晶振或晶體,則會增加PCB園板子尺寸和BOM成本。而選擇集成度更高的時鐘芯片和時鐘緩沖器則可以有效降低系統成本,簡化電路設計,同時也能為系統多個組件提供多路參考時鐘。

那么,時鐘緩沖器究竟應該怎么選,才能更適合自己的使用場景呢?可以從下面這幾個關鍵指標來做選擇:

1、附加(額外)相位抖動

時鐘源經過緩沖器后,緩沖器本身的抖動會增加到時鐘的內在抖動上,從而惡化整個系統時鐘的相位噪聲,這個參數定義為緩沖器的額外抖動或者在指定頻帶范圍內的額外相位抖動。

時鐘緩沖Q器本身不產生時鐘信號,除非有輸入信號,否則不能測量相位抖動。為了定性分析緩沖器對于相位抖動的影響,必須首先測量時鐘源的相位抖動,然后是時鐘源和緩沖器一起工作時的相位抖動,緩沖器的相位抖動可以通過公式計算出來。

在計算相位抖動時通常做的假設是時鐘源和緩沖器噪聲不相關,而且由純粹的隨機抖動組成。

當然,附加相位抖動還依賴于輸入時鐘信號的信號轉換率(slew rate)。較低的slew rat通常導致較高的附件抖動。這也是設計人員需要考慮的。

2、輸入時鐘參數

不同的電子系統的時鐘源是不一樣的,有晶體、振蕩器或者外部時鐘,格式也不一樣,有單端和差分。

有些時鐘緩沖器可以支持3種不同的輸入,涵蓋了目前市場上普遍的輸入方式,可以滿足客戶日常使用。

3、輸出時鐘參數(包括輸出路數、輸出電壓、輸出格式等)

隨著電子產品的功能的增加,對芯片功能和產品功耗的要求也越來越高,針對時鐘bufer口輸出電壓的要求也越來越多。

有些時鐘bufer可以支持多種電壓輸出,單端輸出電壓1.5v/1.8v/2.5v/3.3v;差分輸出電壓2.5v/3.3v。最多可以滿足10路輸出,能夠適配于不同的客戶需求。

當然,時鐘緩沖器的參數還有:輸出之間的指定偏斜;電源噪聲抑制比(PSRR)等。

因此,要想選到更好的時鐘buffer,可以從使用場景的數據指標要求入手,選擇適配這些指標的時鐘Buffer即可。

六、時鐘buffer芯片與時鐘芯片的區別

時鐘緩沖芯片(Clock Buffer Chip)和時鐘芯片(Clock Chip)是兩種常見但功能不同的集成電路。盡管它們都涉及時鐘信號處理,但在設計和應用中有著明顯的區別。

1、時鐘緩沖芯片

相對而言,時鐘緩沖芯片則更專注于時鐘信號的分配和緩沖放大。它們接收來自時鐘源或時鐘芯片的信號,并將其放大、處理后再分配給系統內部的各個模塊,以確保時鐘信號的質量和穩定性。

時鐘緩沖芯片的特點包括:

a. 主要用于時鐘信號的分配、驅動和放大,以克服時鐘信號在傳輸中的衰減和延遲;

b. 通常包含多個時鐘輸出通道,每個通道可以獨立地配置為不同的頻率、相位或占空比;

c. 能夠提供低時延、低抖動的時鐘分配解決方案;

d. 經常用于大型系統或高速數字電路設計中,以確保各個模塊能夠按時獲得正確的時鐘信號。

2、時鐘芯片

時鐘芯片通常被用于產生各種頻率和相位的時鐘信號,用來同步數字系統中的操作。這些芯片通常包括PLL(鎖相環)模塊、分頻器和其他時鐘發生器,以確保設備內部各部件之間的同步性。

時鐘芯片的關鍵特點包括:

a. 提供穩定、精確的時鐘信號;

b. 具有可編程性,能夠根據用戶需求配置輸出時鐘的頻率和相位;

c. 通常集成了各種時鐘管理功能,如頻率調整、時序控制等;

d. 用于主控芯片或系統級集成電路(SoC)中,以便整個系統內各部件同步。

總之,時鐘芯片主要是用于生成、管理時鐘信號,保證整個系統在同步工作;而時鐘緩沖芯片則是專注于時鐘信號的分配和驅動,確保時鐘信號在長距離傳輸時質量穩定。理解它們各自的功能和特點,對于電子系統設計者和工程師來說至關重要。

七、時鐘buffer芯片的主要應用

1、時鐘信號復制

時鐘信號復制簡單理解就是將一路時鐘源信號通過頻率復制生成多路時鐘信號。

從下圖中可以看到1路時鐘信號輸入可以分出5路相同的時鐘信號輸出,并且可以通過OE管腳控制信號輸出與否。

2、時鐘信號格式轉換

除了時鐘信號復制外,現在很多時鐘Buffer也同時具有時鐘信號格式轉換功能,將一種格式的輸入時鐘信號轉換成另一種格式輸出。

下圖是這種Buffer的功能框圖,輸入可以選擇3路中的任意一路,其中輸入口0和1支持的信號格式可以是LVPECL、LVDS、HCSL、SSTL、LVCMOS、LVTTL中任意一種,而XTAL輸入口則支持無源晶體輸入。差分輸出時鐘類型可以通過OUT_MODEA【1:0】及OUT_MODEB【1:0】分別單獨配置,選擇LVPECL、LVDS、HCSL或高阻狀態。

在服務器、網絡設備、存儲設備等應用中,像CPU、PCIe交換芯片、PCIe擴展卡、Wifi控制器、GE口等很多芯片之間都是通過PCIe協議來傳輸高速數據,系統中需要多個HCSL格式的100M參考時鐘,而市場上沒有直接輸出HCSL信號的晶振,這時可以用100M LVDS或LVPECL輸出的晶振,通過Buffer轉換為100M HCSL時鐘信號格式來滿足應用。

3、時鐘信號電平轉換

在下圖中,大家看到有VDD的多個電源PIN,這里的VDD_CORE是核心電壓,也是輸入時鐘信號的電壓,而輸出信號電壓可以不同于VDD_CORE,比如VDD_CORE是3.3V,而VDD_IO可以選擇3.3V、2.5V、1.8V等多種電壓輸出,即時鐘信號的電平轉換。

八、時鐘buffer芯片的特點與優勢

時鐘buffer芯片的核心特點與優勢結合性能、兼容性、功耗及應用場景4方面可歸納到以下5點:

1、高驅動能力與寬頻支持

采用差分輸入/輸出設計,可驅動1MHz~350MHz頻率,滿足多設備同步需求,另外,還可通過寬長比優化電路結構,提升信號擺幅和上升沿速度,增強后端負載驅動能力。

2、低功耗設計與小封裝

設計上注重支持低功耗HCSL和LVDS接口,降低系統整體能耗,符合現代電子設備對節能環保的需求,還采用小型QFN32封裝(5mm×5mm),適合高密度集成場景。

3、低抖動輸出

PCIe 5.0規范下附加抖動僅6fs,滿足高速設備對時序的嚴格要求,且支持PCIe Gen 1/2/3/4/5全代兼容,確保向后兼容性。

4、靈活控制與兼容性

支持通過I2C或獨立引腳控制輸出引腳關斷,增強系統靈活性,同時還兼容PCIe標準,簡化系統設計并降低布線復雜性。

5、電磁兼容性與電壓范圍

支持SSC(靜電放電保護)以降低EMI,保障信號純凈度,且工作電壓為2.5~3.3V,適應不同供電環境。

因此,時鐘buffer芯片通過低抖動、高驅動能力、低功耗及廣泛兼容性,成為高性能計算、高速存儲設備等場景中保障時序一致性的關鍵組件。

九、時鐘buffer芯片的應用領域

時鐘buffer芯片當前均有應用于服務器、存儲設備、PCIe卡、以太網線卡、射頻拉遠單元和基站單元、無線和有線基礎設施、網絡和數據通信、醫療成像、便攜式測試和測量等領域。具體來講,在以下四個高新領域應用最為頻繁和重要:

1、計算機系統

在計算機的主板、處理器、存儲器等部件中廣泛應用,確保各個組件之間的時序一致性,提高系統性能。

2、通信設備

在通信基站、網絡交換設備等通信系統中使用,保證數據傳輸的同步性和穩定性,提高通信質量。

3、工業控制

用于工控系統、自動化設備等領域,確保各個部件的協調運行,實現高效的生產控制。

4、消費電子產品

時鐘Buffer芯片用于數字電視、音頻處理器、攝像機等設備中,提供高質量的音視頻信號。

十、寫在最后面的話

時鐘Buffer芯片通常具有低功耗、小封裝、高穩定性和高頻率等特點。隨著數字電子設備的不斷發展和復雜性的增加,對時鐘信號的要求也越來越高,時鐘Buffer芯片的功能和性能也得到了不斷的提升。它在現代電子設備中的重要性不可忽視,對設備的正常運行和性能提升起著關鍵作用。

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

審核編輯 黃宇

-

半導體

+關注

關注

339文章

30719瀏覽量

263987 -

時鐘緩沖器

+關注

關注

2文章

270瀏覽量

51910 -

時鐘芯片

+關注

關注

2文章

296瀏覽量

42102

發布評論請先 登錄

芯科實驗室推出業界首款通用時鐘緩沖器Si533xx

幫助CLOCK GENERATOR,MPMC和時鐘緩沖器

半導體芯片內部結構詳解

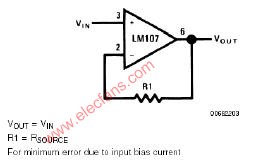

單位增益緩沖器:The Unity-Gain Buffer

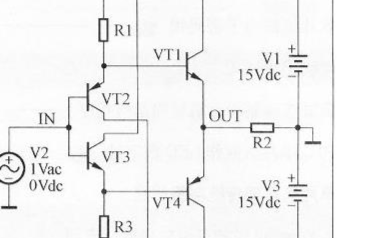

MOS管構成的緩沖器Buffer和漏極開路門OD門的詳細概述

使用IDT時鐘緩沖器提升應用設計

時鐘緩沖器工作原理及常見時鐘緩沖器的國產替代情況

浙江賽思電子時鐘緩沖器的應用條件

半導體“時鐘緩沖器(Clock Buffer )”芯片的詳解;

半導體“時鐘緩沖器(Clock Buffer )”芯片的詳解;

評論