晶振作為電子系統的核心時鐘源,其穩定起振直接關系到設備功能實現。當晶振無法正常啟動時,系統將陷入時序混亂,導致數據傳輸錯誤、控制失靈等嚴重后果。以下從設計、制造、應用三個維度剖析晶振不起振的關鍵問題,并提供針對性解決路徑。

一、設計層面:參數失配與布局缺陷

- ?晶振選型錯誤?

晶振的標稱頻率、負載電容(CL)或等效串聯電阻(ESR)與電路設計要求不匹配時,振蕩條件無法滿足。例如,某低功耗MCU需匹配32.768kHz晶振,若誤用12.5PF負載電容,會導致負性阻抗失衡,引發起振異常。此外,晶振的溫度特性與工作環境不兼容(如工業級應用誤用消費級晶振),也會因溫漂過大而無法穩定工作。

- ?PCB布局不合理?

晶振遠離主控芯片時,長走線易形成天線效應,引入外部噪聲干擾。若晶振下方存在高速信號線或電源走線,容性耦合會破壞時鐘信號完整性。某通信設備案例顯示,晶振與射頻模塊間距不足3mm時,時鐘信噪比大幅下降,導致數據傳輸錯誤率激增。優化方案包括:將晶振緊鄰MCU放置,走線長度控制在5mm內;采用"包地"結構環繞信號線,每隔λ/20打孔接地,形成電磁屏蔽屏障。

二、制造層面:工藝缺陷與材料問題

- ?焊接工藝不當?

焊接過程中的溫度過高或時間過長,會導致晶振內部電性能指標異常。例如,32.768kHz晶振在280℃下焊接超5秒,可能引發特性惡化。此外,晶振制造中的壓封不良或電極雜質,也會導致氣密性破壞或DLD2超差。預防措施包括:控制回流焊溫度曲線(峰值溫度<260℃);返修時禁用烙鐵直接加熱,改用熱風臺確保溫度均勻性。 - ?晶振質量缺陷?

晶振生產過程中的切割精度、電極鍍層厚度不均等問題,會導致頻率特性偏移或起振困難。例如,某批次晶振因電極氧化導致接觸電阻增大,起振成功率僅65%。解決方案包括:選擇具有更高品質的晶振;在采購時要求供應商提供完整的測試報告。

三、應用層面:環境干擾與系統協同

- ?電源噪聲干擾?

電源總線上的紋波噪聲通過VCC引腳傳導至晶振內部,當噪聲幅度超過閾值電壓時,會引發起振失敗或頻率漂移。某醫療設備因電源濾波不足,導致晶振輸出波形畸變,系統誤判率達300%。改進措施包括:在VCC引腳并聯0.1μF陶瓷電容與10μF電解電容,形成高低頻噪聲濾波網絡;必要時串聯22Ω電阻抑制諧振,提升電源純凈度。

- ?機械應力與環境侵蝕?

機械振動或封裝應力可能引發布局微裂,造成時鐘信號間歇性中斷。例如,車載設備在-40℃~+85℃溫沖測試中,晶振因熱膨脹導致頻率漂移超±200ppm,遠超車規級標準。同時,潮濕環境會加速引腳氧化,破壞信號完整性。解決方案包括:采用減震墊隔離晶振安裝區域;優先選用抗沖擊封裝(如金屬外殼);存儲環境控制在≤40℃/≤60%RH。

- ?軟件配置錯誤?

軟件時序配置錯誤可能破壞振蕩穩定性。例如,STM32 LSE驅動等級配置不當,會導致負性阻抗失衡。解決方法包括:在啟動LSE前配置驅動等級(如HAL_RCC);采用數字濾波算法補償瞬時抖動,提升系統容錯能力。

四、驗證與維護要點

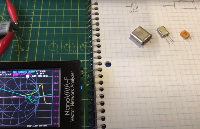

- ?上電測試流程?

設備啟動后監測晶振輸出波形(示波器帶寬>100MHz),驗證無異常抖動或頻率偏移(Δf<±50ppm)。 - ?長期可靠性保障?

存儲環境需控制溫濕度(≤40℃/≤60%RH)。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

晶振

+關注

關注

35文章

3560瀏覽量

73434 -

電子系統

+關注

關注

0文章

508瀏覽量

32286

發布評論請先 登錄

相關推薦

熱點推薦

晶振不起振的系統性解析

晶振不起振的系統性解析

評論