做芯片測試的同學經常會涉及到Continuity測試、Leakage測試、GPIO drive capability測試、GPIO pullup/pulldown resistor測試、standby idd、run idd、IDDQ、MBIST、SCAN等測試,小編在此帶大家總結一下這些測試的基本原理。

- Continuity測試(即OS測試)該測試主要是測試芯片的open/short特性,即測量芯片pin腳對VDD或者GND有沒有短路(short)或斷路(open)。當測某一pin的OS時,應使VDD=0V,同時其他pin的電壓也全為0。下圖為測某一pin對GND的OS測試時的示意圖,ATE會從pin抽一個100uA的電流,下方的二極管導通,在正常工作的情況下,測得的電壓應該在-0.2V~-0.7V之間。

- 下圖為測某一pin對VDD的OS測試時的示意圖,ATE會從pin灌入100uA的電流,上方的二極管導通,在正常工作的情況下,測得的電壓應該在0.2V~0.7V之間。

如果有short情況發生,測得的電壓一般接近0V;如果是open的情況,則測得的電壓一般為5V/-5V(測試程序中設置的鉗位電壓)。- Leakage測試即漏電流測試。在該測試過程中一般將芯片正常上電,然后將pin配置成input狀態,給pin上分別灌入VSS(0V)和VDD的電壓,測量該pin上的電流,一般測量值為-1uA~1uA。

當pin電壓等于VDD時,測得的電流為對GND的漏電流當pin電壓等于VSS時,測得的電流為對VDD的漏電流

當pin電壓等于VDD時,測得的電流為對GND的漏電流當pin電壓等于VSS時,測得的電流為對VDD的漏電流 - GPIO drive capability測試即為GPIO的驅動能力測試GPIO drive capability一般對應datasheet中的VOH/VOL或者IOH/IOL指標,其實VOH/VOL和IOH/IOL是同一個指標,只不過測試方法不同。下圖為VOH或者IOH的測試示意圖。將GPIO配置成output模式,并且輸出高電平(邏輯1)。當測量IOH時,則ATE在pin上施加VDD-0.8V電壓,此時該pin上電流即為IOH。當測量VOH時,則ATE從該pin拉5mA/20mA電流(視該pin的驅動能力而定),此時該pin上測得的電壓即為VOH。

- 下圖為VOL或者IOL的測試示意圖,同樣將GPIO配置成output模式,只不過此時輸出低電平(邏輯0)。當測量IOL時,則ATE在pin上施加0.8V電壓,此時該pin上電流即為IOL。當測量VOL時,則ATE從該pin灌入5mA/20mA電流(視該pin的驅動能力而定),此時該pin上測得的電壓即為VOL。

- Pullup/Pulldown resistor測試該測試目的是測試芯片引腳內部的上拉/下拉電阻的大小。在測試時該pin需要配置成input模式。下圖為上拉電阻的測試示意圖。當測試上拉電阻時需將該pin配置成input狀態,同時打開pullup設置,給pin腳施加電壓0V,測量pin腳上電流,然后根據R=U/I可以計算出上拉電阻的阻值。

- 下圖為下拉電阻的測試示意圖。當測試下拉電阻時需將該pin配置成input狀態,同時打開pulldown設置,給pin腳施加VDD電壓5V,測量pin腳上電流,然后根據R=U/I可以計算出下拉拉電阻的阻值。

- standby idd對于MCU來說,standby idd即是在standby mode下測量VDD pin上電流。Standby mode一般為芯片的低功耗模式,芯片內部大部分時鐘均處于關閉的狀態,只保留LPO時鐘作為芯片的喚醒時鐘。需要注意的是一般測standby idd時候需要將VDD pin上并接的電容去掉,因為電容存在充放電的過程,可能會對電流的測量產生影響。

- Run iddRun idd的測試與standby idd基本一致,只不過會讓芯片處于run mode,有些會要求將外設的時鐘打開進行測試。

- IDDQIDDQ即靜態電流,指CMOS電路在穩定狀態(無信號跳變)下的電源電流。在無缺陷的CMOS電路中,靜態電流應接近零(僅有漏電流,一般微安級)。正常CMOS邏輯在穩態下,PMOS和NMOS管不同時導通,理論靜態電流很小。缺陷影響:物理缺陷(如柵極氧化物短路、電源/地橋接)會形成額外電流路徑,導致IDDQ升高。

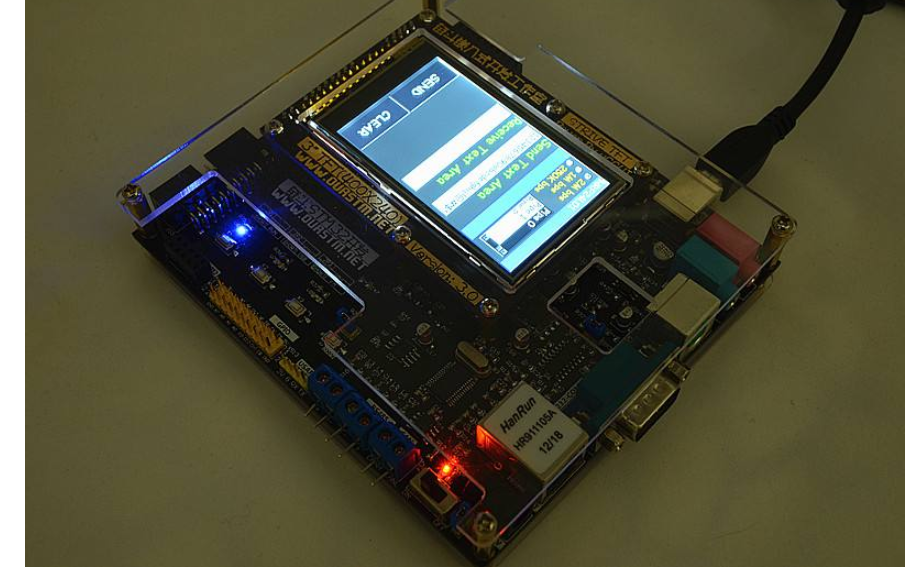

- MBISTMBIST一般指SRAM的測試,采用芯片內部自建的一些測試邏輯來進行測試,機臺只需要通過JTAG接口下達測試的指令,即可從TDO接口獲取測試結果。MBIST測試結束后一般會有兩個信號輸出BIST_DONE和BIST_FAIL。

- SCANscan就是把普通寄存器替換成可掃描的寄存器,目的是創建control和observation點,然后把所有的可掃描寄存器連接在一起串成掃描鏈(scan chain),利用掃描鏈,工具自動產生測試patterns,讓寄存器處于一個特定的值(control),然后將期望的值移出來進行對比(observe),來判斷芯片是否有缺陷。SCAN測試一般分stuck-at和transition測試,stuch-at測試覆蓋固定電平缺陷,但對時序敏感缺陷無效;transition則主要針對時序路徑的延遲缺陷。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片

+關注

關注

463文章

54006瀏覽量

465880 -

二極管

+關注

關注

149文章

10403瀏覽量

178389 -

芯片測試

+關注

關注

6文章

171瀏覽量

21150

發布評論請先 登錄

相關推薦

熱點推薦

超好學!AutoCAD輔助繪圖全圖解

`軟件教程, 制圖《超好學(AutoCAD輔助繪圖全圖解100%)》以通俗易懂的語言、翔實生動的實例,全面介紹了AutoCAD 2012的使用方法和技巧。本書共分11章,內容涵蓋AutoCAD

發表于 11-07 21:16

UCOS移植過程全講解教程免費下載

本文檔的主要內容詳細介紹的是UCOS移植過程全講解教程免費下載包括了: UCOSIII移植準備工作, UCOSIII簡介, UCOSIII測試軟件設計

發表于 10-21 17:40

?21次下載

超全的芯片測試原理講解

超全的芯片測試原理講解

評論