固態(tài)變壓器(Solid State Transformer, SST)是電力電子領(lǐng)域最復(fù)雜的系統(tǒng)之一。在實(shí)際工業(yè)工程中,固變SST 的完整控制代碼量通常在數(shù)萬行至十萬行級別,且必須運(yùn)行在**“多核 DSP + 多片 FPGA 集群”**的分布式異構(gòu)硬件架構(gòu)上。

主流中高壓 固變SST 采用**“交-直-交”三級式物理拓?fù)?*。全景拆解 固變SST 四大核心軟件層的控制代碼,詳細(xì)說明其實(shí)現(xiàn)功能,并提取工程級 DSP 核心算法的 C 語言代碼骨架。

第一部分:系統(tǒng)的“大腦” —— 頂層狀態(tài)機(jī)與聯(lián)鎖保護(hù)

固變SST 內(nèi)部擁有龐大的高壓直流電容陣列和高頻變壓器,絕對不能“一鍵直接上電發(fā)波” ,否則通電瞬間的極高浪涌電流會直接炸毀整個系統(tǒng)。這部分代碼通常運(yùn)行在 DSP 的慢速定時器(如 1ms)中。

實(shí)現(xiàn)功能:

防浪涌預(yù)充電:控制交流接觸器,先串入電阻給高壓電容緩慢充電。

三級平滑軟啟動:嚴(yán)格按“高壓整流 → 隔離降壓 → 低壓逆變”的順序逐級解鎖,并采用參考值斜坡上升(Ramp-up)防止超調(diào)。

極速硬件級急停:實(shí)時輪詢?nèi)到y(tǒng)狀態(tài),發(fā)生異常時拍掉高壓斷路器。

工程核心 C 代碼骨架:

C

typedef enum { STANDBY, PRECHARGE, CHB_START, DAB_START, VSC_START, RUNNING, FAULT } SST_State_t;

void SST_System_StateMachine_Task_1ms(void) {

// 1. 絕對最高優(yōu)先級:故障急停與封鎖

if (Check_Hardware_Desat_Fault() || Check_Fiber_Comms_Loss()) {

Disable_All_PWM_Hardware_Trip(); // 底層硬件引腳瞬間拉低

Open_Main_HV_Breaker(); // 斷開高壓交流斷路器

System_State = FAULT;

}

// 2. 狀態(tài)機(jī)流轉(zhuǎn)調(diào)度

switch(System_State) {

case STANDBY:

if (Receive_Start_Cmd) {

Close_Precharge_Contactor(); // 閉合預(yù)充電接觸器,串入電阻

System_State = PRECHARGE;

}

break;

case PRECHARGE:

// 依靠電網(wǎng)不控整流,等待所有高壓電容充至額定值的 85%

if (Get_Vdc_Global_Avg() > 0.85f * V_GRID_PEAK) {

Close_Main_Contactor(); // 旁路預(yù)充電電阻

System_State = CHB_START;

}

break;

case CHB_START:

Enable_CHB_PWM(); // 解鎖高壓側(cè)發(fā)波

Ramp_Up(&VDC_HV_REF, TARGET_HV); // 軟啟動:高壓直流目標(biāo)值斜坡上升

if (Is_CHB_Stable()) System_State = DAB_START;

break;

case DAB_START:

Enable_DAB_PWM(); // 解鎖中間隔離級發(fā)波

Ramp_Up(&VDC_LV_REF, TARGET_LV); // 軟啟動建立低壓直流母線

if (Is_LV_Bus_Stable()) System_State = VSC_START;

break;

case VSC_START:

Enable_VSC_PWM(); // 解鎖末級逆變器,正式對外供電

System_State = RUNNING;

break;

}

}

第二部分:高壓網(wǎng)側(cè) 交-直(AC-DC)整流級控制

本級直接接入萬伏高壓電網(wǎng),通常采用級聯(lián) H 橋(CHB)或模塊化多電平(MMC)拓?fù)洹?/p>

實(shí)現(xiàn)功能:

高功率因數(shù)并網(wǎng)(PFC) :鎖定電網(wǎng)相位,控制網(wǎng)側(cè)吸收/回饋的電流為純正弦波,且與電網(wǎng)電壓同相。

全局總壓穩(wěn)定:維持幾十個串聯(lián)子模塊的直流總電壓恒定(保證整機(jī)能量守恒)。

模塊均壓(最核心難點(diǎn)) :微調(diào)各個模塊的占空比,克服器件制造公差,確保幾十個模塊均分萬伏高壓,防止個體過壓炸毀。

工程核心 C 代碼骨架(運(yùn)行于 DSP 100μs 高頻中斷) :

C

void Stage1_CHB_Control_ISR(void) {

// 1. 鎖相環(huán) (SRF-PLL):獲取電網(wǎng)相位 Theta

Run_PLL(V_grid_a, V_grid_b, V_grid_c, &Theta, &Omega);

// 2. 全局穩(wěn)壓外環(huán)

// 【工程避坑】單相功率脈動會在電容產(chǎn)生 100Hz 巨大紋波,必須用滑動平均濾波器(MAF)濾除,否則注入電網(wǎng)3次諧波

float vdc_total_filtered = MAF_Filter_100Hz( Calculate_Total_Vdc() );

float id_ref = PI_Calc(&PI_Vdc_Global, VDC_HV_REF - vdc_total_filtered);

float iq_ref = 0.0f; // 無功電流指令設(shè)為0,維持單位功率因數(shù)

// 3. 電網(wǎng)電流內(nèi)環(huán) (dq 坐標(biāo)系前饋解耦控制)

Park_Transform(I_grid_a, I_grid_b, I_grid_c, Theta, &id_fb, &iq_fb);

float vd_cmd = PI_Calc(&PI_Id, id_ref - id_fb) - Omega * L * iq_fb + Vd_grid_ff;

float vq_cmd = PI_Calc(&PI_Iq, iq_ref - iq_fb) + Omega * L * id_fb + Vq_grid_ff;

// 反變換得到三相全局基礎(chǔ)調(diào)制波 (-1.0 ~ 1.0)

Inv_Park_Transform(vd_cmd, vq_cmd, Theta, &D_base_a, &D_base_b, &D_base_c);

// 4. 模塊級相內(nèi)均壓控制 (以 A 相的 N 個模塊為例)

// 【致命細(xì)節(jié)】電流過零點(diǎn)處會導(dǎo)致均壓正負(fù)劇烈翻轉(zhuǎn),必須做平滑防抖處理

float sign_Ia = Smooth_Sign(I_grid_a);

for(int i = 0; i < N; i++) {

// 計(jì)算單個模塊電壓偏差,經(jīng)過 PI 算出微調(diào)占空比

float vdc_err_mod = VDC_MOD_REF - MAF_Filter_100Hz(Vdc_A[i]);

float delta_duty = PI_Calc(&PI_Balance_A[i], vdc_err_mod);

// 模塊發(fā)波指令 = 基礎(chǔ)波 + (微調(diào)量 * 電流充放電極性)

Duty_A[i] = D_base_a + (delta_duty * sign_Ia);

// 動態(tài)限幅抗積分飽和

Duty_A[i] = Saturate(Duty_A[i], -0.95f, 0.95f);

}

// 將最終 Duty 數(shù)組通過光纖發(fā)送給底層 FPGA 生成 PWM

}

第三部分:高頻隔離 直-直(DC-DC)變壓級控制

每個高壓 H 橋模塊背后都接一個雙有源橋(DAB),數(shù)十個 DAB 的輸出端并聯(lián)在一起(ISOP架構(gòu)),匯聚成低壓直流母線。這是 SST 的“心臟”。

實(shí)現(xiàn)功能:

高頻電氣隔離與降壓:利用 10kHz~100kHz 的高頻變壓器實(shí)現(xiàn)物理隔離,并降壓至 400V/800V 直流。

軟開關(guān)與能量雙向流動:通過單移相(SPS)控制變壓器原副邊方波的相位差,實(shí)現(xiàn)無損能量傳輸。

并聯(lián)均流:強(qiáng)制幾十個并聯(lián)的 DAB 模塊輸出相等的電流,防止個別漏感偏小的模塊過載。

工程核心 C 代碼骨架(移相與均流閉環(huán)) :

C

void Stage2_DAB_Control_ISR(void) {

// 1. 低壓直流母線穩(wěn)壓 (全局外環(huán))

float vdc_lv_err = VDC_LV_REF - ADC_Read(VDC_LV_BUS);

// 生成基礎(chǔ)移相角指令 (范圍 -0.5 ~ 0.5,代表 -180° ~ 180°)

// 正值代表高壓側(cè)超前(正向送電),負(fù)值代表反向回饋

float phase_shift_base = PI_Calc(&PI_LV_Bus, vdc_lv_err);

// 2. DAB 模塊級并聯(lián)均流控制 (ISOP Current Sharing)

float i_out_avg = Calculate_Total_LV_Current() / NUM_MODULES;

for(int i = 0; i < NUM_MODULES; i++) {

float i_err = i_out_avg - I_out_DAB[i];

// 生成均流微調(diào)移相角 (帶寬必須極慢,防止與主電壓環(huán)“搶方向”導(dǎo)致振蕩)

float delta_shift = PI_Calc(&PI_Share[i], i_err);

// 合成最終下發(fā)給該模塊的移相角

float final_shift = phase_shift_base + delta_shift;

// 物理限幅 (防止移相角過大導(dǎo)致變壓器偏磁炸機(jī))

final_shift = Saturate(final_shift, -0.45f, 0.45f);

// 更新高頻發(fā)波寄存器 (底層轉(zhuǎn)換為高頻時鐘計(jì)數(shù)器的 Tick 延遲)

Update_DAB_Phase_Shift_Reg(i, final_shift);

}

}

第四部分:低壓 直-交(DC-AC)逆變級控制

低壓母線通過逆變器輸出。以 固變SST 替代傳統(tǒng)配電變壓器為小區(qū)供電為例,通常采用構(gòu)網(wǎng)型(Grid-Forming / V/f控制) 。

實(shí)現(xiàn)功能:

建立交流微網(wǎng):主動生成幅值恒定(380V)、頻率恒定(50Hz)的純凈三相交流電。

抗短路與抗畸變:面對用戶側(cè)突然短路、三相不平衡、非線性負(fù)載時,維持波形并執(zhí)行限流保護(hù)。

工程核心 C 代碼骨架:

C

void Stage3_VSC_Control_ISR(void) {

// 1. 內(nèi)部虛擬時鐘發(fā)生器 (主動造 50Hz 參考相位,代替鎖相環(huán))

Virtual_Theta += 2.0f * PI * 50.0f * T_SAMPLE;

if(Virtual_Theta > 2.0f * PI) Virtual_Theta -= 2.0f * PI;

// 2. 交流電壓外環(huán) (維持輸出 380V 線電壓恒定)

Park_Transform(V_load_a, V_load_b, V_load_c, Virtual_Theta, &vd_load, &vq_load);

// Vd 軸參考值為交流峰值 (約 311V),Vq 軸設(shè)為 0

float id_ref = PI_Calc(&PI_Vd_Inv, 311.0f - vd_load);

float iq_ref = PI_Calc(&PI_Vq_Inv, 0.0f - vq_load);

// 核心保護(hù):電流指令動態(tài)限幅 (防止外部短路燒毀 IGBT)

id_ref = Saturate(id_ref, -MAX_INV_CURRENT, MAX_INV_CURRENT);

iq_ref = Saturate(iq_ref, -MAX_INV_CURRENT, MAX_INV_CURRENT);

// 3. 電流內(nèi)環(huán)帶前饋解耦 (極速指令跟蹤)

Park_Transform(I_inv_a, I_inv_b, I_inv_c, Virtual_Theta, &id_inv, &iq_inv);

float vd_cmd = PI_Calc(&PI_Id_Inv, id_ref - id_inv) - Omega * L_f * iq_inv + vd_load;

float vq_cmd = PI_Calc(&PI_Iq_Inv, iq_ref - iq_inv) + Omega * L_f * id_inv + vq_load;

// 4. SVPWM 空間矢量發(fā)波

Inv_Park_Transform(vd_cmd, vq_cmd, Virtual_Theta, &v_alpha, &v_beta);

SVPWM_Generate(v_alpha, v_beta, VDC_LV_BUS_FB, &Duty_Inv_A, &Duty_Inv_B, &Duty_Inv_C);

}

第五部分:底層的隱形守護(hù)者 —— FPGA 硬件描述代碼

如果只靠上面的 C 語言代碼,固變SST 是活不過 1 秒鐘的。在固變SST 研發(fā)中,超過一半的代碼量和核心動作是由主控/從控 FPGA 上的 Verilog/VHDL 邏輯電路直接完成的,完全脫離 CPU 的軟件執(zhí)行周期:

CPS-PWM 載波移相(算力卸載) :DSP 只發(fā)一個占空比,F(xiàn)PGA 負(fù)責(zé)內(nèi)部生成數(shù)十個精確錯開(如相差 36°)的三角載波,自動錯開發(fā)波。這讓等效開關(guān)頻率翻了幾十倍,極大減小了網(wǎng)側(cè)電感體積。

死區(qū)插入(Dead-time Insertion) :純硬件邏輯死死鎖住上下管,強(qiáng)制插入 2μs~4μs 的死區(qū)時間,防止同一橋臂直通短路。

納秒級硬件退飽和保護(hù)(Hardware Desat / OCP) :這是 固變SST 的最后一道免死金牌。當(dāng)?shù)讓?a target="_blank">驅(qū)動電路檢測到 IGBT/SiC 發(fā)生短路并拉高故障引腳時,F(xiàn)PGA 的硬件門電路會在 不到 1μs(一微秒)內(nèi) 強(qiáng)行切斷所有 PWM 發(fā)波,并觸發(fā) DSP 停機(jī)。這個速度是 C 語言軟件中斷永遠(yuǎn)無法企及的。

Aurora 高速光纖通信:維持主控大腦(DSP)與數(shù)十個位于上萬伏高電位上的子模塊之間“微秒級延遲”的 ADC 數(shù)據(jù)上傳與發(fā)波指令下達(dá)。

固變SST 的控制系統(tǒng)是一個明確分工的多核異構(gòu)體系:

DSP 的 C 語言是“大腦” :負(fù)責(zé)復(fù)雜的數(shù)學(xué)題(坐標(biāo)變換、多變量解耦 PI、鎖相、諧波濾除、均壓均流)。它只輸出一個結(jié)果——“占空比”和“移相角”。

FPGA 的 HDL 語言是“小腦與脊髓” :負(fù)責(zé)具體的脈沖分配執(zhí)行(高速高精度的時鐘管理)以及條件反射式的保命(微秒級短路保護(hù))。

審核編輯 黃宇

-

SST

+關(guān)注

關(guān)注

0文章

143瀏覽量

36199

發(fā)布評論請先 登錄

固變SST隔離驅(qū)動器的非對稱延時補(bǔ)償:提升級聯(lián)型系統(tǒng)單元開關(guān)同步性

干變與油變制造商向固變SST(固態(tài)變壓器)賽道轉(zhuǎn)型的技術(shù)與商業(yè)邏輯剖析

繼續(xù)死磕固變SST,2027年就是固變SST商業(yè)化爆發(fā)年!

基于SiC模塊的固變SST支撐起新一代新能源汽車超級充電樁的閃充系統(tǒng)

軟件定義電力電子:面向基于SiC模塊的多電平固態(tài)變壓器(SST)通用化控制底座(Open-SST)研究

固變SST固態(tài)變壓器DAB雙有源橋隔離DC-DC變換器熱設(shè)計(jì),移相控制策略,EMC設(shè)計(jì)

面向多槍并聯(lián)快充的固變SST動態(tài)負(fù)載平衡與阻抗匹配控制策略研究

磁-熱-流多場耦合:固變SST 高頻變壓器采用納米晶磁芯的散熱策略

軟件定義電網(wǎng):多端口固變SST的自適應(yīng)能量管理與虛擬慣量控制

SiC固變PEBB對中國SST固邊變壓器行業(yè)發(fā)展的技術(shù)價值和商業(yè)價值

SST固變的技術(shù)經(jīng)濟(jì)學(xué)分析與商業(yè)化部署路徑

基于62mm封裝SiC模塊及驅(qū)動的固變SST PEBB的硬件配置

固變(SST)市場銷售額潛力評估以及對干變和油變的替代進(jìn)程

變壓器行業(yè)技術(shù)演進(jìn)與市場格局:干變、油變與固變(SST)

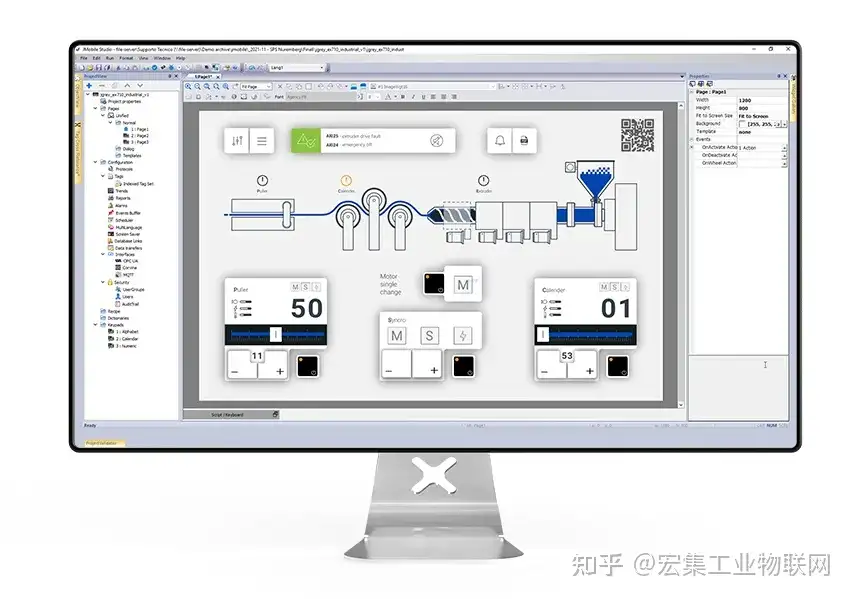

工業(yè)HMI選型指南(中):決定效率的9項(xiàng)核心軟件功能指標(biāo)

全景拆解固變SST四大核心軟件層的控制代碼

全景拆解固變SST四大核心軟件層的控制代碼

評論