寬禁帶電力電子轉(zhuǎn)換半導(dǎo)體工業(yè)標(biāo)準(zhǔn)深度分析:JEDEC JC-70 委員會規(guī)程對SiC碳化硅器件壽命評估框架

隨著全球?qū)δ茉崔D(zhuǎn)換效率和功率密度要求的日益嚴(yán)苛,以碳化硅(SiC)和氮化鎵(GaN)為代表的寬禁帶(WBG)半導(dǎo)體已從實(shí)驗(yàn)室研發(fā)邁向大規(guī)模工業(yè)應(yīng)用 。寬禁帶半導(dǎo)體憑借其高擊穿電場、高飽和電子漂移速度以及優(yōu)異的熱導(dǎo)率,正在電力電子領(lǐng)域引發(fā)一場革命,特別是在電動汽車(EV)、光伏儲能(ESS)以及高頻電源轉(zhuǎn)換器中展現(xiàn)出替代傳統(tǒng)硅(Si)基器件的巨大潛力 。然而,WBG 器件在展現(xiàn)卓越性能的同時(shí),也引入了與硅基器件完全不同的物理退化機(jī)制。傳統(tǒng)的基于硅基半導(dǎo)體的可靠性評估標(biāo)準(zhǔn),如早期的 MIL-STD 或 JEDEC 靜態(tài)應(yīng)力測試,已無法全面覆蓋 WBG 器件在動態(tài)高頻工作條件下的潛在失效模式 。

在此背景下,JEDEC JC-70 委員會(寬禁帶電力電子轉(zhuǎn)換半導(dǎo)體委員會)應(yīng)運(yùn)而生。自 2017 年成立以來,該委員會致力于為 GaN(JC-70.1)和 SiC(JC-70.2)制定專門的工業(yè)標(biāo)準(zhǔn) 。通過密集發(fā)布 JEP194、JEP195 和 JEP200 等多項(xiàng)指南,JC-70 從物理本質(zhì)出發(fā),建立了一套涵蓋柵極氧化層完整性、參數(shù)漂移不穩(wěn)定性以及動態(tài)能量損耗量化的全新科學(xué)框架 。這些標(biāo)準(zhǔn)不僅解決了 WBG 器件在任務(wù)關(guān)鍵型應(yīng)用中的資質(zhì)認(rèn)證壁壘,更深刻地改變了工業(yè)界對半導(dǎo)體壽命預(yù)測的邏輯基礎(chǔ)。

JEP194:SiC MOSFET 柵極氧化層可靠性與穩(wěn)健性的科學(xué)評估

柵極氧化層可靠性一直是 SiC MOSFET 商業(yè)化進(jìn)程中的核心技術(shù)瓶頸 。盡管 SiC 器件通常采用與硅器件類似的二氧化硅(SiO2?)作為絕緣介質(zhì),但 SiC 的寬帶隙特征導(dǎo)致 SiC/SiO2? 界面的導(dǎo)帶偏移(Conduction Band Offset)遠(yuǎn)小于 Si/SiO2? 界面,這使得電子更容易通過 Fowler-Nordheim(FN)隧道效應(yīng)進(jìn)入氧化層,從而引發(fā)電荷捕獲和過早擊穿 。JEP194 標(biāo)準(zhǔn)通過規(guī)范本征壽命提取與外在缺陷剔除程序,為 SiC 柵極氧化層的穩(wěn)健性評估提供了標(biāo)準(zhǔn)化的技術(shù)支撐 。

本征可靠性與 TDDB 測試的標(biāo)準(zhǔn)化程序

JEP194 的首要目的在于規(guī)范 SiC 襯底上 MOS 器件(電容器或晶體管)的介質(zhì)壽命提取方法 。對于氧化層厚度遠(yuǎn)大于 10nm 的功率器件,標(biāo)準(zhǔn)化的經(jīng)時(shí)擊穿(TDDB)測試是評估其“本征行為”的關(guān)鍵 。早期的研究由于未能有效區(qū)分本征失效與缺陷相關(guān)的外在失效,往往對 SiC 的本征壽命給出過于悲觀的預(yù)測 。

在 JEP194 的框架下,工業(yè)界通常采用恒定電壓應(yīng)力(CVS)測試。通過在加速電場和加速溫度下對大量樣品進(jìn)行加壓,記錄失效時(shí)間。利用威布爾(Weibull)分布函數(shù)對數(shù)據(jù)進(jìn)行擬合,可以確定器件的平均失效時(shí)間(t63%?)并推導(dǎo)出激活能 。這種方法允許制造商建立“10 年或 20 年壽命曲線”,驗(yàn)證器件在推薦柵極驅(qū)動電壓(如 +18V 或 +15V)下的長期生存能力 。基本半導(dǎo)體的 B3M 系列 SiC MOSFET 在設(shè)計(jì)中便充分考慮了這一本征壽命要求,確保在大批量制造中具備極高的工藝冗余和本征穩(wěn)健性 。

外在失效管理與“馬拉松應(yīng)力測試”

相比于已基本被理解的本征失效,外在缺陷導(dǎo)致的早期失效(即浴缸曲線中的嬰幼兒期死亡率)對任務(wù)關(guān)鍵型應(yīng)用(如電動汽車主逆變器)構(gòu)成了更大的威脅 。這些缺陷可能源于外延層缺陷、金屬雜質(zhì)沉積或制造過程中的微小顆粒,它們會在局部區(qū)域增強(qiáng)電場,導(dǎo)致氧化層在遠(yuǎn)低于設(shè)計(jì)壽命的時(shí)間點(diǎn)發(fā)生崩潰 。

為了解決這一難題,JEP194 引入了“馬拉松應(yīng)力測試”(Marathon Stress Test)的概念 。這種測試不同于針對少量樣品的小規(guī)模 TDDB 測試,它要求對大規(guī)模樣本施加接近現(xiàn)實(shí)應(yīng)用但更具挑戰(zhàn)性的電壓應(yīng)力 。例如,在針對 18V 柵極電壓設(shè)計(jì)的器件上施加 30V 的過應(yīng)力,通過大規(guī)模統(tǒng)計(jì)篩選,識別并剔除具有潛在外在缺陷的器件 。這種標(biāo)準(zhǔn)化篩選程序使得 SiC MOSFET 能夠達(dá)到與成熟硅基 IGBT 同等的 FIT(單位時(shí)間失效數(shù))水平,消除了工業(yè)界對其可靠性的長期疑慮 。

| 特性維度 | 傳統(tǒng) TDDB 測試 | 馬拉松應(yīng)力測試 (Marathon Stress) |

|---|---|---|

| 評估目標(biāo) | 本征 wear-out 壽命 | 外在缺陷導(dǎo)致的早期失效 (Infant Mortality) |

| 樣本量 | 較小 (通常 < 77 pcs/批次) | 大規(guī)模 (數(shù)百至數(shù)千只器件) |

| 應(yīng)力條件 | 極高電壓/溫度以誘發(fā)崩潰 | 適度加速應(yīng)力,模擬惡劣工況 |

| 失效模型 | 威布爾分布 β>1 | 針對 β≈1 的隨機(jī)失效進(jìn)行剔除 |

| 工業(yè)價(jià)值 | 工藝平臺開發(fā)與壽命聲明 | 生產(chǎn)線質(zhì)量監(jiān)控與高可靠性篩選 |

JEP195:SiC 柵極開關(guān)不穩(wěn)定性與參數(shù)漂移的動態(tài)評估

SiC MOSFET 與硅 MOSFET 的另一個(gè)顯著差異在于其柵極閾值電壓(VGS(th)?)的動態(tài)不穩(wěn)定性 。SiC 界面存在較高密度的近界面陷阱(Near-Interface Traps),這些陷阱在開關(guān)過程中會反復(fù)捕獲和釋放載流子,導(dǎo)致閾值電壓發(fā)生可逆或永久性的漂移 。JEP195 標(biāo)準(zhǔn)(《電力電子轉(zhuǎn)換用碳化硅金屬氧化物半導(dǎo)體器件柵極開關(guān)不穩(wěn)定性評估指南》)專門針對這一現(xiàn)象制定了詳盡的測量與評估規(guī)程 。

閾值電壓遲滯與捕獲動力學(xué)

在 SiC 器件中,由于陷阱電荷的存在,從負(fù)壓向正壓掃描(Upsweep)和從正壓向負(fù)壓掃描(Downsweep)測得的 VGS(th)? 并不相等,形成了明顯的遲滯現(xiàn)象 。通常情況下,Upsweep 測得的閾值電壓較低,這是因?yàn)樵陉P(guān)斷期間的負(fù)向柵極電壓使界面捕獲了來自價(jià)帶的空穴,從而增加了界面正電荷 。隨著開關(guān)次數(shù)的增加,這種動態(tài)捕獲行為會導(dǎo)致 VGS(th)? 發(fā)生不可忽視的凈漂移 。

如果 VGS(th)? 向正向漂移,會導(dǎo)致溝道電阻(RCH?)增加,進(jìn)而使器件的總導(dǎo)通電阻(RDS(on)?)上升,增加導(dǎo)通損耗并可能引發(fā)熱失效 。如果發(fā)生負(fù)向漂移,則會增加誤導(dǎo)通的風(fēng)險(xiǎn),在半橋拓?fù)渲锌赡軐?dǎo)致嚴(yán)重的直通電流損壞器件 。JEP195 的出臺,使得系統(tǒng)設(shè)計(jì)師能夠基于標(biāo)準(zhǔn)化的測量數(shù)據(jù),量化最壞情況下的閾值電壓變動區(qū)間,從而在柵極驅(qū)動電路設(shè)計(jì)中留出足夠的安全裕度 。

動態(tài)柵極應(yīng)力(DGS)測試協(xié)議

JEP195 引入的核心測試方法是動態(tài)柵極應(yīng)力測試(DGS,也稱為 AC-BTI) 。傳統(tǒng)的 HTGB(高溫柵偏)測試是靜態(tài)的,而 DGS 測試要求在最高額定工作溫度下,以實(shí)際應(yīng)用中的高頻(如 100kHz 至 500kHz)對柵極施加方波脈沖 。

研究表明,對于 SiC MOSFET,在開關(guān)次數(shù)超過 108 次后,動態(tài)開關(guān)帶來的不穩(wěn)定性(GSI)會超越靜態(tài) BTI 成為主導(dǎo)退化機(jī)制 。例如,某型 1200V SiC 功率器件在經(jīng)歷 3×1011 次開關(guān)循環(huán)后,測得的 VGS(th)? 漂移量可能超過 4V,而這種效應(yīng)在純靜態(tài)測試中幾乎不可見 。JEP195 規(guī)范了這種測試的波形、預(yù)處理脈沖(Gate Conditioning)以及測量間隔,確保了不同供應(yīng)商之間數(shù)據(jù)的可比性 。

基本半導(dǎo)體 B3M 器件的動態(tài)穩(wěn)健性驗(yàn)證

基本半導(dǎo)體在其 B3M 系列產(chǎn)品的可靠性驗(yàn)證中嚴(yán)格執(zhí)行了類似于 JEP195 的動態(tài)測試。根據(jù)實(shí)驗(yàn)數(shù)據(jù),B3M013C120Z 在 250kHz 的高頻 DGS 測試下,經(jīng)歷了超過 1011 次開關(guān)循環(huán),其靜態(tài)參數(shù)仍能完美保持在規(guī)格書范圍內(nèi),展現(xiàn)了極佳的界面電荷穩(wěn)定性 。這種優(yōu)異的表現(xiàn)源于其第三代芯片技術(shù)對 SiC/SiO2? 界面的精細(xì)優(yōu)化,通過引入高效的氮化(Nitridation)工藝降低了陷阱密度 。

| 測試項(xiàng)目 | 縮寫 | 測試條件 (以 B3M013C120Z 為例) | 測試規(guī)模/結(jié)果 |

|---|---|---|---|

| 動態(tài)柵極應(yīng)力 | DGS | f=250kHz,VGS?=?10/+22V,T=25°C,300H | 1.08×1011 次循環(huán), 0 失效 |

| 動態(tài)反偏應(yīng)力 | DRB | VDS?=960V,f=50kHz,dv/dt≥50V/ns,556H | 1011 次循環(huán), 0 失效 |

| 高溫柵偏(+) | HTGB+ | Tj?=175°C,VGS?=22V,1000H | 3 批次 * 77 pcs, 0 失效 |

| 高溫反偏 | HTRB | Tj?=175°C,VDS?=1200V,1000H | 3 批次 * 77 pcs, 0 失效 |

JEP200:軟開關(guān)拓?fù)渲形灰?a href="http://www.3532n.com/tags/電流/" target="_blank">電流損耗的量化難題

在高頻電源變換領(lǐng)域,為了進(jìn)一步提升效率并降低電磁干擾(EMI),工業(yè)界廣泛采用 LLC 諧振、移相全橋(PSFB)等軟開關(guān)拓?fù)?。這些拓?fù)渲荚谕ㄟ^零電壓開關(guān)(ZVS)消除開關(guān)瞬間的電壓-電流重疊損耗 。然而,研究發(fā)現(xiàn),即便是在理論上的 ZVS 條件下,高性能功率半導(dǎo)體依然存在未被解釋的額外開關(guān)損耗,這一難題阻礙了效率向 99% 以上的極致跨越 。

輸出電容遲滯(Coss? Hysteresis)的物理本質(zhì)

JEP200 標(biāo)準(zhǔn)專門解決了由輸出電容遲滯引起的位移電流相關(guān)損耗的量化問題 。當(dāng)器件處于關(guān)斷狀態(tài)時(shí),漏源電壓(VDS?)的變化會驅(qū)動位移電流通過寄生輸出電容 Coss?(由 Cgd?+Cds? 組成) 。對于先進(jìn)的 Si 基超結(jié)(Super-Junction)MOSFET、SiC MOSFET 甚至 GaN HEMT,由于其復(fù)雜的內(nèi)部結(jié)構(gòu)和陷阱效應(yīng),Coss? 的充電和放電過程并不是完全可逆的 。

在電荷-電壓(Q?V)特性平面上,這種不可逆性表現(xiàn)為一條閉合的磁滯回路。回路所包圍的面積即代表了每個(gè)開關(guān)周期中因位移電流損耗掉的能量(Ediss?) 。在 MHz 級別的開關(guān)頻率下,這種以往被忽略的損耗可能與導(dǎo)通損耗相當(dāng),甚至成為限制功率密度的主要熱源 。

JEP200 測試方法與工業(yè)優(yōu)化意義

JEP200 提供了標(biāo)準(zhǔn)化的測試電路、測量算法和數(shù)據(jù)提取規(guī)程,適用于所有類型的功率晶體管(Si, SiC, GaN) 。該標(biāo)準(zhǔn)建議使用正弦波或梯形波激勵(lì),通過高精度源測量單元(SMU)提取大信號遲滯損耗 。

精確的熱建模:通過量化 Ediss?,系統(tǒng)工程師可以建立更準(zhǔn)確的器件熱模型,防止在極端 ZVS 工況下發(fā)生熱失控 。

器件選型參考:JEP200 數(shù)據(jù)的公開使得用戶能夠科學(xué)地對比不同供應(yīng)商的器件。例如,在 600V 以上的應(yīng)用中,某些增強(qiáng)型 GaN 器件的遲滯損耗可能表現(xiàn)出明顯的 dV/dt 依賴性,而通過 JEP200 測試可以快速識別其最優(yōu)工作窗口 。

驅(qū)動方案優(yōu)化:了解位移電流的貢獻(xiàn),有助于優(yōu)化柵極驅(qū)動電阻和死區(qū)時(shí)間,平衡開關(guān)速度與遲滯損耗 。

基本半導(dǎo)體的 ED3 系列 SiC 模塊在產(chǎn)品手冊中明確列出了 Eoss?(輸出電容存儲能量)參數(shù)。例如,BMF540R12MZA3 在 800V 條件下的典型存儲能量為 509μJ 。JEP200 的出臺將促使此類參數(shù)從簡單的靜態(tài)存儲能量向動態(tài)遲滯損耗演進(jìn),進(jìn)一步細(xì)化 SiC 模塊在高頻工業(yè)逆變器中的效率表現(xiàn) 。

任務(wù)關(guān)鍵型應(yīng)用中的資質(zhì)認(rèn)證與科學(xué)壽命預(yù)測框架

JEDEC JC-70 系列標(biāo)準(zhǔn)的密集發(fā)布,從根本上重塑了工業(yè)界對 WBG 器件資質(zhì)認(rèn)證(Qualification)的認(rèn)知。它標(biāo)志著功率半導(dǎo)體評價(jià)體系從“靜態(tài)參數(shù)時(shí)代”全面跨入“動態(tài)物理機(jī)制時(shí)代” 。

打通汽車與重工業(yè)認(rèn)證壁壘

對于電動汽車主驅(qū)、航空航天輔助動力單元以及軌道交通等任務(wù)關(guān)鍵型應(yīng)用,器件的可靠性門檻通常以 ppb(十億分之一)級別衡量 。傳統(tǒng)的 AEC-Q101 標(biāo)準(zhǔn)雖然嚴(yán)格,但其測試項(xiàng)目很大程度上仍是為硅器件設(shè)計(jì)的 。JC-70 標(biāo)準(zhǔn)通過引入 DGS、DRB 以及 Marathon Stress 測試,為 WBG 制造商提供了與汽車 OEM 廠商溝通的“共同科學(xué)語言” 。

基本半導(dǎo)體的車規(guī)級產(chǎn)品(如 AB2M 系列)在符合 AEC-Q101 的基礎(chǔ)上,進(jìn)一步通過了嚴(yán)苛的 H3TRB 和高溫高濕測試(HV-H3TRB),將反向偏置電壓設(shè)置在 80% 至 100% 的擊穿電壓范圍內(nèi) 。這種“加嚴(yán)可靠性驗(yàn)證”直接響應(yīng)了 JEP194 中對外在缺陷零容忍的要求,成功打通了其在主驅(qū)動模塊中的應(yīng)用壁壘 。

壽命評估的科學(xué)框架重塑

JC-70 標(biāo)準(zhǔn)群形成了一個(gè)完整的閉環(huán)壽命評估體系:

預(yù)防期:JEP194 的篩選規(guī)程通過 Marathon 測試和標(biāo)準(zhǔn) TDDB 模型,在生產(chǎn)端消除了早期失效和本征 wear-out 風(fēng)險(xiǎn) 。

運(yùn)行期:JEP195 解決了器件在開關(guān)運(yùn)行中的參數(shù)穩(wěn)定性問題,確保系統(tǒng)在全壽命周期內(nèi)保持一致的效率和熱表現(xiàn) 。

邊界期:JEP200 通過對極高頻下細(xì)微損耗的量化,界定了器件在功率密度追求上的物理極限 。

這一框架使得壽命評估不再僅僅是基于歷史數(shù)據(jù)的統(tǒng)計(jì)推斷,而是基于對陷阱捕獲、載流子注入以及磁滯能量耗散等物理本質(zhì)的深刻理解 。

工業(yè)實(shí)踐案例:基于 JEDEC 理念的 SiC 模塊技術(shù)解析

通過分析基本半導(dǎo)體(BASIC Semiconductor)的技術(shù)演進(jìn),可以清晰地觀察到工業(yè)界如何將 JC-70 的科學(xué)準(zhǔn)則轉(zhuǎn)化為產(chǎn)品競爭力。其 ED3 系列工業(yè)模塊與 B3M 系列分立器件是這一理念的典型載體 。

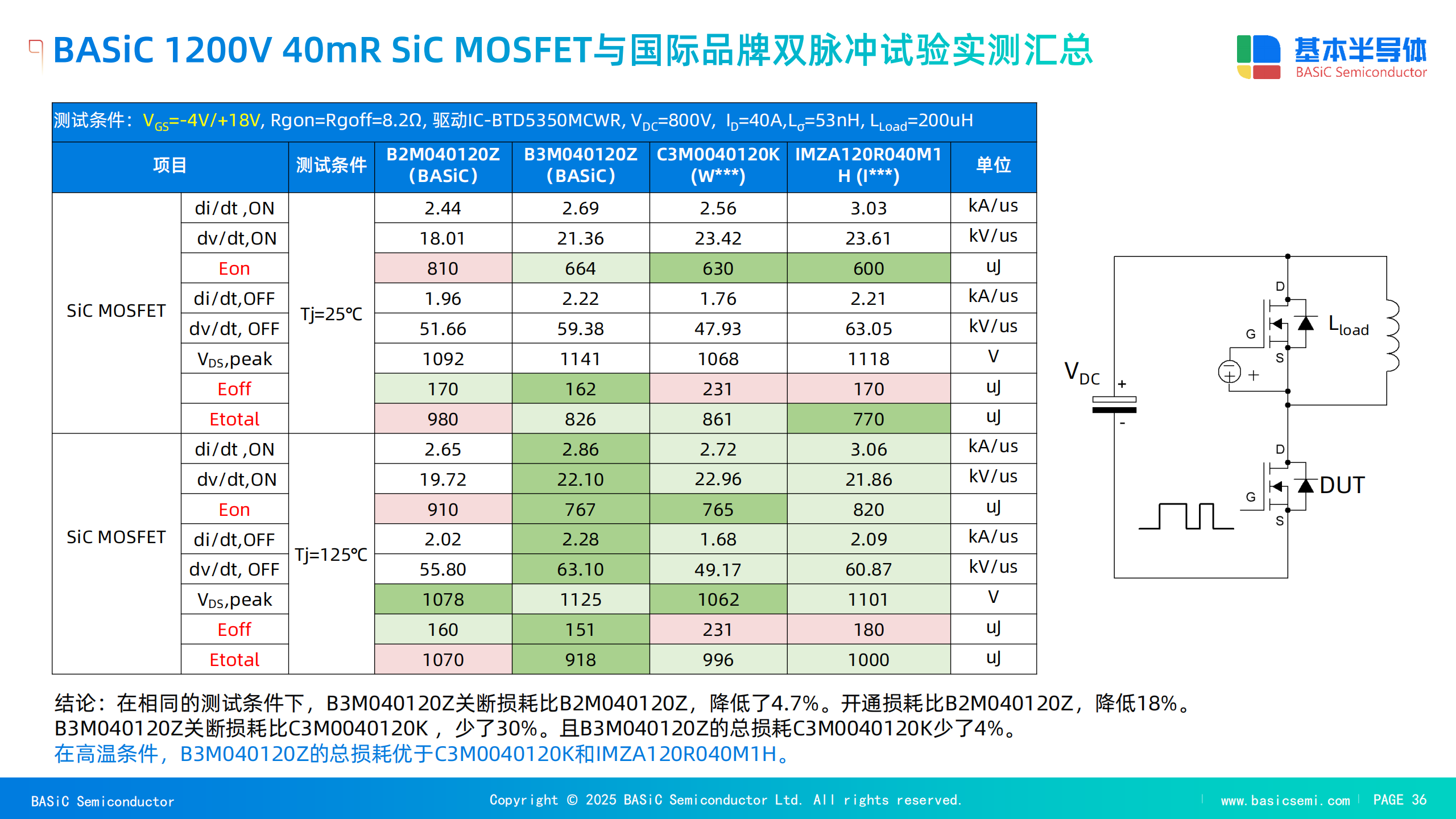

第三代(B3M)芯片的 FOM 優(yōu)化

基本半導(dǎo)體的 B3M 技術(shù)平臺通過優(yōu)化有源區(qū)結(jié)構(gòu),將品質(zhì)因數(shù)(FOM=RDS(on)?×QG?)降低了約 30% 。這種優(yōu)化不僅僅是為了提升效率,更是為了降低柵極驅(qū)動的負(fù)荷。較低的 QG? 意味著在相同頻率下,驅(qū)動電流更小,從而減輕了 JEP195 中提到的動態(tài)柵極應(yīng)力對氧化層的累積沖擊 。

| 指標(biāo) | B2M040120Z (第二代) | B3M040120Z (第三代) | 行業(yè)競爭對手 (溝槽柵) |

|---|---|---|---|

| 工藝類型 | 平面柵 | 平面柵 | 溝槽柵 |

| RDS(on)? (25°C) | 40mΩ | 40mΩ | 40mΩ |

| RDS(on)? (175°C) | 75mΩ | 70mΩ | 78mΩ |

| QG? | 85nC | 90nC | 107nC |

| FOM 值 | 3600mΩ?nC | 3400mΩ?nC | 4280mΩ?nC |

表格數(shù)據(jù)顯示,B3M 技術(shù)在保持平面柵高可靠性的同時(shí),通過優(yōu)化 FOM 實(shí)現(xiàn)了接近甚至優(yōu)于某些溝槽柵器件的動態(tài)性能,這正是 JEP194 與 JEP195 所倡導(dǎo)的“性能與穩(wěn)健性平衡”的體現(xiàn) 。

ED3 模塊的熱管理與高可靠性封裝

針對 1200V/540A 的高功率工況,基本半導(dǎo)體的 ED3 模塊引入了高性能的 Si3?N4? AMB 基板 。相較于傳統(tǒng)的 Al2?O3? 或 AlN 基板,Si3?N4? 具有極高的抗彎強(qiáng)度(700 N/mm2)和優(yōu)異的斷裂韌性 。在經(jīng)歷了 1000 次溫度沖擊測試后,Si3?N4? 基板仍能保持良好的接合強(qiáng)度,有效防止了陶瓷與銅箔之間的分層 。這種模塊級的穩(wěn)健性與 JEP194 的氧化層級穩(wěn)健性相結(jié)合,構(gòu)成了 WBG 器件在惡劣工業(yè)環(huán)境下長期運(yùn)行的基石 。

| 陶瓷覆銅板性能對比 | Al2?O3? (氧化鋁) | AlN (氮化鋁) | Si3?N4? (氮化硅) |

|---|---|---|---|

| 熱導(dǎo)率 (W/mK) | 24 | 170 | 90 |

| 熱膨脹系數(shù) (ppm/K) | 6.8 | 4.7 | 2.5 |

| 抗彎強(qiáng)度 (N/mm2) | 450 | 350 | 700 |

| 剝離強(qiáng)度 (N/mm) | 24 | - | ≥10 |

| 1000 次冷熱沖擊結(jié)果 | 分層明顯 | 較脆、有分層 | 結(jié)合強(qiáng)度良好 |

集成 Miller 鉗位的高速驅(qū)動方案

為了應(yīng)對 SiC MOSFET 高速開關(guān)(高 dv/dt)帶來的米勒效應(yīng)干擾,基本半導(dǎo)體及其旗下青銅劍技術(shù)(Bronze Technologies)開發(fā)了集成米勒鉗位(Miller Clamp)功能的隔離驅(qū)動器(如 BTD5350 系列) 。

根據(jù)雙脈沖實(shí)驗(yàn)數(shù)據(jù),在 800V/40A 的測試條件下,如果不使用米勒鉗位,下管柵極電壓受 dv/dt 耦合影響會產(chǎn)生高達(dá) 7.3V 的電壓波動,遠(yuǎn)超其 VGS(th)? 閾值,從而引發(fā)誤導(dǎo)通 。而開啟集成米勒鉗位后,該波動被強(qiáng)行抑制在 2V 以下,確保了關(guān)斷期間的電平安全 。這一硬件級解決方案,是實(shí)現(xiàn) JEP195 所要求的動態(tài)參數(shù)穩(wěn)定運(yùn)行的物理前提 。

結(jié)論

JEDEC JC-70 委員會發(fā)布的 JEP194、JEP195 和 JEP200 標(biāo)準(zhǔn),標(biāo)志著寬禁帶電力電子行業(yè)已經(jīng)走出了“性能崇拜”的初期階段,正式進(jìn)入了“科學(xué)可靠性”驅(qū)動的成熟期。JEP194 通過 TDDB 與馬拉松測試,為 SiC 柵極氧化層建立了從本征壽命到外在缺陷篩選的完整防線;JEP195 深刻揭示了 SiC 界面捕獲效應(yīng)背后的參數(shù)漂移邏輯,為動態(tài)工況下的穩(wěn)定性評估提供了準(zhǔn)繩;而 JEP200 則填補(bǔ)了高頻軟開關(guān)領(lǐng)域能量損耗量化的空白,為電力電子設(shè)備邁向極高功率密度掃清了障礙。

這些標(biāo)準(zhǔn)共同構(gòu)成了一個(gè)互補(bǔ)且嚴(yán)密的科學(xué)框架,不僅重塑了制造商的研發(fā)與質(zhì)控體系,更極大地增強(qiáng)了終端用戶在電動汽車、可再生能源等關(guān)鍵領(lǐng)域采用 WBG 技術(shù)的信心。隨著基本半導(dǎo)體等領(lǐng)先企業(yè)將這些國際標(biāo)準(zhǔn)深入貫徹到從芯片設(shè)計(jì)、模塊封裝到驅(qū)動配套的全產(chǎn)業(yè)鏈中,寬禁帶半導(dǎo)體必將以其不可替代的效率優(yōu)勢,全面加速全球能源轉(zhuǎn)換的綠色進(jìn)程 。

審核編輯 黃宇

-

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

31154瀏覽量

266063 -

寬禁帶

+關(guān)注

關(guān)注

2文章

57瀏覽量

7610

發(fā)布評論請先 登錄

碳化硅 (SiC) MOSFET 功率器件熱設(shè)計(jì)基礎(chǔ)與工程實(shí)踐

SiC碳化硅MOSFET精準(zhǔn)驅(qū)動電源架構(gòu)的解析

SiC碳化硅功率半導(dǎo)體銷售團(tuán)隊(duì)認(rèn)知教程:電力電子硬開關(guān)與軟開關(guān)技術(shù)的演進(jìn)邏輯

銷售團(tuán)隊(duì)認(rèn)知培訓(xùn):電力電子接地系統(tǒng)架構(gòu)與SiC碳化硅功率器件的高頻應(yīng)用

功率半導(dǎo)體銷售培訓(xùn)手冊:電力電子核心技術(shù)與SiC碳化硅功率器件的應(yīng)用

SiC碳化硅MOSFET功率半導(dǎo)體銷售培訓(xùn)手冊:電源拓?fù)渑c解析

傾佳電子光伏與儲能產(chǎn)業(yè)功率半導(dǎo)體分立器件從IGBT向碳化硅MOSFET轉(zhuǎn)型的深度研究報(bào)告

碳化硅 (SiC) MOSFET 分立器件與功率模塊規(guī)格書深度解析與應(yīng)用指南

傾佳電子碳化硅SiC MOSFET驅(qū)動特性與保護(hù)機(jī)制深度研究報(bào)告

傾佳電子SiC碳化硅MOSFET串?dāng)_抑制技術(shù):機(jī)理深度解析與基本半導(dǎo)體系級解決方案

SiC碳化硅功率半導(dǎo)體:電力電子行業(yè)自主可控與產(chǎn)業(yè)升級的必然趨勢

碳化硅器件在工業(yè)應(yīng)用中的技術(shù)優(yōu)勢

基本半導(dǎo)體碳化硅 MOSFET 的 Eoff 特性及其在電力電子領(lǐng)域的應(yīng)用

寬禁帶電力電子轉(zhuǎn)換半導(dǎo)體工業(yè)標(biāo)準(zhǔn)深度分析:JEDEC JC-70 委員會規(guī)程對SiC碳化硅器件壽命評估框架

寬禁帶電力電子轉(zhuǎn)換半導(dǎo)體工業(yè)標(biāo)準(zhǔn)深度分析:JEDEC JC-70 委員會規(guī)程對SiC碳化硅器件壽命評估框架

評論