探索LMH1982多速率視頻時鐘發生器:特性、應用與設計要點

在視頻處理領域,時鐘發生器的性能對系統的穩定性和圖像質量起著至關重要的作用。今天,我們就來深入探討一款功能強大的多速率視頻時鐘發生器——LMH1982,看看它有哪些獨特之處,以及在實際應用中如何進行設計。

文件下載:lmh1982.pdf

一、LMH1982簡介

LMH1982是一款模擬鎖相環(PLL)時鐘發生器,能夠輸出同時同步或“鎖定”到H同步和V同步輸入參考時序的SD和HD視頻時鐘。它還具備可編程的幀首(TOF)脈沖發生器,可與參考幀同步。該芯片采用兩級PLL架構,第一級基于VCXO的PLL(PLL 1)需要外部27 MHz VCXO和環路濾波器,第二級由三個集成VCO和環路濾波器的PLL(PLL 2、3、4)組成。

二、特性亮點

1. 雙LVDS輸出時鐘

提供兩個同時的LVDS輸出時鐘,具有可選頻率和Hi - Z功能。SD時鐘可選27 MHz或67.5 MHz,HD時鐘可選74.25 MHz、74.25/1.001 MHz、148.5 MHz或148.5/1.001 MHz。這種靈活的頻率選擇能夠滿足不同視頻格式的需求。

2. 低抖動輸出

低抖動輸出時鐘可直接連接到FPGA串行器,滿足SMPTE SDI抖動規范。這對于保證視頻信號的準確傳輸和處理至關重要,能夠有效減少圖像的失真和干擾。

3. 可編程TOF脈沖

TOF脈沖可指示幀的起始位置,甚至提供格式交叉鎖定功能。通過編程輸出格式寄存器,可以指定輸出時序、相對于參考的輸出時序偏移以及與參考幀的輸出初始化(對齊)。

4. 雙參考端口

提供兩個參考端口(A和B),帶有H和V同步輸入,支持輸入和輸出時序的交叉鎖定。這使得系統在參考信號選擇上更加靈活,增強了系統的穩定性和適應性。

5. 外部環路濾波器

外部環路濾波器允許控制環路帶寬、抖動傳輸和鎖定時間特性。結合可編程的PLL參數,系統設計師可以根據具體應用優化環路帶寬和環路響應。

三、應用領域

1. 視頻同步與鎖定

在視頻制作和廣播領域,視頻同步和鎖定是確保多個視頻源和設備之間時間一致性的關鍵。LMH1982能夠精確地將輸出時鐘和TOF脈沖與參考信號對齊,實現視頻的同步和鎖定,保證畫面的穩定和流暢。

2. FPGA SDI SerDes恢復時鐘生成

在FPGA的SDI串行器和解串器(SerDes)應用中,需要精確的時鐘信號來恢復和處理視頻數據。LMH1982的低抖動輸出時鐘能夠滿足這些要求,為FPGA提供穩定可靠的時鐘源。

3. 三速率3G/HD/SD - SDI SerDes

適用于三速率3G/HD/SD - SDI SerDes系統,能夠支持不同速率的視頻信號處理,滿足高清和標清視頻的傳輸和轉換需求。

4. 視頻采集、轉換、編輯和分發

在視頻采集、轉換、編輯和分發過程中,需要精確的時鐘信號來保證數據的準確傳輸和處理。LMH1982可以為這些系統提供穩定的時鐘支持,確保視頻質量不受影響。

5. 視頻顯示和投影儀

在視頻顯示和投影儀中,準確的時鐘信號對于圖像的顯示質量至關重要。LMH1982能夠提供穩定的時鐘信號,保證圖像的清晰和無閃爍。

四、設計要點

1. 電源供應

LMH1982需要3.3 V和2.5 V的電源供應,并且對電源的穩定性和噪聲有一定要求。在設計時,應確保電源的調節精度在±5%以內,并且具有低噪聲特性。同時,要注意電源的上電順序,建議先開啟3.3 V電源,再開啟2.5 V電源,以避免內部ESD結構正向偏置導致的問題。為了減少閂鎖的風險,可以在2.5 V電源(陽極)和3.3 V電源(陰極)之間外部連接一個肖特基二極管。

2. 布局設計

- 電源布線:使用靠近的低噪聲線性穩壓器為芯片提供干凈的3.3 V和2.5 V電源,并進行適當的電源旁路處理,以確保最佳的輸出抖動性能。

- 時鐘布線:將LVDS輸出的SD和HD時鐘通過受控的100 - Ω差分阻抗線路由到邊緣安裝的SMA連接器或后續階段。如果使用差分探頭直接在板上測量時鐘,則差分線應端接100 Ω。

- 環路濾波器布局:將環路濾波器組件(R8、C10、C27和C28)緊密布局在LMH1982旁邊,以減少信號干擾和延遲。

3. 編程配置

通過I2C接口對控制寄存器進行編程,可配置LMH1982的各種功能。在編程過程中,需要注意以下幾點:

- 輸出時鐘頻率編程:根據所需的輸出格式,選擇合適的SD和HD時鐘頻率,并將其編程到相應的寄存器中。

- TOF時序編程:為了確保輸出時鐘和TOF脈沖的正確初始化和對齊,需要編程輸出TOF時序。

- PLL 1分頻器編程:根據輸入參考格式,編程PLL 1的分頻器,使VCXO時鐘與H同步輸入信號相位鎖定。

4. 148.35 MHz PLL初始化

當選擇148.35 MHz作為HD_CLK輸出時,需要進行特定的PLL初始化序列。否則,時鐘可能會出現占空比誤差、頻率誤差和/或高抖動。具體的初始化步驟如下:

- 編程HD_FREQ = 11b和HD_HIZ = 0(寄存器08h),選擇148.35 MHz并啟用HD_CLK輸出。

- 對以下寄存器參數編程為1(可在一個寫序列中完成):FB_DIV = 1(寄存器04h - 05h)、TOF_RST = 1(寄存器09h - 0Ah)、REF_LPFM = 1(寄存器0Fh - 10h)、EN_TOF_RST = 1(寄存器0Ah)。

- 等待至少2個27 MHz VCXO時鐘周期,然后編程EN_TOF_RST = 0。

5. 參考和PLL鎖定狀態監測

LMH1982具有參考檢測器和PLL鎖定檢測器,可通過NO_REF和NO_LOCK狀態標志輸出引腳以及REF_VALID、SD_LOCK和HD_LOCK狀態位來指示輸入參考和設備PLL的鎖定狀態。在設計過程中,應合理設置參考丟失(LOR)閾值和PLL鎖定閾值,以確保系統的穩定性和可靠性。

五、典型應用電路示例

1. 模擬參考鎖定用于三速率SDI視頻

在這個應用中,LMH1982與LMH1981多格式視頻同步分離器配合使用,將模擬參考信號轉換為同步的SD和HD時鐘信號。FPGA的SerDes模塊利用這些時鐘信號進行三速率SDI視頻的處理和傳輸。

2. SDI參考鎖定用于三速率SDI視頻

該應用中,LMH1982直接接收SDI參考信號,將其作為參考源,實現輸出時鐘和TOF脈沖的同步。這種方式適用于需要直接從SDI信號中提取參考信息的系統。

六、總結

LMH1982作為一款功能強大的多速率視頻時鐘發生器,在視頻處理領域具有廣泛的應用前景。通過合理的設計和配置,它能夠為各種視頻系統提供穩定、精確的時鐘信號,保證視頻的高質量傳輸和處理。在實際應用中,電子工程師需要充分了解其特性和設計要點,結合具體需求進行優化設計,以發揮其最大的性能優勢。

你在使用LMH1982的過程中遇到過哪些問題?或者對它的某些特性有更深入的疑問嗎?歡迎在評論區留言討論。

-

視頻處理

+關注

關注

2文章

113瀏覽量

19381

發布評論請先 登錄

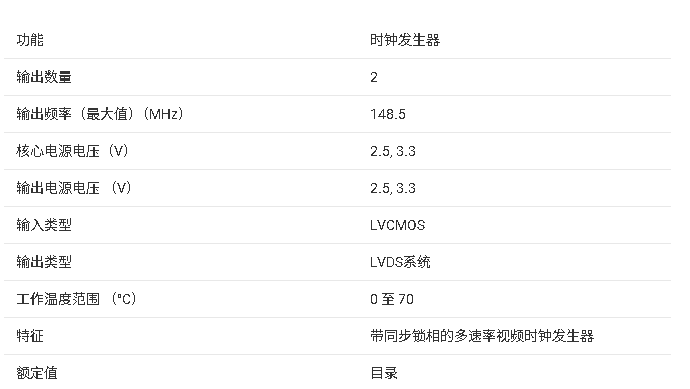

LMH1982 具有同步鎖相的多速率視頻時鐘發生器

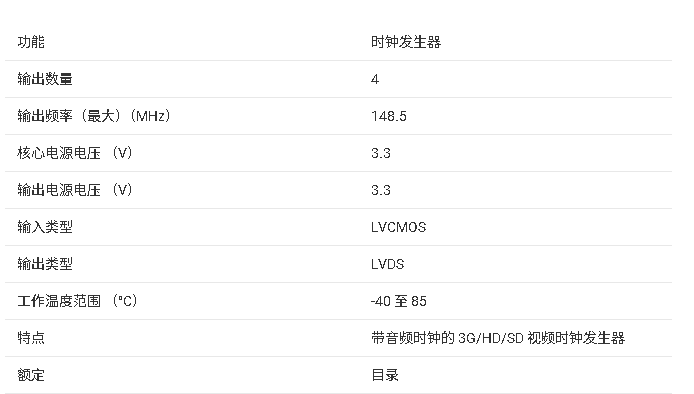

LMH1983高度集成的可編程音頻/視頻(AV)時鐘發生器數據表

?LMH1983 3G/HD/SD視頻時鐘發生器技術文檔總結

探索時鐘發生器的競爭優勢

探索LMH1982多速率視頻時鐘發生器:特性、應用與設計要點

探索LMH1982多速率視頻時鐘發生器:特性、應用與設計要點

評論