CDCLVC11xx系列LVCMOS時鐘緩沖器:高性能設計的理想之選

在電子設計領域,時鐘緩沖器是保障信號穩定傳輸和系統精確運行的關鍵組件。德州儀器(TI)的CDCLVC11xx系列LVCMOS時鐘緩沖器以其卓越的性能和靈活的配置,在通用通信、工業和消費應用等領域展現出強大的競爭力。今天,我們就來深入探討這個系列的產品。

文件下載:cdclvc1102.pdf

產品特性:高性能與低誤差的完美結合

多扇出比與高兼容性

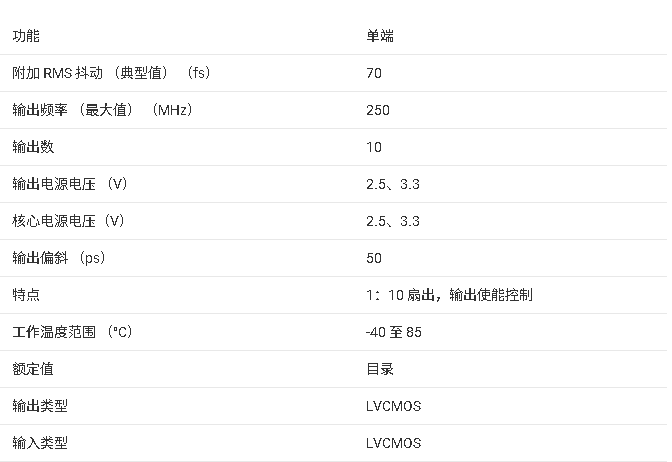

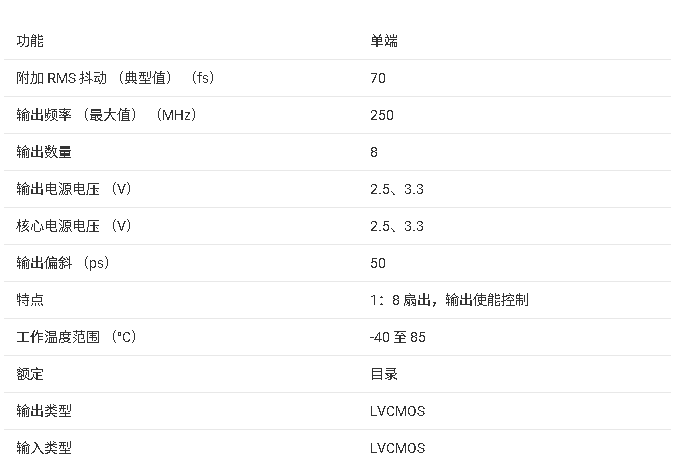

CDCLVC11xx系列提供了從1:2到1:12的七種不同扇出比選擇,能滿足多樣化的設計需求。而且,所有器件引腳兼容,這使得在設計過程中更換不同扇出比的器件變得輕松自如,大大提高了設計的靈活性和可維護性。

超低偏差與抖動

在信號傳輸中,偏差和抖動是影響信號質量的重要因素。CDCLVC11xx系列表現出色,引腳間偏差(Skew)小于50 ps,附加抖動(Jitter)小于100 fs(3.3V供電,250 MHz時)。如此低的偏差和抖動,確保了信號的精確同步和穩定傳輸,為系統的高性能運行提供了有力保障。

寬電壓與溫度范圍

該系列支持3.3V和2.5V兩種供電電壓,最大時鐘頻率分別可達250 MHz(3.3V)和180 MHz(2.5V)。同時,其工作溫度范圍為 -40°C至85°C,能適應各種復雜的工作環境,無論是高溫的工業現場還是低溫的戶外設備,都能穩定工作。

異步輸出使能控制

CDCLVC11xx系列支持異步輸出使能控制(1G),當1G引腳為低電平時,輸出將切換到低狀態。這一特性使得在應用中可以根據需要靈活地啟用或禁用緩沖時鐘輸出,提高了系統的控制靈活性。

產品規格:全面保障設計安全與性能

絕對最大額定值

在設計過程中,了解器件的絕對最大額定值至關重要。CDCLVC11xx系列的電源電壓范圍為 -0.5V至4.6V,輸入和輸出電壓范圍為 -0.5V至VDD + 0.5V(最大值限制為4.6V)。輸入電流和連續輸出電流分別限制在 -20 mA至20 mA和 -50 mA至50 mA之間。最大結溫為125°C,存儲溫度范圍為 -65°C至150°C。超出這些額定值可能會對器件造成永久性損壞,因此在設計時必須嚴格遵守。

ESD 評級

靜電放電(ESD)是電子器件的潛在威脅。CDCLVC11xx系列具有良好的ESD防護能力,人體模型(HBM)靜電放電評級為 ±4000V,帶電設備模型(CDM)評級為 ±1500V。這使得器件在生產和使用過程中能更好地抵御靜電干擾,提高了產品的可靠性。

推薦工作條件

為了確保器件的最佳性能,推薦的工作條件是電源電壓在3.0V至3.6V(3.3V供電)或2.3V至2.7V(2.5V供電)之間。輸入電壓的低電平(VIL)和高電平(VIH)也有相應的要求,例如在3.0V至3.6V供電時,VIL為VDD / 2 - 600 mV,VIH為VDD / 2 + 600 mV。此外,輸入閾值電壓(Vth)為VDD / 2 mV,輸入轉換速率(tr/tf)為1V/ns至4V/ns,最小脈沖寬度(tw)和時鐘輸入頻率(fCLK)也有明確的規定。

熱性能與電氣特性

熱性能方面,不同封裝的器件具有不同的熱阻,如CDCLVC1102的結到環境熱阻(RθJA)為149.4°C/W,結到外殼(頂部)熱阻(RθJC(top))為69.4°C/W。電氣特性上,靜態器件電流(IDD)在不同供電電壓下有所不同,例如在3.6V供電時典型值為6 mA,2.7V供電時典型值為3 mA。功率下降電流(IPD)最大為60 μA,輸出阻抗(ROUT)在3.3V供電時為45Ω至60Ω。

開關特性

開關特性是衡量時鐘緩沖器性能的重要指標。在3.3V ± 0.3V供電時,傳播延遲(tPLH, tPHL)為0.8 ns至2.0 ns,輸出偏差(tsk(o))小于50 ps,上升和下降時間(tr/tf)為0.3 ns至0.8 ns。在2.5V ± 0.2V供電時,傳播延遲為1 ns至2.6 ns,上升和下降時間為0.3 ns至1.2 ns。這些特性確保了信號在傳輸過程中的快速響應和準確切換。

應用與設計:靈活配置滿足多樣需求

典型應用場景

以一個背板應用為例,CDCLVC11xx可以將100 MHz的信號從本地LVCMOS振蕩器進行扇出,為CPU、FPGA和PLL等設備提供時鐘信號。在這個應用中,CPU時鐘可以接受全擺幅直流耦合的LVCMOS信號,通過在CDCLVC11xx附近放置串聯電阻來匹配走線的特性阻抗,減少反射。FPGA時鐘同樣采用直流耦合,并在附近放置合適的串聯電阻。而PLL可以接受較低幅度的信號,因此使用了戴維南等效終端,并且由于PLL接收器具有內部偏置,在共模電壓不匹配時可以使用交流耦合。

詳細設計步驟

在設計過程中,首先要根據圖5和電氣特性表來確定匹配CDCLVC11xx輸出阻抗與傳輸線特性阻抗所需的串聯電阻。對于未使用的輸出引腳,可以將其懸空,以降低系統的組件成本。同時,要參考電源供應建議部分,采用合適的濾波技術來減少電源噪聲對緩沖器的影響。

電源供應與布局:保障穩定運行的關鍵

電源供應建議

高性能時鐘緩沖器對電源噪聲非常敏感,電源噪聲會顯著增加緩沖器的附加抖動。因此,必須采取措施減少系統電源的噪聲。可以使用濾波電容來消除電源中的低頻噪聲,旁路電容則為高頻噪聲提供低阻抗路徑,保護電源系統免受感應波動的影響。旁路電容應選擇低等效串聯電阻(ESR)的類型,并盡可能靠近電源端子放置,以減少電感。此外,TI建議在板級電源和芯片電源之間插入鐵氧體磁珠,以隔離時鐘緩沖器產生的高頻開關噪聲,但要選擇直流電阻非常低的磁珠,以確保電源端子的電壓滿足器件正常工作的要求。

布局指南

在PCB布局方面,要合理放置電源旁路電容。對于元件側安裝,建議使用0402尺寸的電容,方便信號布線。旁路電容與器件電源之間的連接應盡可能短,電容的另一側應通過低阻抗連接接地平面。參考圖14的概念布局,可以更好地實現這一要求。

文檔支持與注意事項

相關鏈接與文檔更新通知

TI為CDCLVC11xx系列提供了豐富的技術文檔、支持和社區資源、工具和軟件等相關鏈接,方便工程師快速獲取所需信息。同時,工程師可以通過在ti.com上的設備產品文件夾中注冊“Alert me”,接收文檔更新的每周摘要通知,及時了解產品信息的變化。

靜電放電注意事項

由于這些器件的內置ESD保護有限,在存儲或處理時,應將引腳短接在一起或放置在導電泡沫中,以防止MOS柵極受到靜電損壞。

CDCLVC11xx系列LVCMOS時鐘緩沖器憑借其高性能、低誤差、寬電壓和溫度范圍等優點,為電子工程師提供了一個可靠的設計選擇。在實際應用中,我們需要根據具體的設計需求,合理選擇器件參數,嚴格遵循電源供應和布局建議,以確保系統的穩定運行。大家在使用CDCLVC11xx系列產品的過程中,有沒有遇到過一些特別的設計挑戰呢?歡迎在評論區分享你的經驗和想法。

-

電子設計

+關注

關注

42文章

1681瀏覽量

49848

發布評論請先 登錄

CDCLVC11xx 3.3V和2.5V LVCMOS高性能時鐘緩沖器系列數據表

CDCLVC11xx系列LVCMOS時鐘緩沖器:高性能設計的理想之選

CDCLVC11xx系列LVCMOS時鐘緩沖器:高性能設計的理想之選

評論