LMK05028:高性能網絡同步時鐘的卓越之選

在通信基礎設施和工業應用領域,對時鐘同步的要求愈發嚴苛,一款優秀的網絡同步時鐘設備顯得尤為重要。今天,我們就來深入探討一下德州儀器(TI)的LMK05028,它在滿足這些應用的嚴格時序要求方面表現出色。

文件下載:lmk05028.pdf

一、LMK05028核心特性剖析

1. 雙PLL通道與低抖動輸出

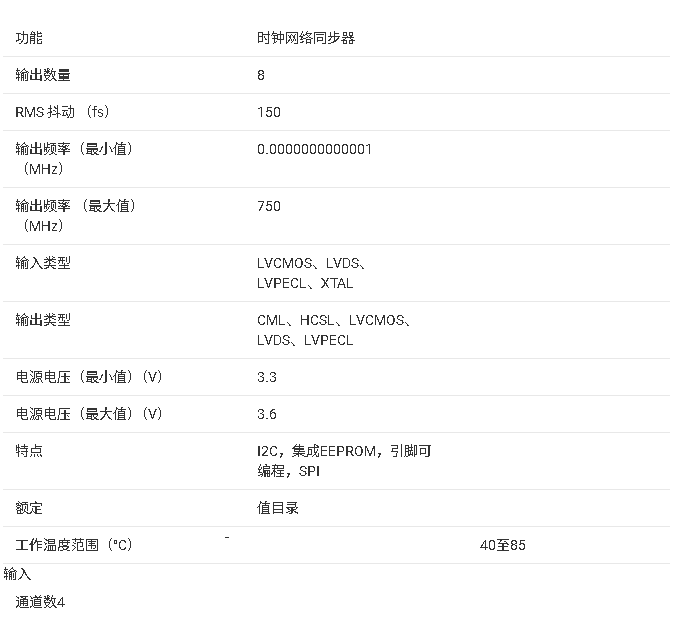

LMK05028具備兩個獨立的PLL通道,這為其帶來了強大的靈活性和高性能。它能夠產生多達八個輸出時鐘,典型的RMS相位抖動僅為150 - fs,如此低的抖動特性對于高速串行鏈路來說至關重要,能夠有效降低誤碼率(BER)。例如在一些對信號質量要求極高的通信系統中,低抖動的時鐘輸出可以確保數據的準確傳輸,減少信號失真。

2. 可編程特性

它擁有可編程的環路帶寬,這意味著我們可以根據不同的應用場景,對輸入抖動和漂移進行有效衰減。同時,分數 - N PLL頻率合成功能更是強大,能夠從任何輸入頻率生成任意輸出頻率,滿足多樣化的頻率配置需求。就好比在一個復雜的通信網絡中,不同的設備可能需要不同的時鐘頻率,LMK05028就能輕松應對這種多樣化的需求。

3. 精準的輸入選擇與切換

參考輸入多路復用器支持自動或手動輸入選擇,并且在參考切換時能夠實現無擾動切換,典型的相位瞬變僅為50 - ps。這種特性在網絡中時鐘源切換時非常關鍵,能夠確保輸出時鐘的穩定性,避免因切換帶來的信號干擾。例如在一些對時鐘穩定性要求極高的測試測量設備中,無擾動切換可以保證測量結果的準確性。

4. 豐富的輸出配置

該設備有八個輸出,其驅動可編程,支持多達八個差分時鐘、八個LVCMOS對(每對兩個輸出)或兩者的組合。輸出時鐘可以從PLL / VCO域中選擇,還支持1PPS(1Hz)輸出。在實際應用中,這種豐富的輸出配置可以滿足不同設備對時鐘信號的需求,提高了設備的通用性。

5. 時鐘監控與狀態反饋

LMK05028配備了先進的時鐘監控功能,能夠實時監測時鐘輸入和PLL的狀態。通過狀態引腳和中斷寄存器,我們可以獲取詳細的狀態信息,便于進行故障診斷和系統調試。比如在一個復雜的通信系統中,當出現時鐘故障時,我們可以通過狀態信息快速定位問題所在,提高系統的可靠性和維護效率。

6. 出色的電源抑制能力

它具有良好的電源抑制比(PSNR),能夠有效減少電源噪聲對時鐘信號的影響。內部LDO穩壓器的使用,進一步提高了電源的穩定性,降低了電源噪聲引起的抖動和雜散。在一些對電源噪聲敏感的設備中,如醫療成像設備,這種出色的電源抑制能力可以確保圖像的清晰和準確。

二、PLL架構與工作模式

1. PLL架構詳解

每個PLL通道由兩個數字PLL(DPLLs)和一個模擬PLL(APLL)以及一個低噪聲集成VCO組成。這種架構為時鐘性能的優化提供了基礎,不同的PLL在整個時鐘系統中發揮著不同的作用。例如,APLL主要負責對VCO頻率進行精確控制,而DPLL則用于對輸入時鐘進行相位和頻率的鎖定。

2. 工作模式選擇

LMK05028支持多種工作模式,如2 - 環REF - DPLL、3 - 環模式等。不同的模式適用于不同的應用場景,能夠在時鐘功能和性能之間進行平衡。

- 3 - 環模式:適合需要標準合規的頻率穩定性和低環路帶寬的應用,如SyncE、SONET / SDH等。在這種模式下,TCXO / OCXO源決定了自由運行和保持模式下的頻率穩定性和準確性,XO源則決定了輸出相位噪聲和抖動性能。例如在一些電信網絡中,3 - 環模式可以確保時鐘信號的穩定性和準確性,滿足網絡同步的要求。

- 2 - 環REF - DPLL模式:對于那些不需要在保持模式下具備高頻率穩定性以及不需要TCXO / OCXO成本的應用來說是一個不錯的選擇。它支持更高的環路帶寬,適用于一些對時鐘帶寬要求較高的設備,如某些測試儀器。

三、關鍵輸入輸出接口分析

1. 參考輸入

參考輸入(IN0 - IN3)可以接受差分或單端時鐘信號,每個輸入都有可編程的輸入類型、終端和交流耦合輸入偏置配置。這種靈活性使得它能夠適應不同類型的時鐘源,提高了設備的兼容性。例如在一些復雜的網絡環境中,可能存在多種不同類型的時鐘信號,LMK05028可以通過靈活的輸入配置來接收這些信號。

2. XO輸入

XO輸入作為分數 - N APLLs的參考時鐘,對輸出時鐘的抖動和相位噪聲性能有著重要影響。為了獲得最佳性能,XO頻率至少應為48 MHz,并且與VCO頻率具有非整數頻率關系,以使APLLs工作在分數模式下。在實際應用中,我們需要根據具體的性能要求來選擇合適的XO頻率和信號類型。

3. TCXO / OCXO輸入

TCXO輸入是TCXO - DPLL環路的參考時鐘,它決定了DPLL鎖定時的近場相位噪聲和漂移性能,以及自由運行和保持模式下的頻率準確性和穩定性。在一些對時鐘穩定性要求極高的應用中,如同步以太網(SyncE),TCXO輸入可以確保時鐘信號的頻率穩定性和準確性。

4. 時鐘輸出

輸出時鐘可以配置為差分驅動(AC - LVDS / CML / LVPECL)、HCSL驅動或LVCMOS驅動(1.8 V或2.5 V),每個輸出還可以單獨關閉。這種多樣化的輸出配置可以滿足不同設備對時鐘信號的要求,提高了設備的通用性。例如在一個包含多種不同類型設備的系統中,不同的設備可能需要不同類型的時鐘信號,LMK05028的多樣化輸出配置就可以很好地滿足這種需求。

四、實際應用場景與設計要點

1. 應用場景廣泛

LMK05028適用于多種應用場景,如SyncE(G.8262)、SONET / SDH(Stratum 3 / 3E,G.813,GR - 1244,GR - 253)、IEEE 1588 PTP從時鐘、光傳輸網絡(G.709)等。在這些應用中,它能夠提供穩定、低抖動的時鐘信號,確保系統的正常運行。例如在一些電信網絡中,SyncE協議對時鐘的穩定性和準確性要求極高,LMK05028可以很好地滿足這種要求,保證網絡的同步和數據的準確傳輸。

2. 設計要點

在實際設計中,我們需要考慮多個方面的因素。

- 電源設計:所有VDD核心電源必須由相同的3.3 - V電源軌供電,而各個輸出電源可以由單獨的1.8 - V、2.5 - V或3.3 - V電源軌供電。這種靈活的電源架構可以根據具體的應用需求進行優化,例如在一些對功耗要求較高的設備中,可以選擇較低電壓的輸出電源來降低功耗。

- 時鐘輸入與輸出接口設計:要根據實際的時鐘源和負載要求,合理選擇輸入和輸出接口的配置。例如在連接不同類型的時鐘源時,需要根據時鐘源的信號類型和特性來選擇合適的輸入接口配置;在連接負載時,需要根據負載對時鐘信號的要求來選擇合適的輸出接口配置。

- 監控與狀態反饋設計:充分利用設備的時鐘監控和狀態反饋功能,及時發現和解決問題。可以通過狀態引腳和中斷寄存器來獲取設備的狀態信息,進行故障診斷和系統調試。例如在一個復雜的系統中,可以通過監控狀態信息來及時發現時鐘故障,并采取相應的措施進行修復。

五、編程與配置

1. 編程接口

系統主機設備(MCU或FPGA)可以使用I2C或SPI來訪問寄存器、SRAM和EEPROM映射。這種雙接口的設計提供了更多的選擇靈活性,方便我們根據實際的系統架構和需求來選擇合適的編程接口。例如在一些對通信速度要求較高的系統中,可以選擇SPI接口進行編程;在一些對通信穩定性要求較高的系統中,可以選擇I2C接口進行編程。

2. 配置流程

通過TICS Pro編程軟件,我們可以根據所需的頻率計劃配置和PLL模式生成有效的分頻器設置。在實際配置過程中,需要按照一定的步驟進行操作,確保設備的正常運行。例如在進行寄存器配置時,需要按照寄存器的地址順序進行寫入操作,并且要注意一些特殊寄存器的配置要求。

六、總結

LMK05028憑借其低抖動、可編程性、出色的切換性能和豐富的功能,成為通信基礎設施和工業應用中網絡同步時鐘的理想選擇。在實際設計中,我們需要充分了解其特性和工作原理,根據具體的應用需求進行合理的配置和設計,以發揮其最大的性能優勢。希望通過本文的介紹,能讓大家對LMK05028有更深入的了解,在實際項目中能夠更好地應用這款優秀的設備。大家在使用過程中如果遇到什么問題,或者有什么獨特的應用經驗,歡迎在評論區留言分享。

-

通信應用

+關注

關注

0文章

20瀏覽量

8388

發布評論請先 登錄

具有EEPROM的LMK05028低抖動雙通道網絡同步器時鐘數據表

LMK05028:高性能網絡同步時鐘的卓越之選

LMK05028:高性能網絡同步時鐘的卓越之選

評論