德州儀器PGA4311:高性能4通道音頻音量控制芯片詳解

在音頻設備的設計中,音量控制是一個關鍵環節,它直接影響著音頻的質量和用戶體驗。德州儀器的PGA4311作為一款高性能的4通道音頻音量控制芯片,為專業和高端消費音頻系統提供了出色的解決方案。今天,我們就來深入了解一下這款芯片。

文件下載:pga4311.pdf

一、芯片概述

PGA4311采用亞微米CMOS工藝制造,適用于各種專業和消費音頻設備,如音頻放大器、混音臺、多軌錄音機、廣播 studio設備、樂器、效果處理器、A/V接收器和汽車音頻系統等。它的核心由電阻網絡、模擬開關陣列和高性能運算放大器級組成,通過開關選擇電阻網絡的抽頭來確定放大器級的增益,開關選擇由串行控制端口編程實現。

二、主要特性

(一)數字控制模擬音量

- 四獨立音頻通道:每個通道都能獨立控制音量,為多聲道音頻系統提供了極大的靈活性。

- 串行控制接口:采用3線串行控制接口,可連接各種主機控制器,還支持多個PGA4311設備的菊花鏈連接,減少了控制信號的數量。

- 零交叉檢測:通過ZCEN輸入啟用或禁用該功能,在輸入信號的零交叉點改變增益設置,可實現無噪聲電平轉換,最小化可聽干擾。

- 靜音功能:支持硬件和軟件控制靜音。硬件靜音通過MUTE輸入實現,軟件靜音則通過向音量控制寄存器加載全零來實現,且靜音時會進行內部失調校準,消除可聽的“咔嗒”聲或“噗噗”聲。

(二)寬增益和衰減范圍

增益范圍為 +31.5dB 至 -95.5dB,步長為 0.5dB,能滿足各種音頻應用對音量調節的需求。

(三)低噪聲和失真

- 動態范圍:高達120dB,能提供清晰、純凈的音頻信號。

- 總諧波失真加噪聲(THD+N):在1kHz時,U級為0.0004%,A級為0.0002%,保證了高音質。

(四)低通道間串擾

通道間串擾低至 -130dBFS,確保各通道之間的信號干擾極小。

(五)電源要求

模擬電源為 ±5V,數字電源為 +5V。

(六)封裝形式

采用SOP - 28封裝,便于電路板布局和焊接。

三、電氣特性

(一)直流特性

- 步長:固定為0.5dB。

- 增益誤差:在增益設置為31.5dB時,誤差為 ±0.05dB。

- 增益匹配:誤差為 ±0.05dB,保證各通道增益的一致性。

- 輸入電阻和電容:輸入電阻為10kΩ,輸入電容為3pF。

(二)交流特性

- THD+N:在輸入電壓為2Vrms、頻率為1kHz時,U級為0.0004%,A級為0.0002%。

- 動態范圍:在輸入接地、增益為0dB時,為116 - 120dB。

- 輸出電壓范圍:輸入無削波時,輸出電壓范圍為2.5Vrms。

- 輸出噪聲:在輸入接地、增益為0dB時,為2.5 - 4Vrms。

- 通道間串擾:在1kHz時為 -130dBFS。

(三)輸出緩沖器特性

- 失調電壓:在輸入接地、增益為0dB時,為0.25 - 0.5mV。

- 負載電容穩定性:能穩定驅動100pF的負載電容。

- 短路電流:為50mA。

- 小信號單位增益帶寬:為10MHz。

(四)數字特性

- 高電平輸入電壓(VIH):為 +2.0V 至 VD+。

- 低電平輸入電壓(VIL):為 -0.3V 至 0.8V。

- 高電平輸出電壓(VOH):在輸出電流為200μA時,為1.0 - 0.4V。

- 低電平輸出電壓(VOL):在輸出電流為 -3.2mA時,為0.4 - 1.0V。

(五)開關特性

- 串行時鐘(SCLK)頻率:范圍為0 - 6.25MHz。

- 串行時鐘(SCLK)脈沖寬度:低電平為80ns,高電平為80ns。

- MUTE脈沖寬度:低電平為2.0ms。

(六)輸入輸出時序

輸入和輸出時序有嚴格的要求,例如SDI設置時間和保持時間為20ns,CS下降到SCLK上升為90ns等。

(七)電源特性

- 工作電壓:模擬電源VA+為 +4.75 - +5.25V,VA - 為 -4.75 - -5.25V;數字電源VD+為 +4.75 - +5.25V。

- 靜態電流:VA+為17 - 22mA,VA - 為19 - 24mA,VD+為0.5 - 1.0mA。

- 電源抑制比(PSRR):在250Hz時為100dB。

四、引腳配置與功能

PGA4311共有28個引腳,包括模擬輸入輸出引腳、電源引腳、數字控制引腳和接地引腳等。以下是部分重要引腳的功能:

- MUTE:靜音控制輸入,低電平有效。

- AIN_x:各通道的模擬輸入引腳。

- AOUT_x:各通道的模擬輸出引腳。

- VA+和VA - :模擬電源引腳,分別為 +5V和 -5V。

- VD+:數字電源引腳,為 +5V。

- SDI:串行數據輸入引腳。

- CS:芯片選擇輸入引腳,低電平時可寫入數據。

- SCLK:串行時鐘輸入引腳,數據在其上升沿時鐘輸入。

- SDO:串行數據輸出引腳,用于菊花鏈連接,在SCLK下降沿輸出數據,CS為高電平時呈高阻態。

- ZCEN:零交叉使能引腳,高電平啟用零交叉檢測。

五、典型特性曲線

文檔中給出了在 (T{A}=+25^{circ}C) 、 (V{A^{+}}=+5V) 、 (V{A^{-}}=-5V) 、 (V{D^{+}}=+5V) 、 (R{L}=100kΩ) 、 (C{L}=20pF) 、帶寬測量范圍為10Hz至20kHz條件下的典型特性曲線,包括幅值與頻率、THD+N與幅值、THD+N與頻率、串擾與頻率等關系曲線,這些曲線有助于工程師更好地了解芯片在不同工作條件下的性能。

六、操作說明

(一)上電狀態

上電時,會激活約100ms的“上電復位”,期間電路處于硬件靜音狀態,所有內部觸發器復位。之后進行失調校準,完成后所有通道的增益字節值設置為 (00HEX) ,即軟件靜音狀態,直到主機控制器通過串行控制端口為每個通道設置新的增益。如果在正常運行時電源電壓降至 ±3.2V以下,電路將進入硬件靜音狀態;當電源電壓恢復到 ±3.2V以上時,將重新啟動上電序列。

(二)模擬輸入輸出

芯片有四個獨立通道,每個通道有對應的輸入和輸出引腳,輸入和輸出引腳為不平衡式,參考模擬地。輸入和輸出引腳的電壓擺動范圍在模擬電源 (V{A+}) 和 (V{A^{-}}) 的1.25V以內,在 (V{A^{+}}=+5V) 和 (V{A^{-}}=-5V) 時,最大輸入或輸出電壓范圍為7.5Vp - p。為獲得最佳性能,建議使用低源阻抗(600Ω或更低)驅動芯片,源阻抗高達2kΩ時,THD+N的劣化最小。

(三)串行控制端口

通過串行控制端口可對PGA4311的增益設置進行編程。控制數據以32位字的形式在SDI引腳輸入,每個通道的增益設置為8位。數據采用MSB優先的直二進制編碼,在SCLK的上升沿時鐘輸入到SDI。SDO用于菊花鏈連接,數據在SCLK的下降沿出現在該引腳。

(四)增益設置

每個通道的增益由對應的8位代碼 [7:0] 設置,代碼為直二進制格式。當 (N = 0) 時為靜音狀態;當 (N = 1) 到255時,增益計算公式為 (Gain(dB)=31.5 - [0.5times(255 - N)]) ,增益范圍為 +31.5dB( (N = 255) )至 -95.5dB( (N = 1) )。增益設置的更改可以選擇是否進行零交叉檢測。

(五)菊花鏈連接

為減少控制信號數量,支持多個PGA4311設備的菊花鏈連接。將前一個設備的SDO引腳連接到下一個設備的SDI輸入,形成一個大的移位寄存器。 (overline{CS}) 輸入必須在32 ? N個SCLK周期內保持低電平,N為鏈中設備的數量,以確保有足夠的時鐘周期加載所有設備。

(六)零交叉檢測

通過ZCEN引腳啟用或禁用零交叉檢測功能。當增益設置改變時,直到檢測到正斜率零交叉或16ms超時后,新的增益設置才會生效。超時情況下,新增益設置將直接生效,不嘗試最小化可聽偽影。

(七)靜音功能

支持硬件和軟件靜音。硬件靜音通過MUTE輸入實現,會斷開內部緩沖放大器與輸出引腳的連接,并用10kΩ電阻將輸出端接地;軟件靜音通過向音量控制寄存器加載全零實現,內部放大器設置為單位增益,放大器輸入連接到AGND。

七、應用設計建議

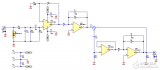

(一)推薦連接圖

建議在設計時將電源旁路電容盡可能靠近PGA4311封裝放置,以減少電源噪聲對芯片的影響。

(二)PCB布局指南

PCB的數字和模擬部分的接地平面應分開,并在單點連接,以避免數字信號對模擬信號的干擾。

八、封裝與訂購信息

PGA4311有U級和A級可選,封裝為SOP - 28(DW),提供多種包裝形式,如TUBE和Tape and Reel,適用于不同的生產需求。

德州儀器的PGA4311以其出色的性能和豐富的功能,為音頻工程師提供了一個可靠的音量控制解決方案。在實際應用中,工程師們需要根據具體的設計需求,合理配置芯片的各項參數,并注意PCB布局和電源管理等方面,以充分發揮其優勢,實現高質量的音頻系統設計。你在使用類似音頻控制芯片時遇到過哪些問題呢?歡迎在評論區分享你的經驗和想法。

-

德州儀器

+關注

關注

123文章

1970瀏覽量

145123

發布評論請先 登錄

用于專業音頻的有源音量控制

音量控制器和對數電位計

用于專業音頻的雙電源高性能音量控制驗證設計

6通道電子音量控制器ICPT2258電子資料

4W帶直流音量控制音頻功率放大電路

PGA4311,pdf(4-Channel Audio Vo

PGA4311 4 通道 +/-5V 音頻音量控制

德州儀器PGA4311:高性能4通道音頻音量控制芯片詳解

德州儀器PGA4311:高性能4通道音頻音量控制芯片詳解

評論