德州儀器TPA5050:立體聲數字音頻唇音同步延遲芯片解析

在音頻處理領域,實現音頻與視頻的完美同步是一個關鍵挑戰。德州儀器(TI)的TPA5050芯片為解決這一問題提供了有效的解決方案。今天,我們就來詳細探討一下這款芯片的特點、應用及相關技術細節。

文件下載:tpa5050.pdf

芯片概述

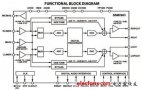

TPA5050是一款支持I2C控制的立體聲數字音頻唇音同步延遲芯片。它能夠接收單路串行音頻輸入,將數據緩沖一段可選擇的時間,然后通過單路串行輸出輸出延遲后的音頻數據。該芯片支持16 - 24位I2S、右對齊、左對齊等數字音頻格式,為音頻處理提供了豐富的選擇。

芯片特性

音頻格式與控制

- 多種音頻格式支持:支持16 - 24位I2S、右對齊、左對齊等數字音頻格式,滿足不同音頻系統的需求。

- I2C總線控制:通過I2C總線進行控制,方便與其他設備進行通信和配置。

- 單串行輸入端口:采用單串行輸入端口,簡化了音頻輸入的連接方式。

延遲特性

- 延遲時間:在采樣頻率(fs = 48 kHz)時,每通道延遲時間可達170 ms,能夠有效解決音頻與視頻的同步問題。

- 延遲分辨率:延遲分辨率為一個樣本,確保了精確的音頻延遲控制。

- 延遲內存清除:在上電或延遲更改后,延遲內存會被清除,避免了錯誤數據的輸出。

- 工作電壓:采用3.3 V電源供電,I/O和I2C控制具有5 V容限,提高了芯片的兼容性。

- 時鐘支持:支持32 - 64倍采樣頻率的音頻位時鐘速率,采樣頻率范圍為32 kHz - 192 kHz。

- 內部時鐘生成:無需外部晶體或振蕩器,所有內部時鐘均由音頻時鐘生成,簡化了電路設計。

封裝形式

采用4mm × 4mm、16引腳的QFN封裝,體積小巧,適合高密度電路板設計。

應用領域

- 高清電視唇音同步延遲:在高清電視中,由于視頻處理算法的復雜性,音頻和視頻可能會出現不同步的情況。TPA5050可以對音頻進行延遲,使其與視頻同步,提高觀看體驗。

- 平板電視唇音同步延遲:與高清電視類似,平板電視也可能存在音頻和視頻不同步的問題,TPA5050可以有效解決這一問題。

- 家庭影院后置聲道效果:在家庭影院系統中,后置聲道的音頻需要與前置聲道和視頻同步。TPA5050可以對后置聲道的音頻進行延遲,實現更好的環繞聲效果。

- 無線揚聲器前置聲道同步:在無線揚聲器系統中,由于信號傳輸的延遲,前置聲道的音頻可能會與視頻不同步。TPA5050可以對前置聲道的音頻進行延遲,確保音頻和視頻的同步。

引腳說明

| TPA5050的引腳功能豐富,不同引腳承擔著不同的任務,如下表所示: |

名稱 |

引腳號 |

I/O |

描述 |

| ADD0 |

10 |

I |

I2C地址選擇引腳 - 最低有效位 |

| ADD1 |

11 |

I |

I2C地址選擇引腳 |

| ADD2 |

12 |

I |

I2C地址選擇引腳 - 最高有效位 |

| BCLK |

16 |

I |

串行輸入的音頻數據位時鐘輸入,5V容限輸入 |

| DATA |

2 |

I |

串行輸入的音頻串行數據輸入,5V容限輸入 |

| DATA_OUT |

15 |

O |

延遲后的音頻串行數據輸出 |

| GND |

5 - 9, 14 |

P |

接地 - 所有接地端子必須連接到GND以確保正常工作 |

| LRCLK |

1 |

I |

左右串行音頻采樣率時鐘 (fs),5V容限輸入 |

| SCL |

3 |

I |

I2C通信總線時鐘輸入,5V容限輸入 |

| SDA |

4 |

I/O |

I2C通信總線數據輸入,5V容限輸入 |

| VDD |

13 |

P |

電源接口 |

電氣參數

絕對最大額定值

| 在使用TPA5050時,需要注意其絕對最大額定值,以避免對芯片造成永久性損壞。 |

參數 |

條件 |

值 |

單位 |

| VDD 電源電壓 |

|

-0.3 至 3.6 |

V |

| VI 輸入電壓 |

DATA、LRCLK、BCLK、SCL、SDA |

-0.3 至 5.5 |

V |

| ADD[2:0] |

|

-0.3 至 VDD + 0.3 |

V |

| 連續總功耗 |

|

見功耗評級表 |

|

| TA 工作環境溫度范圍 |

|

-40 至 85 |

°C |

| TJ 工作結溫范圍 |

|

-40 至 125 |

°C |

| Tstg 存儲溫度范圍 |

|

-65 至 125 |

°C |

| 引腳溫度(距外殼1.6 mm,持續10秒) |

|

260 |

°C |

功耗評級

| 不同的工作溫度下,TPA5050的功耗評級也有所不同。 |

封裝 |

TA ≤ 25 °C 功率評級 |

降額因子 |

TA = 70 °C 功率評級 |

TA = 85 °C 功率評級 |

| RSA |

2.5 W |

25 mW/°C |

1.375 W |

1.0 W |

推薦工作條件

| 為了確保TPA5050的正常工作,建議在以下條件下使用。 |

參數 |

條件 |

最小值 |

最大值 |

單位 |

| VDD 電源電壓 |

|

3 |

3.6 |

V |

| VIH 高電平輸入電壓 |

DATA、LRCLK、BCLK、SCL、SDA、ADD[2:0] |

2 |

|

V |

| VIL 低電平輸入電壓 |

DATA、LRCLK、BCLK、SCL、SDA、ADD[2:0] |

|

0.8 |

V |

| TA 工作環境溫度 |

|

-40 |

85 |

°C |

直流特性

| 在(TA = 25^{circ}C),(VDD = 3V)的條件下,TPA5050的直流特性如下。 |

參數 |

測試條件 |

最小值 |

典型值 |

最大值 |

單位 |

| IDD 電源電流 |

VDD = 3.3 V,fs = 48 kHz,BCLK = 32 fs |

|

1.5 |

3 |

mA |

| IOH 高電平輸出電流 |

DATA OUT = 2.6V |

7 |

|

13 |

mA |

| IOL 低電平輸出電流 |

DATA OUT = 0.4V |

7 |

|

13 |

mA |

| IH 高電平輸入電流 |

DATA、LRCLK、BCLK、SCL、SDA,Vi = 5.5V,VDD = 3V |

|

|

20 |

μA |

| ADD[2:0],Vi = 3.6V,VDD = 3.6V |

|

|

5 |

μA |

| IL 低電平輸入電流 |

DATA、LRCLK、BCLK、SCL、SDA、ADD[2:0],Vi = 0V,VDD = 3.6V |

|

|

1 |

μA |

時序特性

I2C接口信號和串行音頻輸入端口的時序特性對于芯片的正常工作至關重要。

I2C接口信號時序

| 參數 |

測試條件 |

最小值 |

典型值 |

最大值 |

單位 |

| fSCL SCL頻率 |

無等待狀態 |

|

|

400 |

kHz |

| tw(H) SCL高電平脈沖持續時間 |

|

0.6 |

|

|

μs |

| tw(L) SCL低電平脈沖持續時間 |

|

1.3 |

|

|

μs |

| tsu1 SDA到SCL的建立時間 |

|

100 |

|

|

ns |

| th1 SCL到SDA的保持時間 |

|

10 |

|

|

ns |

| t(buf) 停止和起始條件之間的總線空閑時間 |

|

1.3 |

|

|

μs |

| tsu2 SCL到起始條件的建立時間 |

|

0.6 |

|

|

μs |

| th2 起始條件到SCL的保持時間 |

|

0.6 |

|

|

μs |

| tsu3 SCL到停止條件的建立時間 |

|

0.6 |

|

|

μs |

串行音頻輸入端口時序

| 參數 |

測試條件 |

最小值 |

典型值 |

最大值 |

單位 |

| fSCLKIN BCLK頻率(32 × fs、48 × fs、64 × fs) |

|

1.024 |

|

12.288 |

MHz |

| tsu1 LRCLK到BCLK上升沿的建立時間 |

|

10 |

|

|

ns |

| th1 LRCLK從BCLK上升沿的保持時間 |

|

10 |

|

|

ns |

| tsu2 DATA到BCLK上升沿的建立時間 |

|

10 |

|

|

ns |

| th2 DATA從BCLK上升沿的保持時間 |

|

10 |

|

|

ns |

| LRCLK頻率 |

|

32 |

48 |

192 |

kHz |

| BCLK占空比 |

|

|

50% |

|

|

| LRCLK占空比 |

|

|

50% |

|

|

| BCLK上升沿之間的LRCLK上升沿數 |

LRCLK占空比 = 50% |

32 |

|

64 |

BCLK邊沿 |

應用信息

音頻串行接口

TPA5050的音頻串行接口由3線同步串行端口組成,包括LRCLK、BCLK和DATA。BCLK是串行音頻位時鐘,用于將DATA上的串行數據時鐘輸入到音頻接口的串行移位寄存器中。串行數據在BCLK的上升沿時鐘輸入到TPA5050中。LRCLK是串行音頻左右字時鐘,用于將串行數據鎖存到串行音頻接口的內部寄存器中。LRCLK以采樣頻率fs工作,BCLK可以在右對齊、左對齊和I2S格式下以32 - 64倍采樣頻率工作。TPA5050的工作不需要系統時鐘。

音頻數據格式和時序

TPA5050支持行業標準的音頻數據格式,包括右對齊、I2S和左對齊。數據格式可以通過I2C接口和寄存器映射進行選擇。

I2C操作

I2C總線使用SDA(數據)和SCL(時鐘)兩個信號在系統中的集成電路之間進行通信。數據在總線上串行傳輸,每次傳輸一位。地址和數據以字節(8位)格式傳輸,最高有效位(MSB)先傳輸。每個字節傳輸后,接收設備會用一個確認位進行確認。每次傳輸操作從主設備在總線上驅動一個起始條件開始,到主設備在總線上驅動一個停止條件結束。總線在時鐘為高電平時使用數據端子(SDA)上的轉換來表示起始和停止條件。SDA上的高到低轉換表示起始,低到高轉換表示停止。正常的數據位轉換必須在時鐘周期的低電平時間內發生。

單字節和多字節傳輸

TPA5050的串行控制接口支持所有寄存器的單字節和多字節讀寫操作。在多字節讀取操作中,TPA5050會從指定的寄存器開始,每次響應一個字節的數據,只要主設備繼續用確認位響應。TPA5050支持順序I2C尋址。對于寫事務,如果發出一個寄存器地址,然后是該寄存器和所有后續寄存器的數據,則發生了順序I2C寫事務。對于I2C順序寫事務,發出的寄存器地址作為起始點,在發送停止或起始條件之前隨后傳輸的數據量決定了寫入的寄存器數量。

寄存器配置

| TPA5050有多個可通過I2C命令配置的寄存器,不同的寄存器承擔著不同的功能。 |

寄存器 |

寄存器名稱 |

字節數 |

內容 |

初始化值 |

| 0x01 |

控制寄存器 |

1 |

后續章節描述 |

00 |

| 0x02 |

右延遲高5位 |

1 |

后續章節描述 |

00 |

| 0x03 |

右延遲低8位 |

1 |

后續章節描述 |

00 |

| 0x04 |

左延遲高5位 |

1 |

后續章節描述 |

00 |

| 0x05 |

左延遲低8位 |

1 |

后續章節描述 |

00 |

| 0x06 |

幀延遲 |

1 |

后續章節描述 |

00 |

| 0x07 |

右對齊數據包長度 |

1 |

后續章節描述 |

00 |

| 0x08 |

完全更新 |

1 |

后續章節描述 |

00 |

控制寄存器(0x01)

| 控制寄存器允許用戶靜音特定的音頻通道,還可以指定數據類型(I2S、右對齊或左對齊)。 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

功能 |

| 0 |

0 |

X |

X |

X |

X |

– |

– |

左右聲道均激活 |

| 0 |

1 |

X |

X |

X |

X |

– |

– |

左聲道靜音 |

| 1 |

0 |

X |

X |

X |

X |

– |

– |

右聲道靜音 |

| 1 |

1 |

X |

X |

X |

X |

– |

– |

左右聲道均靜音 |

| – |

– |

X |

X |

X |

X |

0 |

0 |

I2S數據格式 |

| – |

– |

X |

X |

X |

X |

0 |

1 |

右對齊數據格式(見數據包長度寄存器0x07) |

| – |

– |

X |

X |

X |

X |

1 |

0 |

左對齊數據格式 |

| – |

– |

X |

X |

X |

X |

1 |

1 |

旁路模式 - 數據直接通過,無延遲 |

音頻延遲寄存器(0x02 - 0x05)

| 通過向高寄存器和低寄存器寫入總共13位(2字節傳輸),可以固定左右聲道的音頻延遲。多字節傳輸應從控制寄存器開始,然后寫入4個字節以填充與右/左聲道延遲相關的高寄存器和低寄存器。D0 - D12的十進制值等于要延遲的樣本數。TPA5050的最大延遲樣本數為8191,在48 kHz時相當于170.65 ms [8191 × (1/fs)]。 |

D12 |

D11 |

D10 - D2 |

D1 |

D0 |

功能 |

| 0 |

0 |

0 |

0 |

0 |

左右音頻無延遲輸出 |

| 0 |

0 |

0 |

0 |

1 |

左右音頻延遲1個樣本(1/fs = 延遲時間) |

| 1 |

1 |

1 |

1 |

1 |

左右音頻延遲8191個樣本(8191/fs = 延遲時間) |

幀延遲寄存器(0x06)

| 該寄存器可用于指定視頻幀的延遲,而不是音頻樣本的延遲。當最高有效位(MSB)設置為1時,音頻延遲寄存器(0x01 - 0x04)被旁路,幀延遲寄存器用于根據幀率(D6)、音頻采樣率(D5 - D3)和要延遲的幀數(D2 - D0)設置延遲。 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

功能 |

| 0 |

|

|

|

|

|

|

|

此寄存器設置被屏蔽,音頻延遲由左右音頻延遲寄存器設置決定 |

| 1 |

|

|

|

|

|

|

|

左右音頻延遲寄存器被屏蔽,延遲由此寄存器設置決定 |

德州儀器TPA5050:立體聲數字音頻唇音同步延遲芯片解析

德州儀器TPA5050:立體聲數字音頻唇音同步延遲芯片解析

評論