探索PCA9665/PCA9665A:Fm+并行總線到I2C總線控制器的深度解析

在電子設計領域,總線控制器扮演著至關重要的角色,它能夠實現(xiàn)不同類型總線之間的通信,為系統(tǒng)的集成和擴展提供了強大的支持。今天,我們將深入探討NXP公司的PCA9665/PCA9665A Fm+并行總線到I2C總線控制器,詳細分析其特點、功能、應用場景以及使用過程中的注意事項。

文件下載:PCA9665PW,118.pdf

一、產(chǎn)品概述

PCA9665/PCA9665A作為一款高性能的總線控制器,主要用于連接標準并行總線微控制器/微處理器和串行I2C總線,實現(xiàn)兩者之間的雙向通信。它具備主模式和從模式兩種工作模式,既可以作為發(fā)送器,也可以作為接收器。通過字節(jié)或緩沖模式,結合中斷或輪詢握手方式,實現(xiàn)與I2C總線的高效通信。此外,該控制器還能自動控制I2C總線的特定序列、協(xié)議、仲裁和時序,無需外部定時元件,大大簡化了設計過程。

(一)突出特性

- 高速傳輸:支持1 MHz的傳輸速度,能夠滿足大多數(shù)高速數(shù)據(jù)傳輸?shù)膽眯枨蟆?/li>

- 強大驅動:SCL/SDA引腳的驅動能力高達25 mA,確保信號的穩(wěn)定傳輸。

- 大容量緩沖:配備68字節(jié)的數(shù)據(jù)緩沖區(qū),可緩存更多的數(shù)據(jù),提高數(shù)據(jù)處理效率。

- 通用呼叫功能:支持I2C總線通用呼叫,方便系統(tǒng)進行全局控制。

- 軟件復位:可通過并行總線進行軟件復位,方便系統(tǒng)進行故障恢復和初始化。

- 寬電壓范圍:工作電源電壓范圍為2.3 V至3.6 V,具有較好的兼容性和靈活性。

- 高耐壓I/O:I/O引腳具有5 V耐壓能力,增強了系統(tǒng)的抗干擾能力。

- 多模式兼容:支持標準模式和快速模式I2C總線,并與SMBus兼容,可廣泛應用于各種系統(tǒng)中。

- 靜電保護:ESD保護能力超過2000 V HBM和1000 V CDM,有效保護芯片免受靜電損傷。

- 閂鎖保護:經(jīng)過JEDEC Standard JESD78測試,閂鎖電流超過100 mA,確保芯片在復雜環(huán)境下的穩(wěn)定性。

(二)封裝類型

PCA9665提供SO20、TSSOP20、HVQFN20三種封裝形式,而PCA9665A則采用TSSOP20封裝,用戶可以根據(jù)實際應用需求選擇合適的封裝。

二、功能詳解

(一)內(nèi)部振蕩器

PCA9665和PCA9665A內(nèi)部均集成了振蕩器,用于提供I2C總線的時序信號。PCA9665的典型振蕩器頻率為28.5 MHz,PCA9665A為32 MHz。當ENSIO位設置為‘1’后,振蕩器需要最多550 μs的啟動時間。

(二)寄存器配置

PCA9665/PCA9665A包含11個寄存器,用于配置設備的操作以及發(fā)送和接收串行數(shù)據(jù)。其中,4個寄存器可直接訪問,7個寄存器需通過設置寄存器指針間接訪問。

- 直接寄存器

- 狀態(tài)寄存器(I2CSTA):8位只讀寄存器,用于反映I2C總線的狀態(tài)。最低兩位始終為零,高六位包含狀態(tài)代碼,共有30種可能的狀態(tài)代碼。當I2CSTA為F8h時,表示處于空閑狀態(tài),無串行中斷請求;其他值對應不同的定義狀態(tài),進入這些狀態(tài)時會請求串行中斷。

- 間接指針寄存器(INDPTR):8位只寫寄存器,用于指向間接地址空間中的寄存器。通過設置該寄存器的值,可以選擇要訪問的間接寄存器。

- I2C總線數(shù)據(jù)寄存器(I2CDAT):8位讀寫寄存器,用于存儲要發(fā)送或剛剛接收的串行數(shù)據(jù)。在主模式下,還包含主設備要發(fā)送的從設備地址。

- 控制寄存器(I2CCON):8位讀寫寄存器,其中兩位受總線控制器硬件影響。SI位在請求串行中斷時置位,STO位在I2C總線上出現(xiàn)停止條件時清零。通過并行接口寫入該寄存器會自動清除SI位,觸發(fā)下一個時鐘脈沖。

- 間接數(shù)據(jù)字段訪問寄存器(INDIRECT):用于訪問間接地址空間中的寄存器。在讀寫之前,需要先將INDPTR寄存器設置為要訪問的間接寄存器的地址。

- 間接寄存器

- 字節(jié)計數(shù)寄存器(I2CCOUNT):8位讀寫寄存器,用于記錄主/從緩沖接收器模式下已存儲的字節(jié)數(shù),以及主/從緩沖發(fā)送器模式下要發(fā)送的字節(jié)數(shù)。最高位為最后一個字節(jié)控制位,僅在主/從緩沖接收器模式下有效。

- 自身地址寄存器(I2CADR):8位讀寫寄存器,存儲微控制器的自身從設備地址。在主模式下,該寄存器內(nèi)容未被使用;在從模式下,高七位為自身從設備地址,最低位決定是否識別通用呼叫地址。

- 時鐘速率寄存器(I2CSCLL和I2CSCLH):8位讀寫寄存器,用于定義PCA9665/PCA9665A作為總線主設備時的數(shù)據(jù)速率。實際頻率由tHIGH、tLOW、tr、tf和td值決定,可通過公式 (f{SCL}=frac{1}{T{osc}(I2CSCLL + I2CSCLH)+t{r}+t{f}+tupu5pf5}) 計算,其中 (T{osc}) 為內(nèi)部振蕩器周期。

- 超時寄存器(I2CTO):8位讀寫寄存器,用于確定SCL允許保持低電平的最長時間。當超過該時間時,I2C總線狀態(tài)機將被復位,或PCA9665/PCA9665A將對I2C總線發(fā)起強制操作。

- 并行軟件復位寄存器(I2CPRESET):8位只寫寄存器,通過連續(xù)寫入兩個特定字節(jié)(A5h和5Ah)來實現(xiàn)軟件復位。如果寫入序列不符合要求,則復位操作將被中止。

- I2C總線模式寄存器(I2CMODE):8位讀寫寄存器,包含控制位,用于在主模式下選擇合適的時序參數(shù)(AC[1:0])。根據(jù)AC[1:0]的值,可以選擇標準模式、快速模式、快速模式Plus或Turbo模式。

三、工作模式

(一)配置模式

PCA9665/PCA9665A支持字節(jié)模式和緩沖模式,可通過I2CCON寄存器中的MODE位進行選擇。

- 字節(jié)模式:一次只能執(zhí)行一個特定命令,執(zhí)行完后更新狀態(tài)寄存器。命令可以是啟動、停止、字節(jié)寫入、字節(jié)讀取等。

- 緩沖模式:可以在生成中斷和更新I2CSTA寄存器之前執(zhí)行多個指令。微控制器可以一次性請求多達68字節(jié)的傳輸序列,讓PCA9665/PCA9665A自動執(zhí)行,無需每次執(zhí)行單個命令時都訪問狀態(tài)寄存器和控制寄存器,提高了系統(tǒng)的運行效率。

(二)操作模式

PCA9665/PCA9665A共有四種操作模式,每種模式都可以在字節(jié)模式或緩沖模式下使用。

- 主發(fā)送器模式:主設備向從設備發(fā)送數(shù)據(jù)。在字節(jié)模式下,一次發(fā)送一個字節(jié);在緩沖模式下,可以一次發(fā)送多個字節(jié)。

- 主接收器模式:主設備從從設備接收數(shù)據(jù)。同樣,字節(jié)模式下一次接收一個字節(jié),緩沖模式下可以一次接收多個字節(jié)。

- 從接收器模式:從設備接收主設備發(fā)送的數(shù)據(jù)。

- 從發(fā)送器模式:從設備向主設備發(fā)送數(shù)據(jù)。

四、特殊情況處理

(一)同時重復啟動條件

當兩個主設備同時生成重復啟動條件時,PCA9665/PCA9665A會檢測到總線上的重復啟動條件,并將其作為自己的啟動條件,繼續(xù)發(fā)送從設備地址。

(二)仲裁丟失后的處理

在主發(fā)送器和主接收器模式下,仲裁可能會丟失。當出現(xiàn)38h、68h和B0h狀態(tài)時,表示仲裁丟失。如果I2CCON寄存器中的STA標志被設置,當總線再次空閑時,將自動發(fā)送啟動條件(狀態(tài)08h),重新開始串行傳輸。

(三)強制訪問I2C總線

在某些情況下,可能會出現(xiàn)總線掛起的問題,例如不受控制的源產(chǎn)生多余的啟動信號或屏蔽停止條件。此時,如果STA標志被設置,且在合理時間內(nèi)未獲得總線訪問權限,PCA9665/PCA9665A可以進行強制訪問。當總線空閑時間達到超時時間時,會發(fā)送啟動條件。

(四)I2C總線阻塞

如果SCL或SDA被不受控制的源拉低,會導致I2C總線掛起。當SCL被拉低且持續(xù)時間等于超時值時,PCA9665/PCA9665A會判定為總線錯誤,并進行相應處理。如果SDA被拉低,PCA9665/PCA9665A會發(fā)送九個時鐘脈沖,然后發(fā)送停止條件。如果SDA被釋放,則發(fā)送正常啟動條件,繼續(xù)串行傳輸;否則,判定為總線錯誤,加載70h到I2CSTA,生成中斷信號,并釋放SCL和SDA線。

(五)總線錯誤

當START或STOP條件出現(xiàn)在格式幀的非法位置時,會發(fā)生總線錯誤。PCA9665/PCA9665A檢測到總線錯誤后,會釋放SDA和SCL線,設置中斷標志,并將狀態(tài)寄存器加載為00h。此時,微控制器必須發(fā)送外部硬件或軟件復位信號來重置PCA9665/PCA9665A。

五、應用場景

(一)添加I2C總線端口

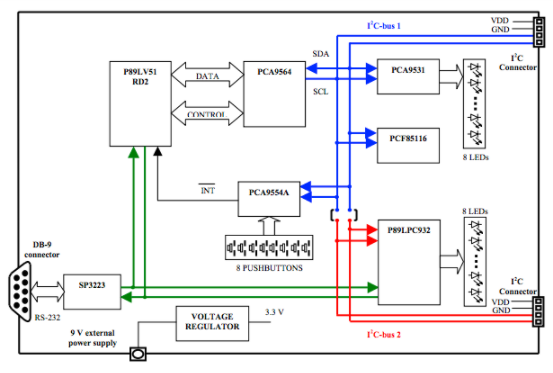

對于沒有集成I2C總線端口的微控制器、微處理器、自定義ASIC、DSP等設備,PCA9665/PCA9665A可以將8位并行數(shù)據(jù)轉換為支持多主設備的I2C總線端口,實現(xiàn)與I2C總線或SMBus組件的接口。

(二)添加額外I2C總線端口

當設備已經(jīng)有一個I2C總線端口,但需要更多端口來連接更多的I2C總線或SMBus組件時,PCA9665/PCA9665A可以將8位并行數(shù)據(jù)轉換為額外的I2C總線端口。

(三)并行數(shù)據(jù)轉串行數(shù)據(jù)

作為從發(fā)送器,PCA9665/PCA9665A可以將8位并行數(shù)據(jù)轉換為兩線I2C總線數(shù)據(jù)流,避免在印刷電路板上鋪設大量的并行線路,簡化了電路設計。

六、注意事項

(一)電源管理

在電源上電時,PCA9665/PCA9665A會進行內(nèi)部上電復位,直到VDD達到VPOR。上電初始化階段需要550 μs,在此期間,禁止通過并行端口寫入數(shù)據(jù),但可以讀取。

(二)復位操作

PCA9665/PCA9665A可以通過將RESET引腳拉低至少 (t_{w(rst)}) 或使用并行軟件復位序列進行復位。需要注意的是,復位操作只會重置內(nèi)部寄存器和控制邏輯,不會重新初始化內(nèi)部振蕩器。如果設備卡死且無法響應正常的復位信號,只能通過斷電再上電來恢復。

(三)I2CCOUNT寄存器

請求發(fā)送或接收的字節(jié)數(shù)應為1到68之間的值,否則將導致數(shù)據(jù)無法傳輸,并在寫入I2CCON寄存器后生成中斷。此時,I2CSTA狀態(tài)寄存器將加載FCh,表示請求加載到I2CCOUNT的值無效。

七、總結

PCA9665/PCA9665A Fm+并行總線到I2C總線控制器是一款功能強大、性能優(yōu)越的總線控制器,具有高速傳輸、大容量緩沖、多模式兼容等優(yōu)點,能夠滿足各種復雜的應用需求。在實際設計中,我們需要根據(jù)具體的應用場景,合理配置寄存器,選擇合適的工作模式,并注意處理各種特殊情況,以確保系統(tǒng)的穩(wěn)定運行。希望本文能夠為電子工程師們在使用PCA9665/PCA9665A時提供有益的參考。

-

總線通信

+關注

關注

0文章

65瀏覽量

12224

發(fā)布評論請先 登錄

探索PCA9665/PCA9665A:Fm+并行總線到I2C總線控制器的深度解析

探索PCA9665/PCA9665A:Fm+并行總線到I2C總線控制器的深度解析

評論