探索TLV320ADC3120:高性能音頻ADC的深度解析

在音頻信號處理領域,高性能的模數轉換器(ADC)是實現優秀音頻質量的關鍵。TI推出的TLV320ADC3120便是一款備受關注的器件,它集成了豐富的特性,為語音激活系統、專業麥克風、音頻會議等應用提供了強大的支持。今天,我們就來深入了解這款高性能的音頻ADC。

文件下載:tlv320adc3120.pdf

產品概述

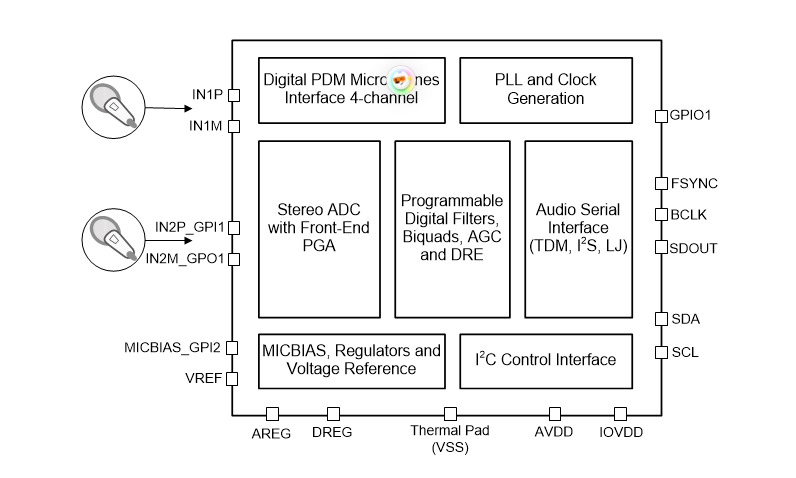

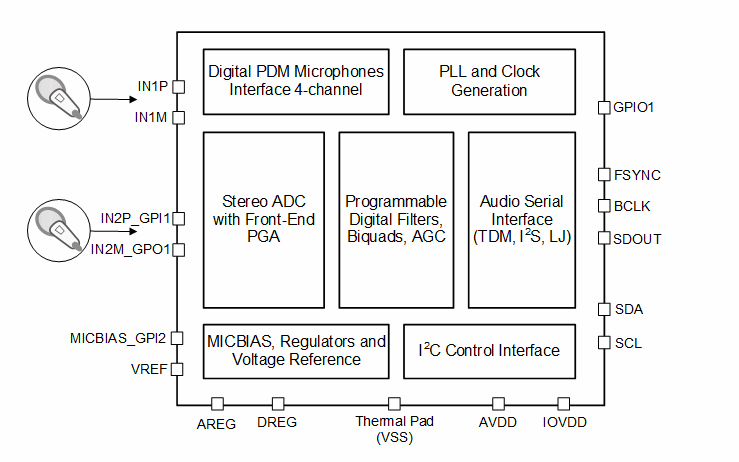

TLV320ADC3120是一款2通道的音頻ADC,具備高達768kHz的輸出采樣率。它支持最多兩個模擬麥克風或四個數字脈沖密度調制(PDM)麥克風的同時錄制,為多通道音頻采集應用提供了極大的靈活性。該器件還集成了眾多功能,如低噪聲可編程麥克風偏置輸出、自動增益控制器(AGC)、可編程抽取濾波器等,大大降低了成本、板空間和功耗,非常適合電池供電的空間受限應用。

核心特性剖析

1. 輸入通道配置

TLV320ADC3120擁有兩對模擬輸入引腳,可配置為差分輸入或單端輸入。對于模擬輸入,信號源可以是駐極體電容式模擬麥克風、微機電系統(MEMS)模擬麥克風或系統板的線路輸入。此外,它還支持數字PDM麥克風輸入,可通過重新配置引腳支持最多四個通道的數字麥克風錄制,甚至可以同時實現兩個模擬通道和兩個數字通道的錄制。 在選擇輸入源時,可通過寄存器進行配置,例如CH1_INSRC[1:0]寄存器位可用于選擇通道1的輸入源。同時,還可以根據輸入源的阻抗選擇合適的輸入阻抗,提供2.5kΩ、10kΩ和20kΩ三種選項,不過較高的輸入阻抗會帶來稍高的噪聲或較低的動態范圍。 在耦合方式上,語音或音頻信號輸入通常采用電容耦合(AC耦合),但該器件也支持直流耦合輸入以節省板空間。對于單端輸入配置,在直流耦合模式下,INxM引腳可直接接地;而在交流耦合模式下,INxM引腳必須在交流耦合電容之后接地。為了獲得最佳的動態范圍性能,建議使用差分交流耦合輸入。

2. 參考電壓與麥克風偏置

所有音頻數據轉換器都需要一個直流參考電壓,TLV320ADC3120通過內部帶隙電路生成低噪聲參考電壓,并具有高電源抑制比(PSRR)性能。該參考電壓通過VREF引腳輸出,需要使用至少1μF的電容連接到模擬地進行外部濾波。可通過P0_R59_D[1:0]寄存器位配置參考電壓的大小,以適應不同的滿量程輸入和AVDD電源電壓。 此外,該器件集成了低噪聲麥克風偏置引腳MICBIAS,可用于為駐極體電容式麥克風提供偏置或為MEMS模擬或數字麥克風供電。集成的偏置放大器支持高達5mA的負載電流,并且具有高PSRR、低噪聲和可編程偏置電壓等特點,可根據具體的麥克風組合進行微調。在使用MICBIAS引腳為多個麥克風提供偏置或供電時,應避免電路板布局上的公共阻抗,以減少麥克風之間的耦合。

3. 信號鏈處理

TLV320ADC3120的信號鏈由低噪聲、高性能、低功耗的模擬模塊和高度靈活的可編程數字處理模塊組成。前端可編程增益放大器(PGA)具有120dB的動態范圍,與低噪聲、低失真的多位Δ - Σ ADC相結合,能夠在安靜和嘈雜的環境中以非常高的保真度錄制遠場音頻信號。此外,ADC架構具有固有的抗混疊濾波功能,可有效抑制調制器頻率分量附近的帶外頻率噪聲,防止噪聲在ADC采樣期間混疊到音頻頻段。 在信號鏈的后續部分,集成的高性能多級數字抽取濾波器可大幅削減帶外頻率噪聲,具有高阻帶衰減能力。同時,該器件還集成了可編程雙二階濾波器,可實現自定義的低通、高通或其他所需的頻率整形,無需額外的外部抗混疊低通濾波組件,從而大大節省了外部系統組件成本和電路板空間。 信號鏈還包括各種高度可編程的數字處理模塊,如相位校準、增益校準、高通濾波器、數字求和器或混合器、雙二階濾波器和音量控制等。這些模塊可根據具體應用需求進行靈活配置,為音頻處理提供了豐富的功能。

4. 自動增益控制器(AGC)

AGC可自動調整通道增益,以保持輸出電平在一個相對穩定的范圍內。在語音錄制等應用中,當輸入信號過強或過弱時,AGC能夠自動調整增益,確保輸出信號的穩定性。例如,當一個人對著麥克風說話時,距離麥克風的遠近變化會導致輸入信號強度的變化,AGC可以自動適應這種變化,調整增益以保持輸出信號的穩定。 AGC算法具有多個可編程參數,包括目標電平、最大允許增益、攻擊和釋放(或衰減)時間常數以及噪聲閾值等。這些參數可以根據具體應用進行微調,以實現最佳的性能。例如,目標電平(AGC_LVL)可設置在 - 6dB至 - 36dB相對于滿量程信號的范圍內,默認值為 - 34dB,建議設置足夠的余量以防止在出現響亮聲音時發生削波。

5. 語音活動檢測(VAD)

在VAD模式下,TLV320ADC3120會持續監測一個輸入通道,以檢測是否有語音活動。該模式下,設備從AVDD電源汲取的靜態電流較低,非常適合對功耗敏感的應用。通過設置VAD_EN(P0_R117_D0)為1'b1可啟用該功能。當檢測到語音活動時,設備可以通過中斷提醒主機,或者根據I2C編程配置自動喚醒并開始錄制。該功能在模擬和數字麥克風接口上均得到支持,為了實現最低功耗的VAD,建議使用數字麥克風接口。可以通過設置VAD_CH_SEL(P1_R30_D[5:4])寄存器位來選擇用于VAD的輸入通道。

接口與通信

1. 串行接口

該器件具有控制和音頻數據兩個串行接口。控制串行接口用于設備配置,通過I2C通信可以訪問所有的配置寄存器和可編程系數。音頻數據串行接口則用于將音頻數據傳輸到主機設備,支持TDM、I2S或左對齊(LJ)協議格式,具有高度的靈活性。用戶可以通過ASI_FORMAT[1:0](P0_R7_D[7:6])寄存器位選擇總線協議格式,通過ASI_WLEN[1:0](P0_R7_D[5:4])寄存器位設置輸出通道數據字長,支持16位、20位、24位或32位。 在TDM模式下,FSYNC的上升沿啟動數據傳輸,從插槽0的數據開始,隨后依次傳輸其余插槽的數據。在I2S和LJ模式下,數據傳輸也有各自特定的時序要求。此外,該器件還支持通過設置可編程偏移來調整插槽數據傳輸的起始位置,以及反轉FSYNC和BCLK的極性,以滿足不同的系統需求。

2. 鎖相環(PLL)和時鐘生成

TLV320ADC3120具有智能自動配置模塊,可通過監測音頻總線上的FSYNC和BCLK信號頻率,自動生成ADC調制器和數字濾波器引擎所需的所有內部時鐘。該器件支持多種輸出數據采樣率和BCLK與FSYNC的比率,可自動配置所有時鐘分頻器,包括PLL配置,無需主機編程。通過監測狀態寄存器ASI_STS(P0_R21),可以捕獲設備對FSYNC頻率和BCLK與FSYNC比率的自動檢測結果。如果檢測到不支持的組合,設備會生成ASI時鐘錯誤中斷,并相應地靜音錄制通道。 此外,該器件還支持使用BCLK、GPIO1或GPIx引腳(作為MCLK)作為音頻時鐘源,而不使用PLL,以降低功耗。但需要注意的是,由于外部時鐘源的抖動,ADC性能可能會下降,并且如果外部音頻時鐘源頻率不夠高,某些處理功能可能無法得到支持。因此,對于高性能應用,建議使用PLL。

應用與設計要點

1. 典型應用案例

兩通道模擬麥克風錄制

在使用兩個模擬MEMS麥克風進行同時錄制的應用中,該器件可以通過I2C控制接口和TDM音頻數據從設備接口進行配置。為了獲得最佳的失真性能,建議使用具有低電壓系數的輸入交流耦合電容。在設計過程中,需要注意AVDD、AVDD電源電流消耗、IOVDD和最大MICBIAS電流等參數的設置。具體的配置步驟包括給設備上電、從睡眠模式轉換到活動模式、開始錄制、在需要時轉換回睡眠模式等,每個步驟都有相應的寄存器操作和時間等待要求。

四通道數字PDM麥克風錄制

當使用四個數字PDM MEMS麥克風進行同時錄制時,同樣可以通過I2C控制接口和TDM音頻數據從設備接口進行操作。在設計時,需要注意AVDD、AVDD電源電流消耗和IOVDD等參數。配置步驟包括給設備上電、從睡眠模式轉換到活動模式、配置通道輸入源和相關引腳功能、啟動錄制、在需要時轉換回睡眠模式等。

2. 電源供應建議

電源供應的順序在IOVDD和AVDD導軌之間可以任意安排,但在所有電源穩定后,才能啟動I2C事務來初始化設備。在電源上電和下電時,需要滿足一定的時間要求,例如上電時 (t{1}) 和 (t{2}) 至少為2 ms,下電時 (t{3}) 和 (t{4}) 至少為10 ms。同時,要確保電源的斜坡率小于1 V/μs,并且電源下電和上電事件之間的等待時間至少為100 ms。如果電源斜坡率小于0.1 V/ms,主機設備在進行任何設備配置之前,必須先進行軟件復位操作。在電源供應過程中,還需確保所有數字輸入引腳處于有效輸入電平,且在電源排序期間不發生切換。 該器件支持單AVDD電源操作,通過集成片上數字穩壓器DREG和模擬穩壓器AREG實現。如果系統中的AVDD電壓小于1.98 V,則應在板上短接AREG和AVDD引腳,并將AREG_SELECT位設置為1b'0(P0_R2的默認值),不啟用內部AREG。如果系統中使用的AVDD電源高于2.7 V,則主機設備在退出睡眠模式時可以將AREG_SELECT設置為1'b1,使設備內部調節器生成AREG電源。

3. 布局指導

合理的PCB布局對于實現設備的最佳性能至關重要。首先,應將散熱墊連接到地面,并使用過孔模式將設備正下方的散熱墊區域連接到接地層,以幫助散熱。電源的去耦電容應盡可能靠近設備引腳放置,并且建議使用低ESR的陶瓷電容。在PCB上,模擬差分音頻信號應進行差分布線,以提高抗噪聲能力,避免數字和模擬信號交叉,防止出現不必要的串擾。 設備的內部電壓參考需要使用外部電容進行濾波,因此應將濾波電容靠近VREF引腳放置,以獲得最佳性能。在為多個麥克風布線偏置或電源走線時,應直接連接MICBIAS引腳,避免公共阻抗,防止麥克風之間的耦合。同時,VREF和MICBIAS外部電容的接地端應直接短接到AVSS引腳,不使用任何過孔。此外,MICBIAS電容(具有低等效串聯電阻)應靠近設備放置,以減少走線阻抗。使用接地層可以為設備和去耦電容之間的電源和信號電流提供最低阻抗路徑,應將設備正下方的區域視為設備的中心接地區域,所有設備接地都應直接連接到該區域。

總結與展望

TLV320ADC3120以其豐富的功能、高靈活性和高性能,為音頻處理領域帶來了出色的解決方案。無論是在專業音頻錄制、語音激活系統還是其他音頻應用中,它都能夠展現出卓越的性能。對于電子工程師來說,深入了解該器件的特性、接口和應用要點,能夠更好地將其應用到實際項目中,實現高質量的音頻處理。在未來的音頻技術發展中,像TLV320ADC3120這樣的高性能器件將繼續推動音頻處理技術的不斷進步,為我們帶來更加優質的音頻體驗。

各位工程師朋友們,你們在使用類似音頻ADC的過程中遇到過哪些問題呢?你們又是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

音頻處理

+關注

關注

0文章

162瀏覽量

18294

發布評論請先 登錄

TLV320ADC6120高精度音頻ADC技術解析與應用

探索TLV320ADC3120:高性能音頻ADC的深度解析

探索TLV320ADC3120:高性能音頻ADC的深度解析

評論