探索PWD13F60:高集成度功率驅動的卓越之選

引言

在電子工程師的日常設計工作中,選擇一款合適的功率驅動芯片至關重要。它不僅關系到產品的性能和穩(wěn)定性,還會影響到設計的復雜度和成本。今天,我們就來深入探討一款高集成度的功率驅動芯片——PWD13F60,看看它能為我們的設計帶來哪些驚喜。

文件下載:pwd13f60.pdf

產品概述

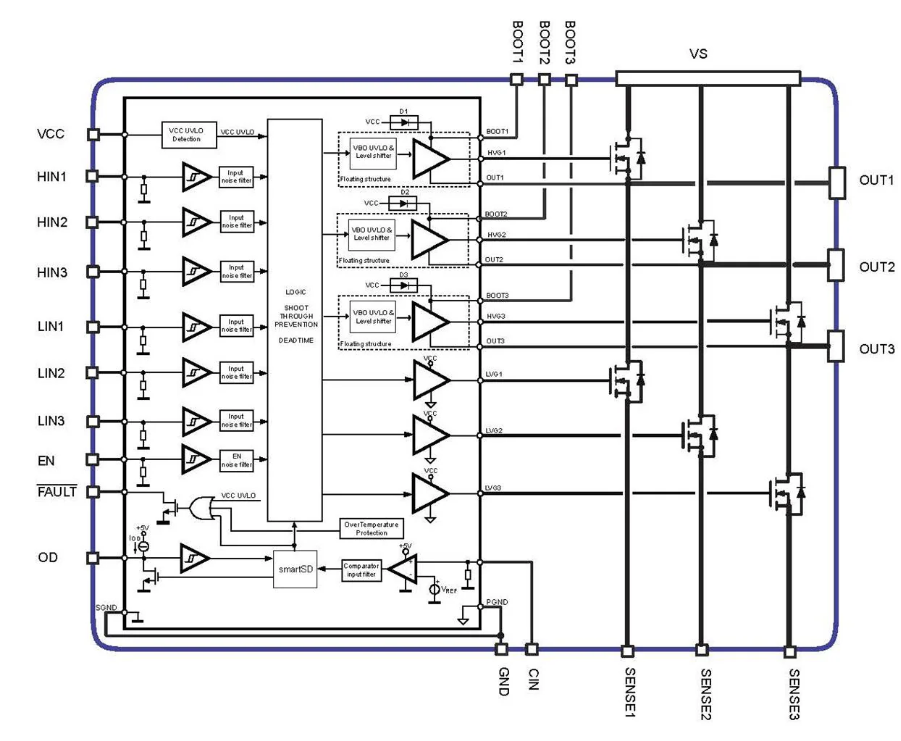

PWD13F60是一款高密度功率驅動芯片,它將柵極驅動器和四個N溝道功率MOSFET以雙半橋配置集成在一起。這種高度集成的設計使得該芯片能夠在極小的空間內高效地驅動負載,非常適合各種工業(yè)和家電應用。

產品特性

- 低導通電阻:集成的功率MOSFET具有低 (R_{DS(on)}) ,僅為320 mΩ,這意味著在導通狀態(tài)下能夠減少功率損耗,提高效率。

- 高耐壓能力:漏源擊穿電壓 (BV_{DSS}) 達到600 V,能夠承受較高的電壓,適用于多種高壓應用場景。

- 寬驅動電源電壓范圍:驅動電源電壓可低至6.5 V,并且具有欠壓鎖定(UVLO)保護功能,確保在電源電壓不穩(wěn)定時芯片的安全運行。

- 多種工作模式:可以作為全橋或雙獨立半橋工作,提供了靈活的設計選擇。

- 兼容輸入:3.3 V至15 V兼容輸入,具有遲滯和下拉功能,方便與微控制器、DSP單元或霍爾效應傳感器等接口。

- 互鎖功能:防止交叉導通,提高了系統(tǒng)的可靠性。

- 內部自舉二極管:嵌入式柵極驅動器的高端可以通過集成的自舉二極管輕松供電,簡化了設計。

- 輸出與輸入同相:使信號處理更加方便。

- 緊湊布局:采用緊湊的VFQFPN封裝,尺寸為10 x 13 x 1.0 mm,節(jié)省了電路板空間。

應用領域

PWD13F60的應用非常廣泛,包括但不限于以下領域:

- 工業(yè)和家電電機驅動器:為電機提供高效、穩(wěn)定的驅動。

- 工廠自動化:滿足自動化設備對功率驅動的需求。

- 風扇和泵:驅動風扇和泵的運轉。

- HID燈鎮(zhèn)流器:為高強度氣體放電燈提供合適的驅動。

- 電源單元:用于電源的轉換和控制。

- DC - DC和DC - AC轉換器:實現(xiàn)不同電壓和電流的轉換。

電氣特性分析

絕對最大額定值

了解芯片的絕對最大額定值對于確保芯片的安全使用至關重要。PWD13F60的絕對最大額定值包括:

- MOSFET漏源電壓: (V{DS}) 最大為600 V( (T{J}=25^{circ}C) )。

- 驅動器電源電壓: (V{CC1}) 和 (V{CC2}) 范圍為 -0.3至19 V。

- VCC至SENSE引腳電壓: (V_{CCx - SENSEx}) 范圍為 -0.3至19 V。

- 自舉電壓: (V_{BOOTx}) 范圍為GNDx - 0.3至600 V。

- BOOTx至OUTx引腳電壓: (V{BO1}) 和 (V{BO2}) 范圍為 -0.3至19 V。

- 漏極電流:每個MOSFET的直流漏極電流在 (T{CB}=25^{circ}C) 時最大為8 A,在 (T{CB}=100^{circ}C) 時為6.9 A,峰值電流在 (T_{CB}=25^{circ}C) 時可達32 A。

- 源 - 漏二極管電流:每個二極管的直流電流在 (T{CB}=25^{circ}C) 時最大為8 A,峰值電流在 (T{CB}=25^{circ}C) 時可達32 A。

- 全橋輸出壓擺率: (SR_{out}) 最大為40 V/ns。

- 邏輯輸入電壓范圍: (V_{i}) 范圍為 -0.3至15 V。

- 結溫: (T_{J}) 范圍為 -40至150 °C。

- 存儲溫度: (T_{s}) 范圍為 -40至150 °C。

- 總功率耗散:在 (T{CB}=25^{circ}C) 時每個MOSFET最大為450 W,在 (T{amb}=25^{circ}C) 、JEDEC板條件下為6.9 W。

推薦工作條件

為了使芯片能夠穩(wěn)定、可靠地工作,建議在以下條件下使用:

- 驅動器電源電壓: (V{CC1}) 和 (V{CC2}) 最低為6.5 V。

- BOOTx至OUTx引腳電壓: (V{BO1}) 和 (V{BO2}) 最低為6.5 V。

- 高壓電源:VS最大為480 V。

- 結溫: (T_{J}) 范圍為 -40至125 °C。

熱特性

熱特性對于功率驅動芯片的性能和可靠性有著重要影響。PWD13F60的熱特性參數(shù)如下:

- 結到每個MOSFET暴露焊盤的熱阻: (R_{th(J - CB)}) 典型值為1.1 °C/W。

- 結到環(huán)境的熱阻: (R_{th(J - A)}) 為18 °C/W(模擬芯片安裝在FR4 2s2p板上,功率均勻分布在四個功率MOSFET上)。

電氣特性詳細分析

驅動器部分

- 電源電壓遲滯: (V_{CC_hys}) 范圍為0.2至0.6 V,用于防止電源電壓波動引起的誤動作。

- 電源欠壓開啟閾值: (V_{CC_thON}) 范圍為5.7至6.5 V。

- 電源欠壓關閉閾值: (V_{CC_thOFF}) 范圍為5.3至6.1 V。

- 欠壓靜態(tài)電源電流: (I{qccu}) 在 (V{CC}=4.5 V) 時最大為190 μA。

- 靜態(tài)電流: (I_{qcc}) 在 (HINx = GND) 、 (LINx = 5 V) 時范圍為270至350 μA。

- 自舉電源靜態(tài)電流: (I{QBO}) 在 (V{BO}=15 V) 、 (LINx = GND) 、 (HINx = 5 V) 時范圍為60至97 μA。

- 自舉泄漏電流: (I{LK}) 在 (V{OUTx}=V_{BOOTx}=VS = 600 V) 、 (VCC = LINx = HINx = GND) 時最大為1 μA。

- 自舉驅動器導通電阻: (R_{BD(on)}) 在 (LIN = 5 V) 時典型值為120 Ω。

- 邏輯輸入閾值電壓:邏輯低電平閾值電壓 (V{il}) 范圍為0.80至1.10 V,邏輯高電平閾值電壓 (V{ih}) 范圍為1.90至2.30 V。

- 邏輯輸入偏置電流:邏輯 '1' 輸入偏置電流 (I{ih}) 在 (LINx = HINx = 15 V) 時范圍為30至65 μA,邏輯 '0' 輸入偏置電流 (I{il}) 在 (LINx = HINx = GND) 時最大為1 μA。

功率MOSFET部分

- 漏源擊穿電壓: (V{(BR)IDSS}) 在 (I{D}=1 mA) 時最小為600 V。

- 零柵壓漏極電流: (I{DSS}) 在 (V{DS}=600 V) 時最大為1 μA。

- 柵極閾值電壓: (V{GS(th)}) 在 (V{DS}=V{GS}) 、 (I{D}=250 μA) 時范圍為3至5 V。

- 靜態(tài)漏源導通電阻: (R{DS(on)}) 在 (I{D}=3 A) 、 (V_{GS}=10 V) 時典型值為0.32 Ω,最大為0.425 Ω。

- 雪崩電流: (I{AS}) 最大為3 A(脈沖寬度受 (T{J}) 最大值限制)。

- 單脈沖雪崩能量: (E{AS}) 在起始 (T{J}=25^{circ}C) 、 (I{D}=I{AS}) 、 (V_{DD}=50 V) 時最大為162 mJ。

- 源 - 漏二極管正向導通電壓: (V{SD}) 在 (LINx = GND) 、 (HINx = GND) 、 (I{SD}=3 A) 時范圍為0.8至1.25 V。

功能描述

邏輯輸入

| PWD13F60有四個邏輯輸入,用于獨立控制內部的高端和低端MOSFET。芯片提供了互鎖功能,避免同一通道內高端和低端MOSFET同時導通,確保系統(tǒng)的安全運行。邏輯輸入的真值表如下: | HINx | LINx | HSx | LSx |

|---|---|---|---|---|

| 0 | 0 | OFF | OFF | |

| 0 | 1 | OFF | ON | |

| 1 | 0 | ON | OFF | |

| 1 | 1 | OFF | OFF |

邏輯輸入還具有內部下拉電阻,當邏輯線路中斷或控制器輸出處于三態(tài)時,能夠將邏輯輸入拉低,使柵極驅動器輸出為低電平,相應的MOSFET關閉。

自舉結構

自舉電路通常用于為高壓部分供電。PWD13F60采用了專利的集成結構代替外部二極管,由低壓二極管和高壓DMOS串聯(lián)組成,與低端驅動器(LVG)同步驅動。內部自舉提供DMOS的驅動電壓,當?shù)投蓑寗悠鲗〞r,集成二極管結構主動導通,保證了最佳性能。在某些需要在低端驅動器關閉時對自舉電容充電的應用中,可以并聯(lián)一個外部自舉二極管。

Vcc電源引腳和UVLO功能

VCCx電源引腳為柵極驅動器的低端部分以及用于充電自舉電容的集成自舉二極管提供電流。在輸出換向期間,為高端和低端MOSFET提供柵極電荷的平均電流通過這些引腳。VCC1和VCC2分別為兩個驅動器供電,通常在最終應用中連接到同一電源。

芯片的電源電壓( (V{CCx}) )由欠壓鎖定(UVLO)電路持續(xù)監(jiān)控。當電源電壓低于 (V{CC_thOFF}) 閾值時,高端和低端MOSFET關閉;當電源電壓高于 (V{CC_thON}) 電壓時,根據(jù)LIN和HIN的狀態(tài)開啟MOSFET。為了抑制噪聲,提供了 (V{CC_hys}) 遲滯。兩個獨立的UVLO電路分別監(jiān)控 (V{CC1}) 和 (V{CC2}) ,當單個電源軌出現(xiàn)UVLO時,僅關閉相關半橋的MOSFET。

典型應用與布局建議

典型應用電路

PWD13F60的典型應用電路包括連接到控制器的邏輯輸入、電源引腳、自舉電容、負載以及用于過流保護的SENSE引腳等。通過合理配置這些元件,可以實現(xiàn)對負載的高效驅動。

布局建議

在PCB布局時,需要考慮以下幾點:

- 散熱:為了提高散熱效率,建議在EPAD1、EPAD2、EPAD5下方添加熱過孔,將芯片產生的熱量傳遞到其他PCB銅層。

- 布線:合理布線,減少信號干擾和噪聲。例如,將邏輯輸入線和電源線分開布線,避免相互干擾。

- 焊盤設計:參考ST提供的建議焊盤設計,確保芯片與PCB的良好連接。

總結

PWD13F60是一款功能強大、性能卓越的高集成度功率驅動芯片。它具有低導通電阻、高耐壓能力、寬驅動電源電壓范圍等優(yōu)點,適用于多種工業(yè)和家電應用。通過深入了解其電氣特性、功能描述和布局建議,電子工程師可以更好地利用這款芯片進行設計,提高產品的性能和可靠性。在實際應用中,你是否遇到過類似功率驅動芯片的設計挑戰(zhàn)呢?你又是如何解決的呢?歡迎在評論區(qū)分享你的經驗和見解。

-

電氣特性

+關注

關注

0文章

224瀏覽量

10300

發(fā)布評論請先 登錄

意法半導體推 PWD13F60 節(jié)省電路板空間60% 還能提升最終應用的功率密度

PWD5F60高密度片上系統(tǒng)電源驅動解決方案

PWD13F60 STMicroelectronics PWD13F60柵極驅動器

PWD5F60TR STMicroelectronics PWD5F60高密度功率驅動器

STMicroelectronics PWD5T60三相高密度功率驅動器深度解析與技術應用指南

探索PWD13F60:高集成度功率驅動的卓越之選

探索PWD13F60:高集成度功率驅動的卓越之選

評論