LMX1204:低噪聲、高頻JESD緩沖器/倍增器/分頻器的卓越之選

在電子設計領域,時鐘信號的精確性和穩定性對于系統性能至關重要。今天,我們要深入探討一款高性能的時鐘處理器件——LMX1204低噪聲、高頻JESD緩沖器/倍增器/分頻器,它在測試測量、航空航天與國防以及通用等多個領域都有著廣泛的應用前景。

文件下載:lmx1204.pdf

一、LMX1204的核心特性

1. 寬輸出頻率范圍

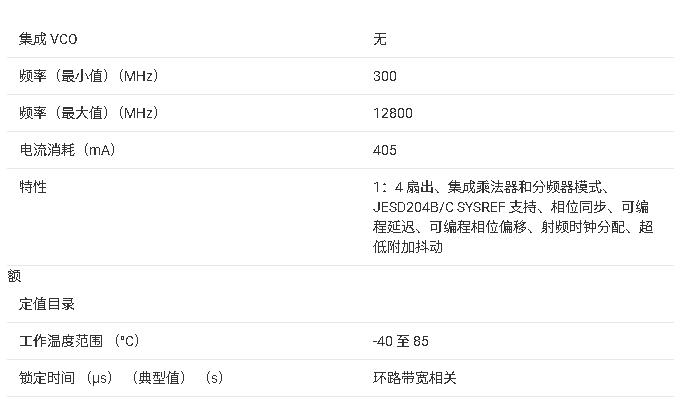

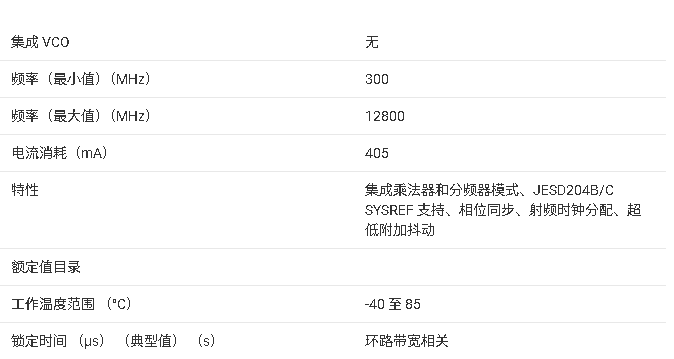

LMX1204的輸出頻率范圍為300MHz至12.8GHz,能夠滿足多種不同頻率需求的應用場景。無論是高頻的高速數據采集系統,還是較低頻率的FPGA時鐘驅動,它都能應對自如。

2. 超低噪聲表現

- 噪聲底限:在6GHz輸出時,噪聲底限低至 -161dBc/Hz,有效減少了信號中的噪聲干擾,提高了信號的純凈度。

- 1/f噪聲:在6GHz輸出、10kHz偏移時,1/f噪聲僅為 -154dBc/Hz,進一步優化了信號質量。

- 抖動性能:僅5fs的抖動(12kHz至20MHz)以及小于30fs的附加抖動(DC至fCLK),確保了時鐘信號的穩定性和準確性。

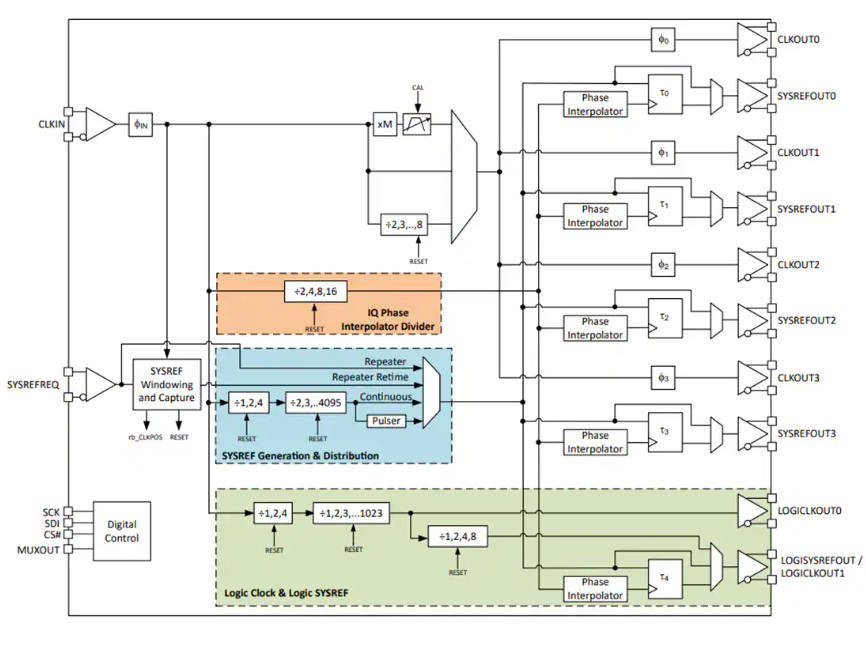

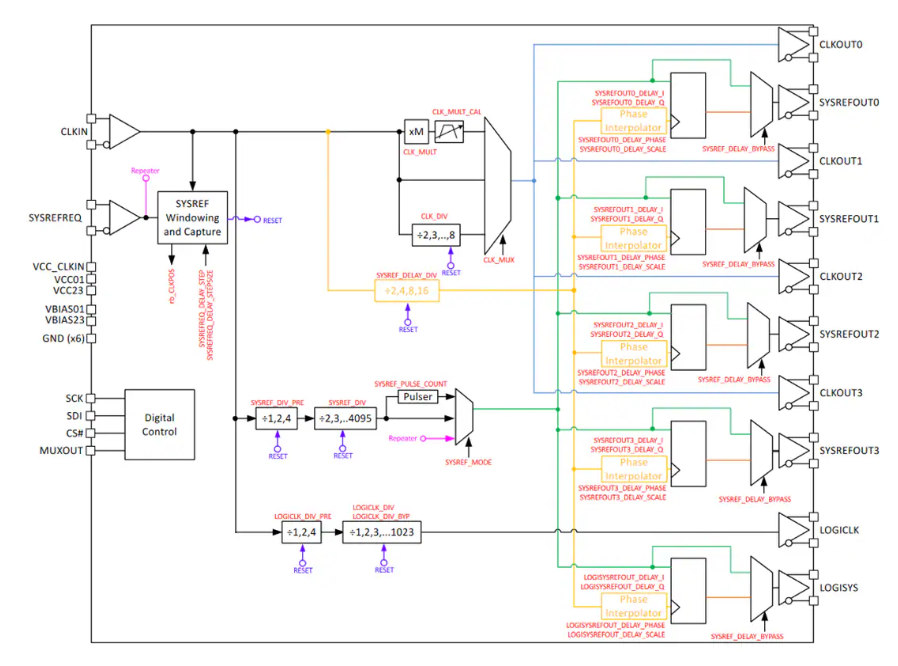

3. 豐富的時鐘輸出配置

- 4路高頻時鐘及SYSREF輸出:配備4路高頻時鐘輸出,且每路都有對應的SYSREF輸出。共享分頻器支持÷1(緩沖模式)、÷2、3、4、5、6、7和8,共享的基于PLL的倍增器支持x1(濾波模式)、x2、x3和x4。

- LOGICLK及SYSREF輸出:獨立的LOGICLK輸出及對應的SYSREF輸出,其預分頻器支持÷1、2、4,后分頻器支持÷1(旁路)、2至1023,為不同頻率需求的設備提供了靈活的時鐘解決方案。

4. 可調節輸出功率與同步功能

- 可編程輸出功率:具有8檔可編程輸出功率,可根據實際應用需求靈活調整時鐘輸出的功率大小。

- 同步SYSREF時鐘輸出:支持508個延遲步長調整,每個步長在12.8GHz時小于2.5ps。具備發生器和中繼器模式,以及SYSREFREQ引腳的窗口功能,可優化時序。

- 同步特性:支持對所有分頻器和多個設備進行同步,確保多個設備之間時鐘信號的一致性。

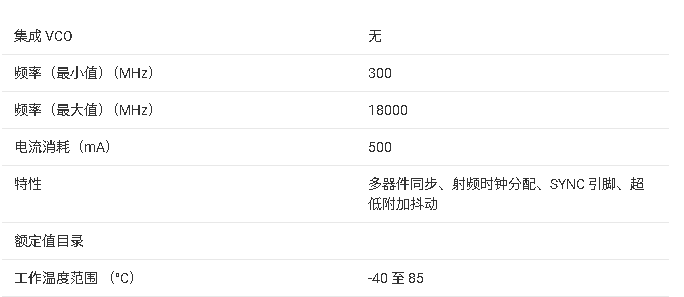

5. 工作條件與參數

- 工作電壓:采用2.5V工作電壓,降低了功耗,提高了系統的能效。

- 工作溫度范圍:工作溫度范圍為 -40oC至85oC,具備良好的環境適應性。

二、應用領域

1. 測試與測量

在示波器、無線設備測試儀和寬帶數字化儀等測試測量設備中,LMX1204的高性能時鐘輸出能夠確保精確的測量結果。其超低噪聲和低抖動特性可以有效減少測量誤差,提高設備的分辨率和精度。

2. 航空航天與國防

在雷達、電子戰、導引頭前端、彈藥以及相控陣天線/波束成形等領域,對時鐘信號的穩定性和抗干擾能力要求極高。LMX1204憑借其出色的性能,能夠在復雜的電磁環境下提供穩定可靠的時鐘信號,保障系統的正常運行。

3. 通用應用

在數據轉換器時鐘和時鐘緩沖器分配/分頻等通用應用中,LMX1204可以為數據轉換器提供精確的時鐘信號,確保數據轉換的準確性和穩定性。同時,其靈活的時鐘配置和同步功能,能夠滿足不同系統架構的需求。

三、詳細功能解析

1. 上電復位

上電時,器件的上電復位(POR)會將所有寄存器重置為默認狀態,并復位所有狀態機和分頻器。在POR狀態下,所有SYSREF輸出禁用,分頻器旁路,器件作為4路輸出緩沖器工作。建議在電源軌上電后等待100μs再對其他寄存器進行編程,以確保復位完成。同時,也可以通過在SPI總線上寫入RESET = 1來進行軟件上電復位,復位位在寫入其他寄存器后會自動清除。

2. 溫度傳感器

通過溫度傳感器可以讀取結溫,這有助于根據溫度變化進行調整,如調整CLKOUTx_PWR以穩定輸出功率,或使用外部或數字延遲補償傳播延遲的溫度變化。結溫與讀取代碼之間的關系為:Temperature = 0.65 × Code – 351,該公式基于對不同批次芯片的測試得出,實際溫度與預測溫度的最大偏差為13°C。

3. 時鐘輸出

- 時鐘輸出緩沖器:采用類似CML的集電極開路輸出結構,集成上拉電阻。通過CLKOUTx_EN位可啟用輸出緩沖器,CLKOUTx_PWR字段可單獨設置輸出功率。若要關閉整個通道,需禁用CHx_EN位。

- 時鐘MUX:4路主時鐘頻率可通過CLK_MUX字段選擇旁路、倍增或分頻。CLK_MUX有三種可選模式:緩沖模式(÷1)、分頻模式(÷2至÷8)和倍增模式(x1至x4)。

- 時鐘分頻器:將CLK_MUX設置為分頻模式后,可通過CLK_DIV字段設置分頻值。在使用時鐘分頻器時,輸入頻率的任何變化都需要將CLK_DIV_RST位從1切換到0。

- 時鐘倍增器和濾波模式

- 一般信息:時鐘倍增器可將輸入時鐘頻率乘以1、2、3或4倍,倍增值由CLK_MULT字段設置。由于倍增器基于PLL并集成了VCO,因此具有狀態機時鐘、校準功能和鎖定檢測功能,還可作為可調濾波器使用。

- 狀態機時鐘:狀態機時鐘頻率fSMCLK通過對輸入時鐘頻率進行編程分頻得到。在使用時鐘倍增器時,狀態機時鐘用于運行校準引擎和鎖定檢測,其頻率必須小于30MHz。若不使用時鐘倍增器,應將SMCLK_EN設置為0以減少串擾和雜散。

- 校準:為了獲得最佳相位噪聲性能,倍增器中的VCO將頻率范圍劃分為多個頻段和內核,并針對每個頻段進行優化的幅度設置。因此,在初次使用或頻率變化時,需要運行校準程序來確定正確的內核、頻段和幅度設置。校準時間與狀態機時鐘速度有關,狀態機時鐘頻率應至少為SPI寫入速度的兩倍,但不超過30MHz。

- 濾波模式:x1時鐘倍增器可作為可編程濾波器,用于衰減PLL環路帶寬(約10MHz)之外的噪聲、雜散、諧波和次諧波。與緩沖模式不同,濾波模式會對輸入頻率進行濾波,但會增加近相位噪聲。在頻率高于4.2GHz時,可能會出現Fref/3的次諧波,可通過輸出濾波器消除。

- 鎖定檢測:倍增器的鎖定狀態可通過rb_LD字段或MUXOUT引腳讀取。狀態機時鐘必須運行,鎖定檢測才能正常工作。

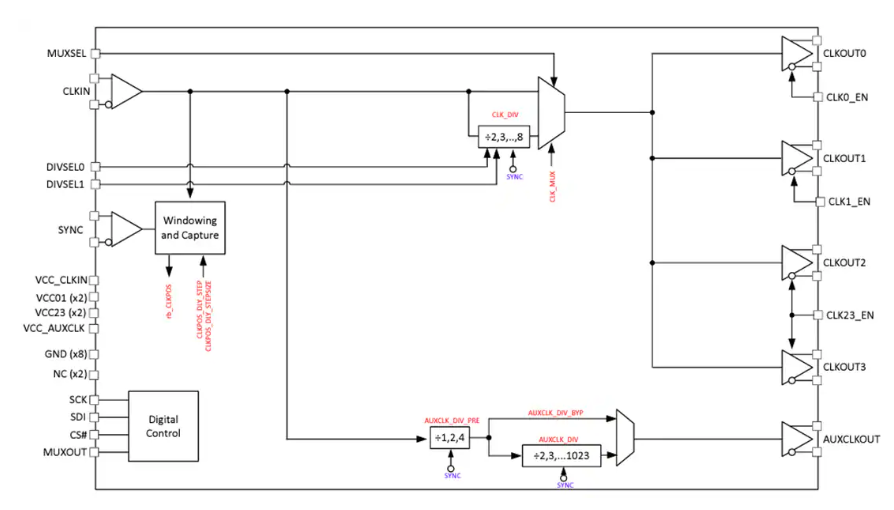

4. LOGICLK輸出

LOGICLK輸出可用于驅動需要較低頻率時鐘的設備,如FPGA。其輸出格式可編程為LVDS、LVPECL和CML模式,相應的SYSREF輸出格式也可在這三種模式中選擇。LOGICLK_DIV_PRE和LOGICLK_DIV分頻器用于將頻率降低到合適的范圍,確保輸入到LOGICLK_DIV分頻器的頻率不超過3.2GHz。當LOGICLK_DIV為奇數且不旁路時,占空比不為50%。通過SYNC功能可實現多個設備之間的分頻器同步。

5. SYSREF

SYSREF可生成與主時鐘或LOGICLK輸出重新時鐘同步的低頻率JESD204B/C兼容信號。CLKOUT和SYSREF輸出之間的延遲可通過軟件調整。SYSREF輸出可配置為發生器模式或中繼器模式。

- 發生器模式:內部發生器產生連續的SYSREF脈沖流,可通過SYSREFREQ引腳或SYSREFREQ_SPI位控制SYSREF分頻器,以提高噪聲隔離。

- 脈沖器模式:內部發生器在SYSREFREQ引腳上升沿或SYSREFREQ_SPI位從0變為1后,產生由SYSREF_PULSE_COUNT設置的1 - 16個脈沖。

- 中繼器模式:SYSREFREQ引腳輸入信號重新時鐘到時鐘輸出,并根據SYSREF_DELAY_BYPASS字段進行延遲后輸出到SYSREFOUT引腳。

6. SYSREF輸出緩沖器

- 主時鐘SYSREF輸出緩沖器:與時鐘輸出緩沖器結構相似,但增加了調整共模電壓的功能。SYSREF輸出為CML輸出,共模電壓可通過SYSREFOUTx_VCM字段調整,輸出電平可通過SYSREFOUTx_PWR字段編程。

- LOGICLK的SYSREF輸出緩沖器:支持LVDS、LVPECL和CML三種格式。LVDS模式下可通過LOGISYSREF_VCM字段編程共模電壓,LVPECL和CML模式需要外部組件,CML模式可通過LOGISYSREF_PWR字段控制輸出功率。

7. SYSREF頻率和延遲生成

在發生器模式下,SYSREF_DIV_PRE和SYSREF_DIV值用于將CLKIN頻率分頻到較低頻率,然后重新時鐘到輸出。在中繼器模式下,信號從SYSREFREQ引腳輸入。每個輸出都有獨立的延遲控制,最大延遲等于相位插值器周期,共有508個不同的延遲步長。可通過公式計算每個步長的大小和總延遲。

8. SYSREFREQ引腳和SYSREFREQ_SPI字段

SYSREFREQ引腳具有多種功能,可用于SYNC、SYSREF請求和SYSREF窗口功能。這些引腳可進行DC或AC耦合,具有雙50-Ω單端終端和可編程共模支持。SYSREFREQ_SPI字段可設置為1以模擬將這些引腳拉高的效果,簡化硬件設計。

9. SYNC功能

SYNC功能允許用戶同步CLK_DIV、LOGICLK_DIV、LOGICLK_DIV_PRE、SYSREF_DIV、SYSREF_DIV_PRE和SYSREF_DELAY_DIV分頻器,使不同電源周期之間的相位偏移保持一致,從而實現多個設備的同步。該同步只能通過SYSREFREQ引腳實現,不能通過軟件完成。

四、寄存器配置

LMX1204的寄存器配置對于實現其各種功能至關重要。文檔中詳細列出了各個寄存器的地址、位域、類型、復位值和功能描述。例如,R0寄存器可用于設置設備的低功耗狀態和軟復位;R2寄存器用于配置狀態機時鐘的預分頻器和使能狀態機時鐘發生器;R25寄存器用于選擇設備的功能模式(緩沖模式、分頻模式或倍增模式)以及設置時鐘分頻或倍增值等。在進行寄存器編程時,建議按照推薦的初始編程序列進行操作,避免對未記錄的地址進行寫入,以免影響設備的正常工作。

五、應用與實施要點

1. SYSREFREQ輸入配置

SYSREFREQ引腳支持單端或差分輸入,可采用AC或DC耦合模式。內部具有50-Ω終端和電容接地,等效于100-Ω差分終端。在不同的輸入配置下,需要合理選擇電阻和電容值,以確保引腳的共模電壓和信號傳輸的穩定性。例如,在AC耦合差分和單端輸入配置中,需要使用電阻終止器來創建每個引腳的共模電壓,并保持引腳P和引腳N之間的電位差大于150-mV;在DC耦合配置中,源共模電壓需要與設備輸入共模規格匹配。

2. 降低SYSREF共模電壓

對于某些需要較低SYSREF輸出共模電壓的數據轉換器應用,可以使用電阻分壓器來降低共模電壓。通過測試不同負載到地的情況下SYSREFOUTx引腳的單端電壓VOD和共模電壓VCM,可以選擇合適的電阻值來實現所需的電壓值。

3. 電流消耗

LMX1204的電流消耗隨設置條件的不同而變化。通過累加各個模塊的電流消耗,可以大致估算出任何設置條件下的電流。在不使用SYSREF輸出緩沖器時,建議關閉它們以節省電流。

4. 未使用引腳的處理

在實際應用中,并非所有引腳都需要使用。對于未使用的引腳,需要根據引腳的類型進行適當的處理。例如,所有Vcc引腳必須連接到電源;SYSREFREQ引腳在不同的使用模式下有不同的處理方式;CLKIN互補輸入在單端驅動時需要通過交流耦合電容和50Ω電阻接地等。

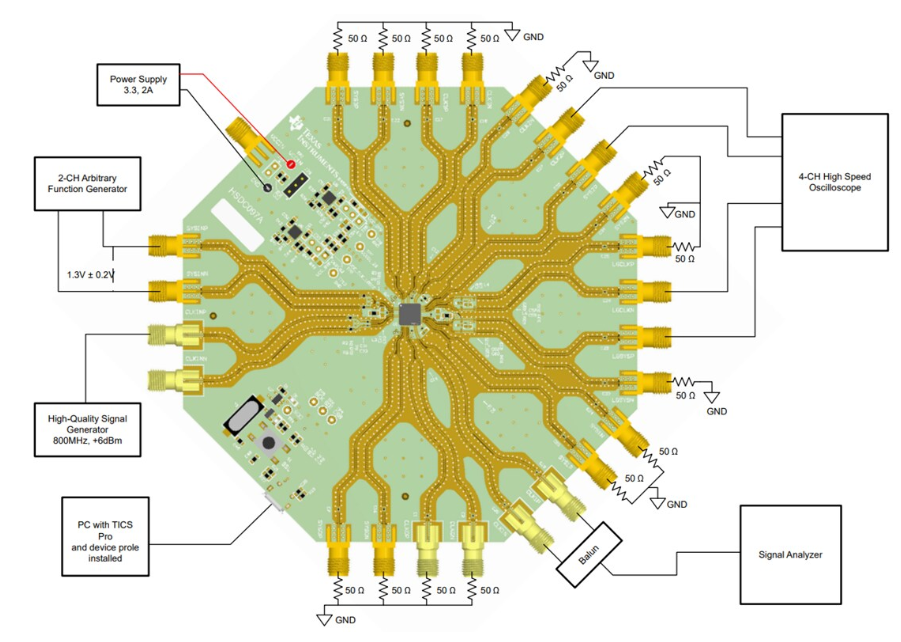

5. 典型應用示例

文檔中給出了一個將LMX1204作為×2倍增器與LMX2820的3-GHz輸出時鐘結合的典型應用示例。通過該示例可以看出,在1-MHz至20-MHz范圍內,LMX1204會增加相位噪聲,但在超過20MHz后,輸入倍增器實際上會對輸出噪聲底限進行濾波。在設計過程中,可使用TICS Pro軟件計算必要的寄存器值并配置設備。

6. 電源供應建議

LMX1204采用2.5V電源供電,直接連接到開關電源可能會導致輸出出現不需要的雜散。建議在所有電源引腳處進行旁路處理,將具有最小阻抗高頻特性的小電容放置在與器件同一層并盡可能靠近引腳,較大值的旁路電容用于內部LDO穩定性,可適當遠離器件。如果同時使用時鐘和LOGICLK的電源引腳,建議使用小電阻或鐵氧體磁珠進行隔離。

7. 布局指南

在PCB布局時,需要注意以下幾點:如果使用單端輸出,需要對互補側進行端接,以確保阻抗匹配;盡量縮短CLKIN走線的長度,以獲得最佳的相位噪聲性能;確保器件的DAP引腳通過多個過孔良好接地;使用低損耗的介電材料,如Rogers 4350B,以提高輸出功率;如果所有輸出和SYSREF都在工作,電流消耗可能會導致芯片結溫超過推薦的125°C,可能需要使用散熱片。

六、總結與思考

LMX1204作為一款高性能的低噪聲、高頻JESD緩沖器/倍增器/分頻器,憑借其豐富的功能、出色的性能和靈活的配置,在多個領域都有著廣泛的應用前景。然而,在實際使用過程中,我們也需要充分考慮其寄存器配置、輸入輸出配置、電流消耗和布局等方面的問題,以確保其性能的充分發揮。同時,對于電子工程師來說,不斷學習和掌握新的器件特性和應用技術,才能在日益復雜的電子設計領域中應對各種挑戰。大家在使用LMX1204的過程中,是否也遇到過一些獨特的問題或者有一些創新的應用思路呢?歡迎在評論區分享交流。

-

應用領域

+關注

關注

0文章

304瀏覽量

8366

發布評論請先 登錄

Texas Instruments LMX1205 JESD緩沖器/乘法器/除法器數據手冊

?LMX1205 低噪聲高頻JESD緩沖器/乘法器/分頻器技術文檔摘要

LMX1204低噪聲高頻JESD緩沖器/倍頻器/分頻器技術解析

?LMX1204 低噪聲高頻 JESD 緩沖器/乘法器/分頻器技術文檔總結

LMX1204高性能JESD緩沖器/乘法器/分頻器技術解析與應用指南

LMX1204:低噪聲、高頻JESD緩沖器/倍增器/分頻器的卓越之選

LMX1204:低噪聲、高頻JESD緩沖器/倍增器/分頻器的卓越之選

評論