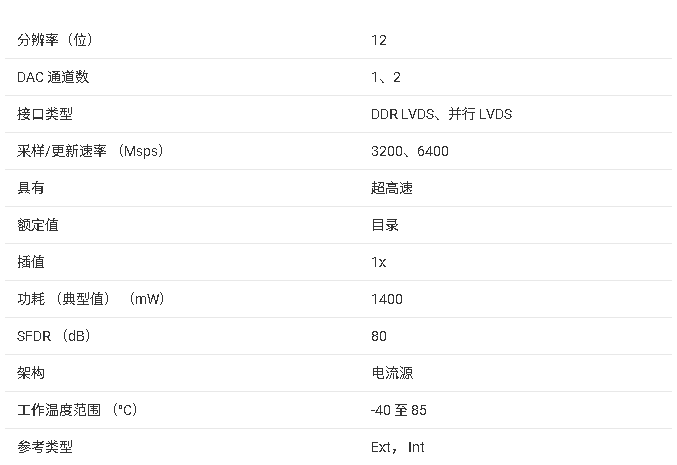

DAC12DL3200:高速低延遲數模轉換器的技術剖析與應用探索

在電子工程領域,數模轉換器(DAC)作為連接數字世界與模擬世界的橋梁,其性能的優劣直接影響著整個系統的表現。今天,我們就來深入探討一款高性能的DAC——DAC12DL3200,看看它在高速、低延遲等方面有著怎樣的出色表現和應用潛力。

文件下載:dac12dl3200.pdf

一、DAC12DL3200的核心特性

1. 高分辨率與高速率

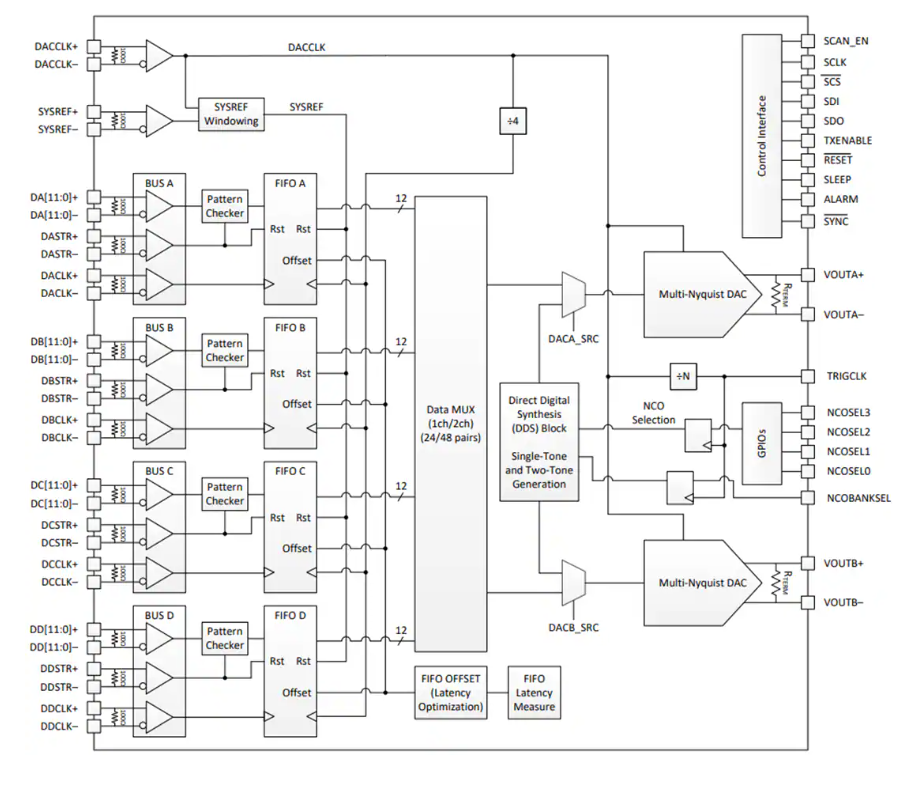

DAC12DL3200擁有12位的分辨率,能夠提供較為精確的模擬輸出。在采樣率方面,它支持單通道高達6.4 GSPS,雙通道高達3.2 GSPS的輸入輸出速率,這使得它在處理高速信號時游刃有余,能夠滿足許多對數據處理速度要求極高的應用場景。

2. 多Nyquist工作模式

該DAC具備多種Nyquist工作模式,包括單通道的NRZ、RTZ、RF模式,以及雙通道的NRZ、RTZ、RF、2xRF模式。不同的模式適用于不同的應用需求,例如NRZ模式適用于第一Nyquist區的操作,而RF模式則可以增強第二Nyquist區的輸出功率,為工程師提供了更多的靈活性。

3. 低延遲特性

低延遲是DAC12DL3200的一大亮點,其從數字輸入到模擬輸出的延遲僅為6到8 ns,與低延遲接收器ADC12DL3200配合使用時,DAC和ADC的組合延遲小于15 ns(不包括FPGA)。這對于那些對延遲敏感的應用,如電子戰系統,能夠確保信號的實時處理和響應。

4. 并行LVDS接口

采用并行DDR LVDS接口,具有源同步接口,簡化了時序設計。它支持24或48個LVDS對,每個對的速率高達1.6 Gbps,并且每12位總線配備1個LVDS DDR時鐘。這種接口設計不僅提高了數據傳輸的速度,還增強了系統的穩定性。

5. 寬輸出頻率范圍

輸出頻率范圍超過8 GHz,能夠直接覆蓋C波段(8 GHz)及以上,這使得它在高頻信號處理方面具有很大的優勢,可用于雷達、衛星通信等領域。

6. 片上直接數字合成器(DDS)

片上集成了DDS,支持單音和雙音正弦波生成,擁有32個32位數控振蕩器,具備快速跳頻能力(小于500 ns),并且支持同步CMOS頻率/相位輸入。這為信號的生成和處理提供了更多的功能和可能性。

二、DAC輸出模式詳解

1. 非歸零(NRZ)模式

NRZ模式是標準的零階保持輸出波形,在時域上可以看作是一個矩形濾波器,在頻域上呈現sinc響應。它適用于第一Nyquist區的操作,在該區域內具有較好的性能,但在第二和第三Nyquist區會有較大的功率損失。

2. 歸零(RTZ)模式

RTZ模式與標準的零階保持輸出波形類似,但在采樣周期的后半部分增加了一個歸零脈沖。這使得它在頻域上的sinc響應擴展了兩倍,在第二Nyquist區的功率損失相對較小,可用于第一和第二Nyquist區的應用。

3. 射頻(RF)模式

RF模式通過在采樣周期的中間對采樣值進行反轉,增加了一個混合功能。其sinc響應在第二Nyquist區達到峰值并提供最大的平坦度,因此該模式主要適用于第二Nyquist區。

4. 2x射頻(2xRF)模式

2xRF模式是RF模式和歸零模式的組合,在采樣周期的前半部分采用RF模式,后半部分采用歸零模式。它的sinc響應在第三、第四和第五Nyquist區達到峰值并提供最大的平坦度,不過該模式僅在雙通道模式下可用,并且需要輸入時鐘為DAC采樣率的兩倍。

三、LVDS接口與同步機制

1. LVDS接口的工作模式

DAC12DL3200的LVDS接口有多種工作模式,如MODE0采用雙通道,每個通道使用兩個12位LVDS數據總線;MODE1采用雙通道,每個通道使用一個12位LVDS數據總線;MODE2采用單通道,使用四個12位LVDS數據總線。不同的模式可以根據實際需求選擇,以滿足不同的數據傳輸速率和系統配置。

2. 同步機制

為了實現多設備的同步,DAC12DL3200支持使用同步信號(SYSREF)。SYSREF窗口化功能可以簡化多設備系統中的同步設置,其時鐘方案與JESD204B時鐘設備兼容。通過合理設置SYSREF相關寄存器,可以確保系統在不同的工作條件下都能實現穩定的同步。

四、應用場景與啟動流程

1. 典型應用場景

DAC12DL3200適用于多種應用場景,如電子戰、脈沖發生器、任意波形發生器(AWG)等。在電子戰系統中,其低延遲特性能夠確保快速響應和精確的信號處理;在AWG中,高采樣率和多工作模式可以生成各種復雜的波形。

2. 啟動流程

LVDS輸入啟動流程

使用LVDS輸入時,啟動流程包括啟動DEVCLK、按順序施加電源、進行復位操作、配置器件參數、等待Fuse ROM加載完成、施加輸入信號、設置DP_EN、清除相關告警、同步系統、配置FIFO_DLY、清除所有系統告警、等待數據刷新,最后啟用傳輸。

NCO操作啟動流程

在NCO僅模式下,啟動流程與LVDS輸入模式類似,但需要額外配置NCO相關參數,如頻率和相位設置。在啟動過程中,需要注意NCO的同步和使能操作,以確保系統的正常運行。

五、設計要點與注意事項

1. 電源設計

該器件需要三種不同的電源電壓,分別為1.8 VDC、1.0 VDC和 -1.8 VDC。推薦使用高效的開關轉換器進行降壓,然后通過第二級調節來減少開關噪聲并提高電壓精度。在電源設計中,要注意避免數字開關噪聲耦合到模擬信號鏈中,盡量不共享VDDDIG與模擬電源電壓,如果需要共享,要進行仔細的電源濾波。

2. 布局設計

在電路板設計中,對于模擬輸出信號、CLK和SYSREF、LVDS數據輸入、電源連接和接地連接等關鍵信號需要特別注意。例如,模擬輸出信號和CLK、SYSREF信號應采用松散耦合的100 - Ω差分走線,以保證信號質量;LVDS數據輸入應采用緊密耦合的100 - Ω差分走線,以減少布線面積和相鄰數據對之間的串擾。同時,建議在進行電路板制造之前對關鍵信號走線進行信號質量仿真,以確保設計的可靠性。

DAC12DL3200以其高分辨率、高速率、低延遲、多工作模式等特性,為電子工程師在高速信號處理和模擬輸出方面提供了一個強大的工具。在實際應用中,我們需要深入理解其特性和工作原理,合理進行設計和配置,以充分發揮其優勢,滿足不同應用場景的需求。大家在使用過程中遇到過哪些問題或者有什么獨特的應用經驗,歡迎在評論區分享交流。

-

數模轉換器

+關注

關注

14文章

1296瀏覽量

85741

發布評論請先 登錄

介紹DAC數模轉換器以及DMA的使用

DAC12DL3200 12 位、低延遲、雙通道 3.2GSPS 或單通道 6.4GSPS、RF 采樣 DAC技術手冊

DAC12DL3200:高速低延遲數模轉換器的技術剖析與應用探索

DAC12DL3200:高速低延遲數模轉換器的技術剖析與應用探索

評論