7-Bit 0.25dB Digital Step Attenuator F1958:設計與應用全解析

在電子設計領域,對于基站(BTS)無線電卡等應用而言,數字步進衰減器(DSA)起著至關重要的作用。今天我們要深入探討的是Renesas的F1958,一款7位0.25dB數字步進衰減器,它在1MHz至6GHz的頻率范圍內展現出卓越的性能。

文件下載:F1958NBGK8.pdf

一、產品概述

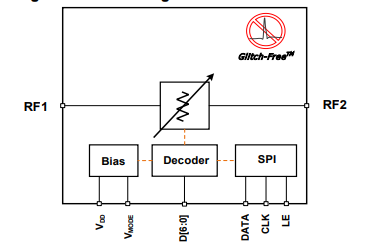

F1958屬于Renesas Glitch - Free?系列DSA,專為滿足基站無線電卡等嚴苛應用需求而優化。它采用緊湊的4 x 4 mm 24引腳封裝,輸入和輸出阻抗均為50Ω,便于集成到無線電或射頻系統中。

(一)高可靠性設計

該器件由QFN封裝中的單片硅芯片構建而成,具有極高的可靠性。插入損耗極低,失真極小,并且能夠實現極其精確的衰減水平。這些精確的衰減水平有助于提高系統的信噪比(SNR)和/或鄰道泄漏比(ACLR),確保系統增益盡可能接近目標水平。

(二)快速切換特性

在并行模式下,F1958具有極快的建立時間,非常適合快速切換系統。此外,它采用了Renesas的Glitch - Free?技術,與其他競爭產品相比,能夠在衰減狀態轉換期間保護功率放大器或ADC。

二、競爭優勢

(一)低插入損耗

F1958擁有最低的插入損耗,能夠為系統提供最佳的SNR,這對于對信號質量要求極高的應用來說至關重要。

(二)Glitch - Free?技術

該技術可有效保護功率放大器或ADC在衰減狀態轉換時不受損害,提高了系統的穩定性和可靠性。

(三)精確的衰減水平

極其精確的衰減水平能夠確保系統增益的準確性,從而提高系統的整體性能。

(四)超低失真

超低的失真特性使得信號在傳輸過程中能夠保持較高的質量,減少了信號的畸變。

(五)高ESD防護

具有MSL1和2000V HBM ESD防護能力,增強了器件在復雜環境下的抗干擾能力。

三、典型應用

F1958的應用場景十分廣泛,包括但不限于以下幾個方面:

(一)基站系統

在3G/4G/4G +基站系統中,F1958能夠精確控制信號的衰減,確保信號的穩定傳輸。

(二)分布式天線系統(DAS)

在DAS中,它可以根據實際需求調整信號強度,優化信號覆蓋范圍。

(三)遠程無線電頭端

為遠程無線電頭端提供精確的信號衰減控制,提高通信質量。

(四)有源天線系統(AAS)和寬帶衛星設備

在這些對信號精度要求極高的系統中,F1958能夠發揮重要作用。

(五)NFC基礎設施和軍事通信設備

在NFC基礎設施和軍事通信設備中,其高可靠性和精確的衰減控制能力能夠滿足特殊環境下的通信需求。

四、產品特性

(一)接口靈活

支持串行和7位并行接口,用戶可以根據實際需求選擇合適的接口方式。

(二)寬衰減范圍

具有31.75dB的衰減范圍,且以0.25dB為步進,能夠滿足不同的衰減需求。

(三)快速建立時間

對于0.25dB步進,建立時間僅為500ns,能夠實現快速的信號調整。

(四)低插入損耗

在4GHz時,插入損耗小于1.7dB,有效減少了信號的損失。

(五)高精度衰減

在4GHz時,衰減誤差小于±0.2dB,確保了衰減的精確性。

(六)雙向RF使用

支持雙向RF使用,增加了器件的使用靈活性。

(七)寬電源范圍

可使用3.3V或5V電源,適應不同的電源環境。

(八)寬工作溫度范圍

工作溫度范圍為 - 40°C至 + 105°C,能夠在惡劣的環境條件下正常工作。

(九)緊湊封裝

采用4 x 4 mm薄型24 - QFN封裝,節省了電路板空間。

五、引腳分配與描述

(一)引腳分配

F1958的引腳分配清晰明確,不同的引腳承擔著不同的功能。例如,D0 - D6為并行控制引腳,用于控制不同的衰減量;RF1和RF2為RF端口,可作為輸入或輸出端口;VDD為電源輸入引腳等。

(二)引腳描述

每個引腳都有詳細的描述,如D0引腳為0.25dB的并行控制引腳,拉高該引腳可實現相應的衰減。同時,對于一些關鍵引腳,如VDD引腳,需要使用電容器盡可能靠近引腳接地,以減少電源噪聲。

六、電氣特性

(一)絕對最大額定值

明確了器件在不同參數下的絕對最大額定值,如電源電壓、控制引腳電壓、RF端口電壓、最大RF輸入功率、結溫等。超過這些額定值可能會導致器件永久性損壞,因此在設計過程中必須嚴格遵守。

(二)推薦工作條件

給出了器件的推薦工作條件,包括電源電壓、工作溫度范圍、RF頻率范圍、最大輸入功率等。在這些條件下使用器件,能夠確保其性能的穩定性和可靠性。

(三)電氣特性詳細參數

涵蓋了邏輯輸入高電平、邏輯輸入低電平、邏輯電流、插入損耗、相對相位、步進誤差、絕對衰減誤差、端口回波損耗、輸入IP3、輸入0.1dB壓縮點等多個方面的詳細參數。這些參數是評估器件性能的重要依據,工程師在設計時需要根據實際需求進行綜合考慮。

七、編程模式

(一)串行模式

通過將VMODE引腳拉高至邏輯高電平來選擇串行模式。串行接口使用8位字,但僅使用其中的7位,數據以LSB(D0)先移入的方式進行傳輸。在串行編程時,所有并行控制輸入引腳必須接地。

(二)并行控制模式

用戶可以選擇直接并行模式或鎖存并行模式。

- 直接并行模式:當VMODE引腳浮空或為邏輯低電平,且LE引腳為邏輯高電平時,選擇直接并行模式。在該模式下,器件會立即對并行控制引腳的電壓變化做出反應,適用于需要快速建立時間的應用。

- 鎖存并行模式:當VMODE引腳浮空或為邏輯低電平,且LE引腳從邏輯低電平切換到邏輯高電平時,選擇鎖存并行模式。在該模式下,需要先設置好并行控制引腳的電壓,然后將LE引腳拉高,器件才會轉換到相應的衰減設置。

八、評估套件

(一)套件組成

評估套件包含了評估F1958所需的各種組件,如開關、連接器、電容器、電阻器等。通過評估套件,用戶可以方便地對器件進行測試和驗證。

(二)操作步驟

評估套件的操作步驟包括電源供應設置、并行邏輯控制設置、串行邏輯控制設置、上電和下電程序等。在操作過程中,需要嚴格按照步驟進行,以確保測試結果的準確性。

九、應用信息

(一)數字引腳電壓和電阻值

明確了各個控制引腳的開路直流電壓和內部連接情況,為工程師在設計電路時提供了重要的參考。

(二)電源供應

建議使用公共電源為所有需要直流電源的引腳供電,并使用外部電容器對電源引腳進行旁路,以減少噪聲和快速瞬變。同時,對電源電壓的變化率和控制引腳的電壓范圍也有相應的要求。

(三)控制引腳接口

當控制信號的完整性成為問題時,推薦在每個控制引腳的輸入處使用特定的電路,以確保信號的穩定性。

十、訂購信息

提供了不同型號的訂購信息,包括封裝形式、MSL評級、運輸包裝和溫度范圍等。工程師可以根據實際需求選擇合適的型號。

F1958數字步進衰減器憑借其卓越的性能、靈活的接口和廣泛的應用場景,為電子工程師在設計射頻系統時提供了一個優秀的選擇。在實際應用中,工程師需要根據具體的需求和設計要求,充分發揮其優勢,確保系統的性能和可靠性。你在使用數字步進衰減器時遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

產品特性

+關注

關注

0文章

69瀏覽量

899

發布評論請先 登錄

基于RFSA2644下的SERIAL CONTROLLED DIGITAL STEP ATTENUATOR 50MHz TO 4000MHz 6-BIT 0.5dB LSB

基于RFSA3715下的5MHz to 4000MHz Digital Step Attenuator

基于RFSA3714下的50MHz to 6000MHz Digital Step Attenuator

基于RFSA3713下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA3613下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA2724下的Serial Controlled Digital Step Attenuator 50MHz to 4000MHz

基于RFSA3523下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA2534下的50?MHz to 4000?MHz Digital Step Attenuator

基于QPC6713下的50MHz to 6000MHz Digital Step Attenuator

基于RFSA3623下的5MHz to 6000MHz Digital Step Attenuator

基于RFSA2524下的SERIAL CONTROLLED DIGITAL STEP ATTENUATOR 50MHz TO 4000MHz 5-BIT 1dB LSB

7位0.25dB數字步進衰減器F1958:特性與應用解析

7-Bit 0.25dB Digital Step Attenuator F1958:設計與應用全解析

7-Bit 0.25dB Digital Step Attenuator F1958:設計與應用全解析

評論