1 實驗要求

在FPGA上生成1280x720@60分辨率的視頻信號,通過DE10-Nano的 HDMI輸出到顯示屏上進行顯示,顯示的內容是一個黑色方塊每隔10ms移動一個像素位置,方塊遇到邊框自行回彈,屏幕背景為白色,屏幕邊框為綠色。

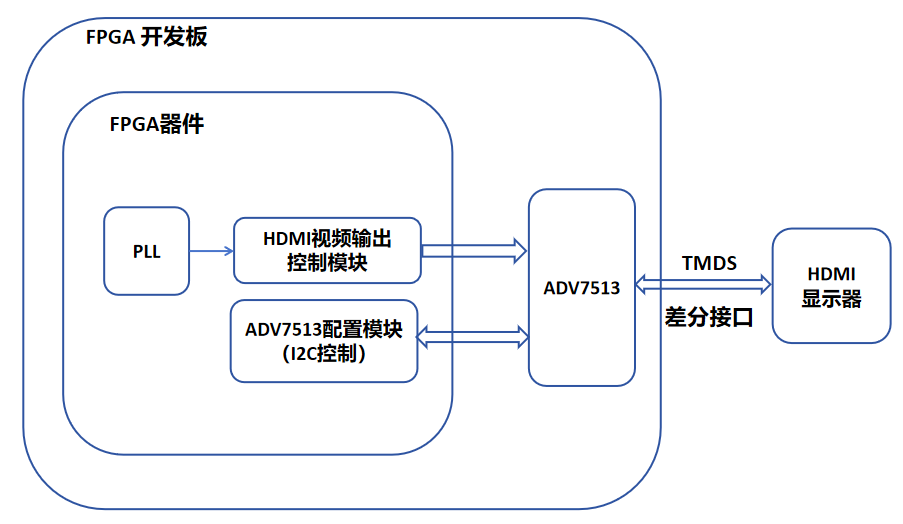

2 設計框圖

根據實驗要求分析可得出,想要控制ADV7513最終在HDMI顯示器上顯示畫面,需要先配置ADV7513寄存器,配置通過I2C總線,該部分的控制原理在前面(參考文末往期閱讀的鏈接)已經講解過。

想要在HDMI顯示器上顯示邊框,方塊和白色背景,需要設計一個滿足DMT時序的視頻信號。

1280x720@60分辨率的像素時鐘是74.25MHz,所以這里可調用Altera的PLL IP來生成這個時鐘(系統時鐘是50MHz)。

整個系統的設計框圖如下所示:

3 代碼實現

(1)Top level代碼

主要是例化PLL、HDMI顯示和I2C控制三個模塊。具體代碼參考工程。

(2)HDMI控制器模塊

HDMI控制器模塊用于生成1280x720分辨率的視頻信號,并在屏幕上顯示一個每隔10ms移動的黑色方塊,背景為白色,屏幕邊框為綠色。

1. 首先是1280*720分辨率時序參數的設定。如下是行時序參數設定:

這些參數對應到時序如下圖所示:

如下是場時序參數設定:

這些參數對應到時序如下圖所示:

2. 實現行計數器和場計數器,用于跟蹤當前像素位置,以及生成像素點橫縱坐標:

3. 根據行場計數器生成行場同步信號:

4. 根據行場計數器生成像素點橫縱坐標:

5. hdmi_ctrl模塊的時鐘是74.25MHz(1280*720@60對應的像素時鐘),利用計數器產生10ms間隔:

6. 當方塊移動到邊界時,改變移動方向:

根據代碼畫出方向改變的框圖示意圖如下:

7. 根據方塊移動方向,改變其縱橫坐標:

8. 給不同的區域繪制不同的顏色:

(3)I2C控制模塊

I2C控制模塊直接參考本文第8.3章節(內容一模一樣)。

4 硬件準備

HDMI顯示器一臺

HDMI cable 一根

5 軟件安裝 1. 進入Altera官網選擇Quartus Prime Lite 17.1版本:

2. 點擊Indicidual Files 找到Cyclone V的器件包并下載:

3. 往下繼續找到Intel Quartus Software下載QuartusLiteSetup壓縮包和ModelSimSetup壓縮包(后續會有仿真章節):

4. 所有文件都下載完以后,雙擊QuartusLiteSetup-17.1.0.590-windows.exe文件進行安裝。安裝的過程中會默認選擇一起安裝Nios II IDE、ModelSim和Cyclone V器件包(未勾選時可自行勾選這些內容),建議安裝的過程中所有默認設置都保留(除了安裝路徑自己選擇外)。USB Blaster II驅動程序將在軟件安裝結束時提示安裝。 6 操作步驟 1. 打開Quartus軟件,點擊File——New Project Wizard...

2. 點擊Next:

3. 在如下對話框里面選擇工程路徑和工程名稱:

4. 繼續點擊Next:

5. 繼續點擊Next:

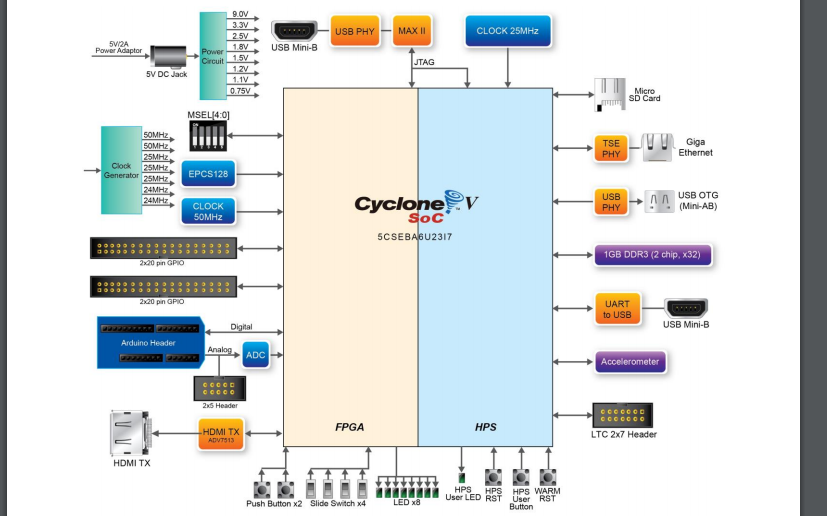

6. 然后在如下對話框里面鍵入DE10-Nano對應的FPGA器件(5CSEBA6U23I7):

7. 點擊Finish結束工程的創建:

8. 開始新建Top工程,點擊File——New...

9. 選擇Verilog HDL File 然后點擊OK:

10. 編Verilog代碼(代碼可以參考隨本文一起提供的工程)并保存為HDMI_block_move.v文件:

11. 用同樣的方法新建.v文件,編Verilog代碼(代碼可以參考隨本文一起提供的工程)并保存為hdmi_ctrl.v文件:

12. 將第八章節提到的I2C控制器所包含的三個.v文件拷貝到當前工程路徑下:

13. 并將這三個文件添加到當前工程里面以便后面編譯的時候會調用這三個文件,具體做法是點擊Project——Add/Remove Files in Project..., 然后點擊File Name旁邊的...瀏覽到三個文件所在路徑,選中這三個文件然后點擊打開按鈕:

14. 然后點擊Apply和OK按鈕結束工程文件的添加:

15. 接下來配置PLL IP,在IP Catalog里面搜索pll 找到Altera PLL,點擊它:

16. 在出現如下的對話框里填入pll的名稱為pll,然后點擊OK:

17. 在Reference Clock Frequency處填寫50,在outclk0處填寫74.25,然后點擊Finish結束pll的配置:

18. 等pll模塊生成以后會彈出如下對話框,點擊Yes將其添加到當前工程:

19. 這時FPGA電路設計基本完成,接下來是引腳分配,首先點擊Start Analysis&Synthesis按鈕對工程進行分析和綜合,這樣在后面引腳分配的時候信號端口才能出現:

20. 接下來參考DE10-Nano的 usermanual文檔或者schematic文件來分配引腳,該工程引腳分配如下:

21. 引腳分配完成就點擊Start Compilation按鈕開始全編譯工程:

22. 工程全編譯結束后在HDMI_block_moveoutput_files路徑下會產生HDMI_block_move.sof文件,接下來點擊Programmer 按鈕將此文件配置到FPGA里面去:

23. 點擊Hardware Setup(在這之前記得用一根HDMI線纜連接HDMI顯示器和DE10-Nano, 然后用一根Mini USB線連接PC和DE10-Nano, 然后給DE10-Nano開發板插上5V電源),選擇DE-SoC[USB-1]端口,點擊Close:

24. 點擊Auto Detect,選擇5CSEBA6,然后點擊OK:

25. 如果出現如下窗口,點擊Yes:

26. 此時系統會出現兩個器件,一個是SOCVHPS, 一個是5CSEBA6U23,鼠標右擊5CSEBA6U23選擇Change File:

27. 瀏覽到HDMI_block_move.sof路徑下選擇該文件,然后點擊Open:

28. 點選如下復選框,然后點擊Start開始FPGA 文件配置:

29. 當Progress進度條顯示100%(顏色變綠了)代表FPGA配置完成:

7 實驗現象

可以觀察到HDMI顯示器上有個綠色邊框,中間背景為白色,有個黑色小方塊在屏幕中移動。

HDMI_block_move工程下載鏈接: https://pan.baidu.com/s/1LwQjqLpmZMl5IkvTgzo-3w

提取碼: tera

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636207 -

顯示器

+關注

關注

22文章

5146瀏覽量

144374 -

HDMI

+關注

關注

34文章

1899瀏覽量

160492

原文標題:7-DE10-Nano的HDMI方塊移動案例的整體實現(含Quartus完整工程免費下載)

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA開發板DE10-Standard和T-Core的串口通信設計

來自InnovateFPGA的全球令人印象深刻的創新設計

【正點原子FPGA連載】第十九章HDMI方塊移動實驗-領航者ZYNQ之FPGA開發指南

ADI開發板擴展DE10-Nano 套件功能

如何使用英特爾FPGA加速軟件

DE1O Nano SoC開發板的用戶手冊免費下載

【正點原子FPGA連載】第二十五章HDMI方塊移動實驗 -摘自【正點原子】新起點之FPGA開發指南_V2.1

用于Terasic DE10-納米套件的實際插件

使用友晶DE10-Nano開發板的HDMI彩條顯示案例

使用DE10-Nano的HDMI方塊移動案例的整體實現

使用DE10-Nano的HDMI方塊移動案例的整體實現

評論