深入解析CDx4HC147與CD74HCT147:高速CMOS優先編碼器的卓越之選

在電子設計領域,優先編碼器是一種常用的邏輯器件,用于將多個輸入信號編碼為較少位數的輸出信號。今天,我們將深入探討Texas Instruments(TI)的CDx4HC147和CD74HCT147,這兩款高速CMOS邏輯10 - 至4 - 線優先編碼器在眾多應用中展現出了卓越的性能。

文件下載:cd74hc147.pdf

產品特性亮點

電氣性能出色

- 低傳播延遲:在(V{CC}=5V)、(C{L}=15pF)、(T_{A}=25^{circ}C)的典型條件下,傳播延遲僅為13ns,能夠實現快速的數據處理和傳輸,大大提高了系統的響應速度。

- 高扇出能力:總線驅動輸出可提供15個LSTTL負載的驅動能力,能夠輕松驅動多個負載設備,滿足不同規模系統的設計需求。

寬工作范圍

- 溫度范圍廣:支持 - 55°C至125°C的寬工作溫度范圍,適用于各種惡劣的工業和汽車環境,確保設備在極端條件下仍能穩定工作。

- 電源電壓靈活:HC類型支持2V至6V的電源電壓范圍,具有較高的噪聲免疫力((N{IL}=30%),(N{IH}=30%) of (V{CC}) at (V{CC}=5V));HCT類型則在4.5V至5.5V的電壓范圍內工作,與LSTTL輸入邏輯直接兼容((V{IL}=0.8V) (Max),(V{IH}=2V(Min))),同時具備CMOS輸入兼容性((I{1} ≤1μA) at (V{OL}),(V_{OH}))。

功耗顯著降低

相較于LSTTL邏輯IC,CDx4HC147和CD74HCT147在功耗方面有了顯著的降低,有助于減少系統的整體功耗,延長電池續航時間,提高能源利用效率。

產品詳細描述

CDx4HC147和CD74HCT147是9輸入優先編碼器,通過隱含的十進制“零”實現了10線至4線的優先編碼功能。它們采用高速硅柵CMOS技術,與低功耗肖特基TTL(LSTTL)引腳兼容,能夠方便地替代傳統的TTL器件。

引腳配置與功能

| 引腳編號 | 引腳名稱 | 輸入/輸出 | 描述 |

|---|---|---|---|

| 1 | I4 | 輸入 | 低電平有效輸入4 |

| 2 | I5 | 輸入 | 低電平有效輸入5 |

| 3 | I6 | 輸入 | 低電平有效輸入6 |

| 4 | I7 | 輸入 | 低電平有效輸入7 |

| 5 | I8 | 輸入 | 低電平有效輸入8 |

| 6 | Y2 | 輸出 | 低電平有效輸出2 |

| 7 | Y1 | 輸出 | 低電平有效輸出1 |

| 8 | GND | 接地 | 接地引腳 |

| 9 | I0 | 輸入 | 低電平有效輸入0 |

| 10 | I9 | 輸入 | 低電平有效輸入9 |

| 11 | I1 | 輸入 | 低電平有效輸入1 |

| 12 | I2 | 輸入 | 低電平有效輸入2 |

| 13 | I3 | 輸入 | 低電平有效輸入3 |

| 14 | Y3 | 輸出 | 低電平有效輸出3 |

| 15 | NC | 無 | 無內部連接 |

| 16 | VCC | 電源 | 正電源引腳 |

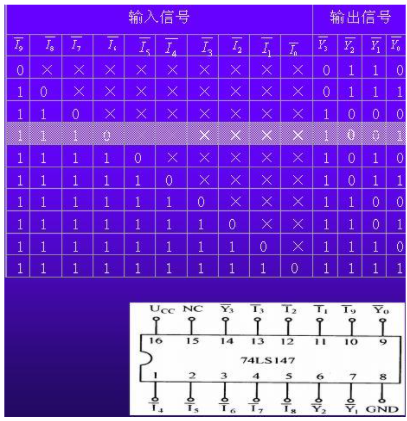

真值表

| 輸入 | 輸出 | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| I1 | I2 | I3 | I4 | I5 | I6 | I7 | I8 | I9 | Y3 | Y2 | Y1 | Y0 |

| H | H | H | H | H | H | H | H | H | H | H | H | H |

| X | X | X | X | X | X | X | X | L | L | H | H | L |

| X | X | X | X | X | X | X | L | H | L | H | H | H |

| X | X | X | X | X | X | L | H | H | H | L | L | L |

| X | X | X | X | X | L | H | H | H | H | L | L | H |

| X | X | X | X | L | H | H | H | H | H | L | H | L |

| X | X | X | L | H | H | H | H | H | H | L | H | H |

| X | X | L | H | H | H | H | H | H | H | H | L | L |

| X | L | H | H | H | H | H | H | H | H | H | L | H |

| L | H | H | H | H | H | H | H | H | H | H | H | L |

從真值表中可以看出,當多個輸入同時有效時,具有最高優先級的輸入將在輸出中得到體現,輸入線I9具有最高優先級。

應用與實現建議

電源供應

電源電壓應在推薦的工作范圍內選擇,每個(V_{CC})終端應配備一個良好的旁路電容,以防止電源干擾。建議使用0.1μF的電容,也可以并聯多個旁路電容以抑制不同頻率的噪聲,如0.1μF和1μF的電容并聯使用。旁路電容應盡可能靠近電源端子安裝,以獲得最佳效果。

布局設計

- 旁路電容放置:應靠近設備的正電源端子放置,提供電氣上較短的接地返回路徑,使用寬走線以最小化阻抗,并盡量將設備、電容和走線布置在電路板的同一側。

- 信號走線幾何形狀:信號走線寬度建議為8mil至12mil,長度應小于12cm,以減少傳輸線效應。避免信號走線出現90°角,在信號走線下方使用連續的接地平面,并在信號走線周圍填充接地。對于長度超過12cm的走線,應使用阻抗控制走線,在輸出端附近使用串聯阻尼電阻進行源端端接,并避免分支,對于必須分支的信號應單獨進行緩沖。

文檔支持與注意事項

文檔支持

TI提供了豐富的應用報告,如《CMOS Power Consumption and (C_{p d}) Calculation》、《Designing With Logic》和《Thermal Characteristics of Standard Linear and Logic (SLL) Packages and Devices》等,幫助工程師更好地理解和使用這些器件。

靜電放電注意事項

由于該集成電路可能會受到靜電放電(ESD)的損壞,TI建議在處理所有集成電路時采取適當的預防措施,否則可能會導致性能下降甚至設備完全失效。

總結

CDx4HC147和CD74HCT147以其出色的電氣性能、寬工作范圍和低功耗等優點,成為了電子工程師在優先編碼器設計中的理想選擇。在實際應用中,合理的電源供應和布局設計對于發揮器件的最佳性能至關重要。同時,關注文檔更新和靜電放電防護也是確保設計成功的關鍵因素。你在使用類似優先編碼器時遇到過哪些挑戰?又是如何解決的呢?歡迎在評論區分享你的經驗。

-

優先編碼器

+關注

關注

0文章

5瀏覽量

1539

發布評論請先 登錄

CD54HC147,CD74HC147,CD74HCT147

CD54HC147 高速 CMOS 邏輯 10 至 4 線優先級編碼器

CD74HC147 高速 CMOS 邏輯 10 至 4 線優先級編碼器

CD74HCT147 高速 CMOS 邏輯 10 至 4 線優先級編碼器

高速CMOS邏輯六路緩沖器/線路驅動器CDx4HC367、CDx4HC368、CDx4HCT367、CD74HCT368數據表

深入解析CDx4HC147與CD74HCT147:高速CMOS優先編碼器的卓越之選

深入解析CDx4HC147與CD74HCT147:高速CMOS優先編碼器的卓越之選

評論