面向:PTP Grandmaster / Boundary Clock、SyncE 設備時鐘、SSU/SEC 及電力/軌交等關鍵基礎設施授時節點

目標:在 窄帶伺服/PLL 與復雜板級噪聲環境下,獲得更低輸出抖動、更穩健 holdover,并形成可量產的驗證閉環

目錄

1. 典型痛點:為什么“協議沒問題,指標還是過不了”

2. 方案目標:把系統指標翻譯成 OCXO 語言

3. 方案架構:OCXO 在 PTP/SyncE 時鐘樹里的位置

4. 選型規范:建議你在 RFQ/評審里寫清楚的參數

5. 參考設計要點:供電、VCTRL、布局三大紀律

6. 驗證閉環:四步法把“器件好看”變成“系統過標”

7. 推薦器件短名單:FOC-5S-LN vs FOC-6S 如何選

8. 常見問題(FAQ)

9. 參考鏈接(原文回鏈)

1. 典型痛點:為什么“協議沒問題,指標還是過不了”

在分組定時(PTP/IEEE1588)與 SyncE 場景里,很多項目會出現類似現象:

實驗室 bench 條件測得抖動不錯,但一上整機(真實電源樹 + 高速 SerDes + DC/DC)抖動/相噪明顯變差

GNSS 丟失或上游參考劣化后,TE/MTIE/TDEV 上升過快,holdover 不穩

伺服帶寬調窄后,輸出 close-in 抖動反而更敏感(“越濾越糟”)

根因往往集中在兩點:

窄帶伺服/PLL 時 close-in phase noise(1–100 Hz offset)會主導積分抖動,因此 OCXO 的相噪裙邊與伺服帶寬強耦合;

供電噪聲與 VCTRL 噪聲會直接調制相位噪聲,導致“器件指標”無法在系統內復現。

2. 方案目標:把系統指標翻譯成 OCXO 語言

建議把“系統目標”拆成兩條可工程化落地的路徑:

路徑 A:輸出抖動/相噪(Jitter / Phase Noise)

關注 close-in offset(1/10/100 Hz) 的相噪,而不是只看 10 kHz 單點

以系統實際 jitter integration 帶寬為準(與時鐘 IC、環路帶寬、輸出接口強相關)

路徑 B:Holdover(短中期穩定度 → TE 增長)

用 Allan deviation / stability vs τ 評估參考丟失期間的 TE 累積趨勢

同時約束 aging(天到月尺度) 與 溫度穩定(機柜也存在氣流與熱梯度)

3. 方案架構:OCXO 在 PTP/SyncE 時鐘樹里的位置

這套方案適用于以下節點類型:

PTP Grandmaster / Boundary Clock:追求伺服穩定與低 close-in 噪聲

SyncE 設備時鐘 / 線路接口:更關注 jitter / wander 預算與鏈路一致性

SSU/SEC 與關鍵基礎設施節點:需要 GNSS outage 下更穩健的 holdover

一個通用的“落地型”視角是:把 OCXO 作為本地 flywheel,由系統伺服對其進行慢速馴服;當參考源(GNSS 或網絡)不可用時,OCXO 用短中期穩定度保持輸出質量與時間誤差可控。

4. 選型規范:建議你在 RFQ/評審里寫清楚的參數

下面這份清單更適合“方案模塊”的工程交付(可直接復制進 RFQ / 技術規范)。

4.1 Holdover 相關

Allan deviation / stability vs τ(用于 TE 累積評估)

Aging:天/周/月尺度漂移控制

溫度穩定:即使室內機柜也要考慮熱梯度與氣流

4.2 相噪與抖動

1/10/100 Hz offset 相噪點(close-in)

與系統帶寬一致的 jitter integration(按最終環路與輸出接口計算/驗證)

供電/控制電壓敏感度(Supply / VCTRL susceptibility)

4.3 接口約束

輸出格式:HCMOS / clipped sine / sine(不同型號不同)

供電:3.3 V(典型)/ 可選 5 V(視型號)

warm-up:上電收斂到目標精度的動態(影響開機與切換策略)

VCTRL:控制范圍、增益、輸入阻抗與濾波要求(噪聲會直接調制相噪)

5. 參考設計要點:供電、VCTRL、布局三大紀律

5.1 供電噪聲控制(Supply noise control)

使用低噪 LDO 或經濾波的專用電源軌

穩壓器與濾波網絡靠近 OCXO 引腳放置

避免與高 di/dt 數字域共享回流路徑

5.2 VCTRL 衛生(VCTRL hygiene)——很多系統的關鍵失分點

在電信架構中,OCXO 常由控制環路(servo)馴服,因此 VCTRL 必須按“精密模擬節點”對待:

采用 RC 或有源低通,并與伺服動態匹配

VCTRL 走線遠離時鐘、SerDes、開關電源

必要時考慮專用參考地與 guard routing

調試建議:用低噪探頭觀察 VCTRL 頻譜,把異常 close-in 相噪與電源開關頻點/數字活動做相關性分析

實用計算:一階 RC 低通截止頻率

fc = 1 / (2πRC)

經驗上 fc 需要與伺服/PLL 的有效帶寬協同,避免既“跟不動”又“放噪聲進來”。

5.3 布局建議(Layout)

OCXO 區域盡量保留連續地平面

與 DC/DC、SerDes 高速通道物理隔離

輸出走線盡量短,必要時做阻抗控制以匹配下游時鐘 IC

6. 驗證閉環:四步法把“器件好看”變成“系統過標”

建議采用官方給出的四步實驗流程,這是把風險壓到量產前最有效的路徑之一:

測振蕩器獨立相噪(stand-alone)

上板測(使用最終電源樹與真實負載)

入環測(按最終產品配置的伺服/PLL 帶寬)

做 holdover 場景并記錄 time error(GNSS 丟失/參考劣化)

6.1 建議的“可交付”測試項清單(可復制)

| 測試項 | 目的 | 關鍵注意 |

| 輸出抖動(10 MHz/25 MHz/恢復時鐘) | 對齊系統接口 KPI | 在最終接口點測,不要只測器件腳 (fujicrystal.com) |

| close-in 相噪(1/10/100 Hz) | 驗證窄帶伺服下的真實噪聲 | 真實電源 + 真實負載 (fujicrystal.com) |

| holdover TE | 驗證 GNSS 丟失時的誤差增長 | 記錄溫度變化與氣流擾動 (fujicrystal.com) |

| warm-up & settling | 驗證開機/切換策略 | 觀察前幾分鐘漂移與伺服收斂 (fujicrystal.com) |

| VCTRL 頻譜(可選但強烈建議) | 定位 close-in 劣化源 | 對齊電源開關頻率/數字活動 (fujicrystal.com) |

7. 推薦器件短名單:FOC-5S-LN vs FOC-6S 如何選

本方案可直接采用 Fuji Crystal 的 telecom OCXO 家族與推薦器件作為短名單入口。

7.1 快速對比(用于方案選型分流)

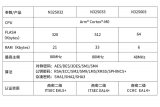

| 型號 | 封裝 | 穩定度(頁面標注) | 相噪(typ., 20 MHz) | 供電/控制 | 適合場景 |

| FOC-5S-LN | 14.7×9.6×8.2 mm | ±10 ppb(?40~+85°C);5 min warm-up 可到 ±5 ppb(@25°C) | ?126 dBc/Hz@10 Hz;?149@100 Hz;?160@1 kHz;?164@10 kHz | 3.3 V(5 V 可選);VCO 0–3.3 V 正斜率 | 高密度邊緣節點、1588 邊界時鐘、對 ultra-low phase noise 更敏感的平臺 (fujicrystal.com) |

| FOC-6S | 25.4×22.1×11.0 mm | ±10 ppb(0~+70°C) | ?115 dBc/Hz@10 Hz;?130@100 Hz;?140@1 kHz;?150@10 kHz | 3.3 V(5 V 可選);VCO 0–2.8 V 正斜率 | 傳統板卡/機框設備、同步卡、回傳與更從容的集成空間 (fujicrystal.com) |

7.2 一句話決策

你更在意 更小封裝 + 更低相噪(并且平臺高密度):優先 FOC-5S-LN

你更在意 穩健集成與經典板卡適配:優先 FOC-6S

8. 常見問題(FAQ)

Q1:PTP/SyncE 節點最該優先的 OCXO 指標是什么?

優先:holdover 穩定度(Allan deviation/stability vs τ)+ close-in 相噪 + 供電/VCTRL 敏感度,并確保測量帶寬與系統伺服/PLL 帶寬一致。

Q2:為什么“器件相噪數據很好”,上板后反而變差?

高概率是電源噪聲或 VCTRL 噪聲引入了額外調制。建議把 VCTRL 當成精密模擬節點做濾波與隔離,并在調試時直接觀測 VCTRL 頻譜與相噪惡化的相關性。

Q3:伺服/PLL 帶寬該怎么取舍?

一般規律:帶寬更窄可抑制參考源短期噪聲,但過窄會導致收斂慢、對瞬態更敏感;帶寬更寬可快速跟蹤參考,但可能引入參考噪聲并增加 close-in 抖動風險。建議從目標 jitter/MTIE/TDEV 出發,結合實測相噪做積分/仿真,再在最終電源與 VCTRL 條件下驗證。

-

OCXO

+關注

關注

0文章

56瀏覽量

15401 -

IEEE1588

+關注

關注

1文章

23瀏覽量

16922 -

邊界時鐘

+關注

關注

0文章

3瀏覽量

5783 -

SyncE器件

+關注

關注

0文章

2瀏覽量

5378 -

PTP

+關注

關注

0文章

97瀏覽量

9785

發布評論請先 登錄

電信同步“底盤”怎么選:Telecom 級 OCXO 在 PTP/SyncE 與關鍵基礎設施里的工程落地

一頁打通電信同步與接收機前端:OCXO、TCXO 與 70–300MHz IF SAW 的選型與驗證路徑

從天線到主時鐘:SAW 濾波器 + TCXO + OCXO 的系統級時頻棧(GNSS/衛星/電信)

TCXO 在同步、GNSS 與衛星通信中的中堅角色:從板級參考到射頻模塊

從系統視角選時鐘:一張“應用分層地圖”講清 TCXO / OCXO / SAW 的正確打開方式

軍工、航天與電信主時鐘用 OCXO:L1 級時序基準怎么選?

時鐘振蕩器選型與排障:從抖動預算到PCB電源的工程實操(含延伸閱讀)

華為超節點互聯技術引領AI基礎設施新范式

WLAN/WiMAX 時鐘選型:TCXO/VCXO/OCXO 如何影響 EVM/CFO(含兩張對比圖)

網絡與存儲時鐘設計實戰:156.25 MHz / 100 MHz 參考時鐘、抖動預算與 Pin-to-Pin 選型(附 BOM)

國民技術安全芯片筑牢關鍵信息基礎設施安全防線

PTP/SyncE 與關鍵基礎設施節點的 OCXO 參考設計(低抖動 + 強 Holdover + 易驗證)

PTP/SyncE 與關鍵基礎設施節點的 OCXO 參考設計(低抖動 + 強 Holdover + 易驗證)

評論