以下文章來源于郝旭帥電子設計團隊,作者郝旭帥

DDRX SDRAM外部接口數據傳輸率需要不斷提高(從DDR到DDR5),內存芯片內部的DRAM存儲單元(電容陣列)的物理訪問速度有上限,無法隨著接口速度的線性增長。

預取(Prefetch)技術是DDR SDRAM實現高速數據傳輸的關鍵技術之一。它的基本思想是:在內存核心(存儲陣列)和外部數據總線之間設置一個緩沖區,內存核心工作在一個相對較低的頻率,而數據總線工作在一個較高的頻率,通過一次從存儲陣列中讀取多個數據(預取),然后在外部數據總線上通過多個時鐘周期(或雙沿傳輸)將數據依次傳輸出去,從而提升數據傳輸率。

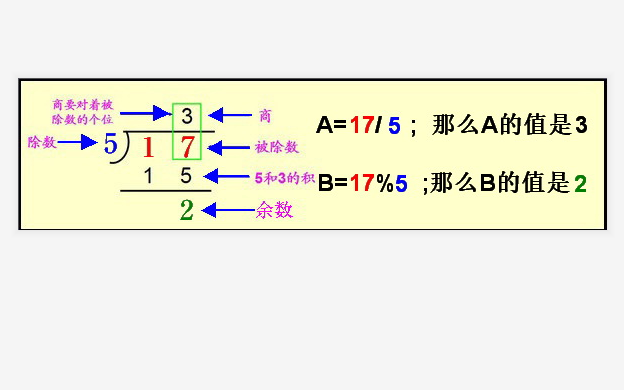

具體來說,DDR SDRAM的預取長度(Prefetch Length)是指每次從存儲陣列中讀取的數據位數與每次對外傳輸的數據位數的比值。例如,對于DDR1,預取長度是2n;DDR2是4n;DDR3是8n;DDR4也是8n(但通過Bank Group分組來模擬更高的預取);DDR5則是16n(但通過兩個獨立的通道實現)。

下面我們詳細說明:

1. DDR1 (2n Prefetch) 內存核心(存儲陣列)的工作頻率是外部數據傳輸頻率的一半。例如,對于DDR-400,外部數據傳輸頻率是400MT/s,內存核心頻率是200MHz。 每次從存儲陣列中讀取2位數據(針對每個數據引腳),然后在外部數據總線上通過兩個時鐘邊沿(上升沿和下降沿)將這兩位數據依次傳輸出去。 這樣,在內存核心工作頻率不變的情況下,外部數據傳輸率翻倍。

2. DDR2 (4n Prefetch) 內存核心頻率進一步降低,為外部數據傳輸頻率的四分之一。例如,DDR2-800,外部數據傳輸頻率為800MT/s,內存核心頻率為200MHz。 每次從存儲陣列中讀取4位數據,然后在外部數據總線上通過4個時鐘邊沿(兩個時鐘周期,因為每個周期有兩個邊沿)將這4位數據依次傳輸出去。 這樣,在相同的內存核心頻率下,DDR2的數據傳輸率是DDR1的兩倍(因為預取長度翻倍)。

3. DDR3 (8n Prefetch) 內存核心頻率為外部數據傳輸頻率的八分之一。例如,DDR3-1600,外部數據傳輸頻率為1600MT/s,內存核心頻率為200MHz。 每次從存儲陣列中讀取8位數據,然后在外部數據總線上通過8個時鐘邊沿(4個時鐘周期)將這8位數據依次傳輸出去。 這樣,在相同的內存核心頻率下,DDR3的數據傳輸率是DDR2的兩倍,是DDR1的四倍。

上述結構為ddr3 sdram 內部結構圖。8bank,16krow,1kcol,x16.

按照我們正常的理解:

每一個bank應該有16k行,1k列,每個存儲空間可以存儲16bit。

但是實際上我們通過結構圖看到的是:16k行,128列,每個存儲空間可以存儲128bit。

那也就是說:每次讀寫都是128位,而接口的寬度是16,相當于讀取出來了8個我們認為的存儲地址。

所以ddr3的內部就可以以接口速率的1/8運行。

4. DDR4 (8n Prefetch with Bank Group) DDR4也使用8n預取,但是引入了Bank Group(存儲體分組)的概念。每個Bank Group可以獨立操作,從而可以在不同的Bank Group之間交替執行操作,類似于提高了并行度,從而在保持8n預取的情況下進一步提升了性能。 例如,DDR4-3200,外部數據傳輸頻率為3200MT/s,內存核心頻率為400MHz(因為8n預取,核心頻率為3200/8=400MHz)。注意,這里核心頻率比DDR3的例子高,因為DDR4的速度更高,但預取倍數相同。

5. DDR5 (16n Prefetch) DDR5將預取長度提升到16n,但這是通過兩個獨立的通道(每個通道40位,其中32位數據位和8位ECC位)來實現的。實際上,每個通道的預取長度可以認為是8n,但整體上,內存核心一次提供16n的數據,然后通過兩個通道傳輸。 例如,DDR5-6400,每個通道的數據傳輸率是3200MT/s,整體是6400MT/s。內存核心頻率為400MHz(假設每個通道是8n預取,那么每個通道的核心頻率為3200/8=400MHz,兩個通道共享核心陣列,但可以交錯訪問)。

預取技術的優點:

允許內存核心工作在相對較低的頻率,從而降低功耗和制造難度(因為存儲陣列的訪問速度難以提升)。

通過提高預取長度,可以在不提高內存核心頻率的情況下增加外部數據傳輸率。

預取技術的缺點:

預取長度增加會導致訪問延遲(Latency)的增加,因為每次訪問需要從存儲陣列中讀取更多的數據,而且如果訪問模式不是順序的(例如隨機訪問),那么預取的數據可能用不上,造成浪費。

為了緩解這個問題,DDR4和DDR5引入了Bank Group,通過并行操作來隱藏延遲。

總結:

預取技術是DDR SDRAM實現高速數據傳輸的核心技術,它通過降低內存核心工作頻率并提高每次訪問的數據量來實現更高的數據傳輸率。隨著DDR代際的升級,預取長度不斷增加,同時通過其他技術(如Bank Group、多通道)來克服預取帶來的延遲增加問題。

-

SDRAM

+關注

關注

7文章

458瀏覽量

57794 -

接口

+關注

關注

33文章

9575瀏覽量

157527 -

存儲

+關注

關注

13文章

4866瀏覽量

90218 -

DDR

+關注

關注

11文章

760瀏覽量

69486

原文標題:DDRX SDRAM中的預取技術說明

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DDRx的關鍵技術介紹(上)

DDRx的關鍵技術介紹(中)

請問如何理解C6678中對預取數據的描述?

可以在不關閉緩存的情況下關閉FMC預取器嗎?

片上多處理器中基于步長和指針的預取

SDRAM設計詳細說明

一種幫助線程預取質量的實時在線評價方法

面向系統的程序基本塊指令預取技術

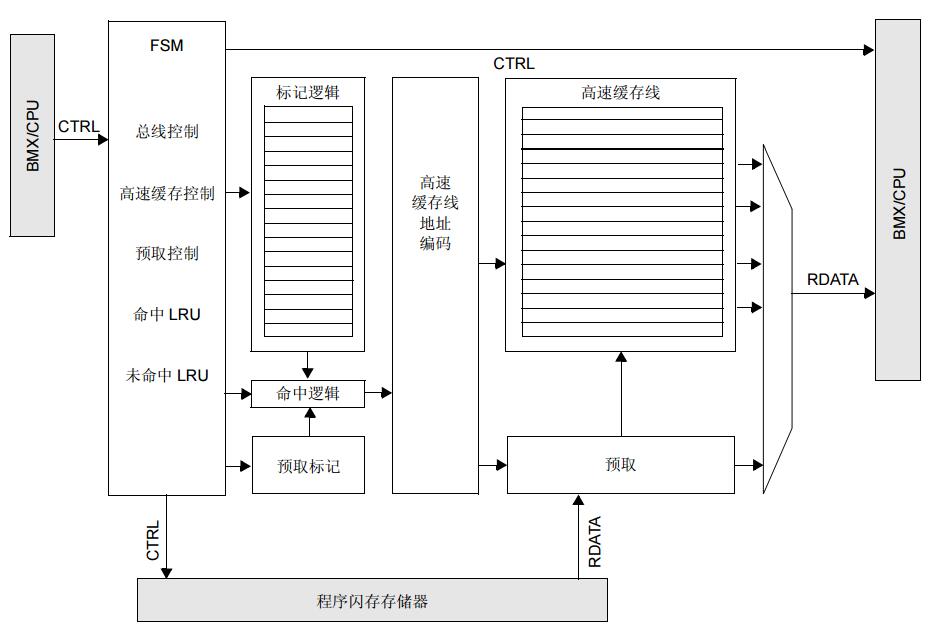

PIC32MX系列參考手冊之預取高速緩存模塊

DDRX SDRAM中的預取技術說明

DDRX SDRAM中的預取技術說明

評論