以下文章來源于郝旭帥電子設計團隊,作者郝旭帥

在進行電子系統設計時,我們經常會用到SDRAM(SDR SDRAM或者DDRX SDRAM)作為緩沖單元,但是如何評估SDRAM的有效帶寬呢(評估有效帶寬才能夠了解當前緩沖單元以及驅動方式能否滿足我們的設計需求)?

SDRAM的“有效帶寬”指的是在實際系統中,扣除所有必要開銷后,能夠用于數據傳輸的實際可用帶寬。它總是顯著低于理論峰值帶寬。

理論帶寬

公式:

理論峰值帶寬 = (時鐘頻率 × 數據總線位寬 × 數據傳輸次數(每個時鐘周期傳輸的bit數:SDR為1,DDR為2)) / 8

單位通常是 字節/秒(B/s) 或 GB/s。

舉例:

一片 DDR3-1600,位寬為 16位(2字節);

核心時鐘頻率:800 MHz

數據傳輸率(DRAM Frequency):1600 MT/s(每秒百萬次傳輸)

理論峰值帶寬 = 800 × 10? × 2 x 16 /2 Bytes = 3200 MB/s = 3.2 GB/s

這個值通常被芯片廠商和市場宣傳所使用。

有效帶寬

SDRAM在進行通信時,是無法每個時鐘周期都用于進行數據讀寫的。

一次完整的訪問通常包含三步:

激活(Activate): 將指定Bank的指定Row數據送到該Bank的“行緩沖器”。此操作功耗較高,延遲較大。

讀/寫(Read/Write): 在行緩沖器中,根據列地址進行精細的讀或寫操作。可以連續進行多個讀/寫(突發傳輸)。

預充電(Precharge): 操作完成后,必須將行緩沖器的數據寫回原Row,并關閉該行,為激活新的行做準備。

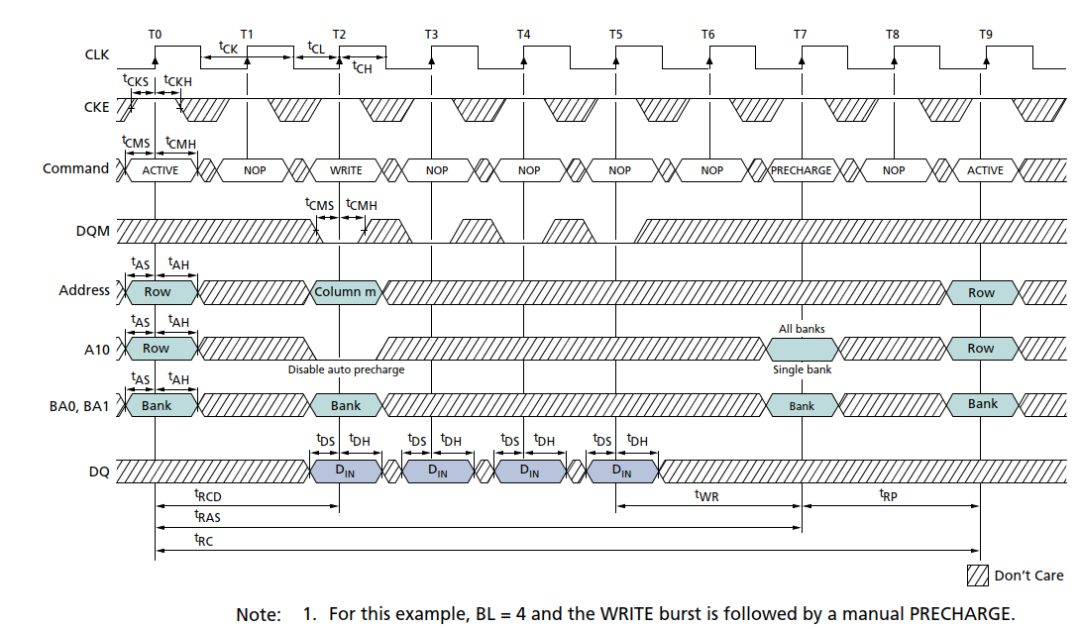

下面以SDR SDRAM為例:

在上述時序中可以清楚的看到:為了將四個數據寫入到SDRAM中使用了九個周期(包括了激活、寫入、關閉等)。

那么也就是說:有效帶寬只是理論帶寬的一半不到(4/9).

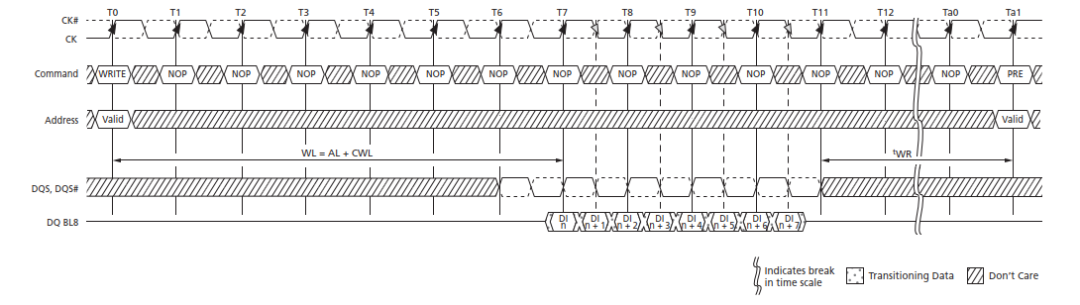

下面給出DDR3的波形圖:

與SDR SDRAM類似。

SDRAM在工作時,還需要定時進行刷新操作以避免數據丟失。所以有效帶寬就會更低。

提高有效帶寬的幾種方式

在此只是根據單個芯片進行說明(關于多芯片擴位寬以及RANK,在此不再說明)。

1. 增大突發長度

在每次突發讀寫中,無論突發長度為多少,前面的激活和后面的預充電所占用的時間是相同的。

例:激活4+讀寫4+預充電4:那么有效帶寬為三分之一;如果激活4+讀寫8+預充電4:那么有效帶寬為二分之一。

說明:在SDR SDRAM中經常采用此方法進行提高有效帶寬(可以利用頁突發,幾乎可以達到百分之百)。在DDRX SDRAM中取消了頁突發,并且突發長度一般固定,所以此方法在DDRX SDRAM中失效。

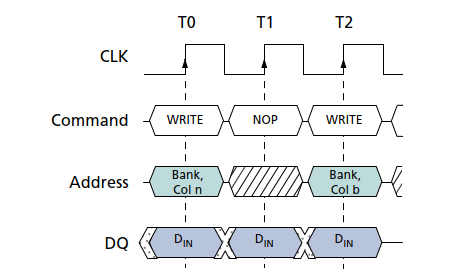

2. 連續突發訪問

在SDRAM中,如果第一次操作和第二次操作處于同一個bank的同一行,那么第一次操作可以不用關閉,第二次操作可以不用打開(節省了一次關閉,一次激活)。

以SDR SDRAM的寫入為例:

第一次寫入沒有關閉,第二次寫入沒有激活。

在電子設計開發時,如果采用的是DDRX SDRAM,一般主控芯片會有IP 控制器,不用我們直接操作DDRX SDRAM。在配置時,注意一個選項:命令的順序。

建議選擇可以優化(重新排列序號)。

例:第一次操作N行,第二次操作M行,第三次操作N行。因為第一次和第二次處于不同行,所以第一次關閉了以后才可以激活第二次操作(完成上述操作需要三次激活、三次操作、三次關閉)。如果我們可以將第三次操作和第二次操作對調執行順序,那么只需要兩次激活、三次操作、兩次關閉。

操作的數據量沒有改變,但是縮短了需要的時間。

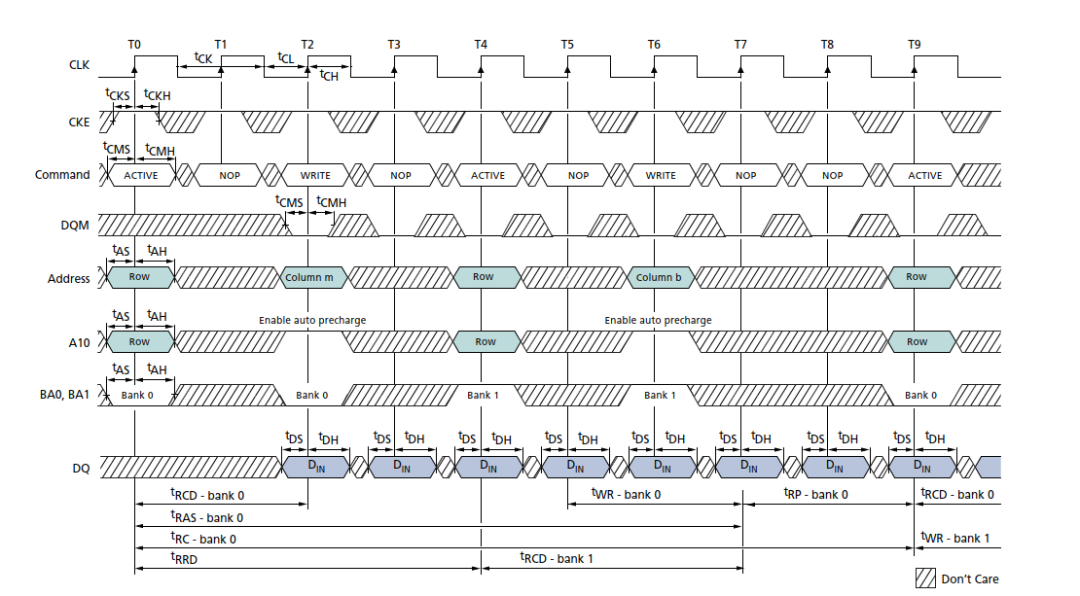

3. 改變地址映射

在SDRAM中,如果第一次操作和第二次操作處于不同bank時,那么可以利用第一次操作關閉的時間來激活第二次操作。

以SDR SDRAM為例:

我們在使用SDRAM在進行緩沖時,一般是使用連續的一塊地址(邏輯地址),如果邏輯地址對應的是:BANK ROW COL,那么將會出現用完ABANK的第一行,就會用ABANK的第二行(在同一個bank中,無法實現第一次操作的關閉和第二次操作的激活利用同一段時間)。如果邏輯地址對應的是:ROW BANK COL,那么將會出現用完ABANK的第一行,就會用BBANK的第一行(此時第一次操作的關閉和第二次操作的激活利用的是同一段時間)。

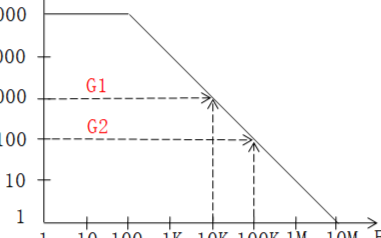

評估有效帶寬

當設計完控制器(IP控制器或自己設計控制器)后,可以自己寫一些邏輯進行測試有效帶寬。

例:統計一秒鐘能夠寫入多少字節,統計一秒鐘能夠讀出多少字節。

說明:

1. 有效帶寬和地址的改變規律有一定的關系。

2. 測量時,應該保證最大限度的給予命令或命令(反例:控制器能夠五個周期寫入一個數據,測量者10個周期才給與一個數據)。

設計注意事項

務必保證有效帶寬在你的設計需求之上,否則項目就會出現崩盤。

-

SDRAM

+關注

關注

7文章

458瀏覽量

57800 -

帶寬

+關注

關注

3文章

1048瀏覽量

43532 -

時鐘

+關注

關注

11文章

1998瀏覽量

135199

原文標題:SDRAM有效帶寬解析與估算

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

SDRAM控制器的設計——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

有效的歐盟ErP認證是如何評估的?

采樣寬帶寬模擬信號的AD9684評估板

自相似業務流的有效帶寬

SDRAM設計詳細說明

SDRAM內存基礎知識

DRAM、SDRAM及DDR SDRAM之間的概念詳解

FPGA讀寫SDRAM的實例和SDRAM的相關文章及一些SDRAM控制器設計論文

如何評估SDRAM的有效帶寬

如何評估SDRAM的有效帶寬

評論