深入剖析SN74AC138-Q1:3 - 8解碼器的設計與應用指南

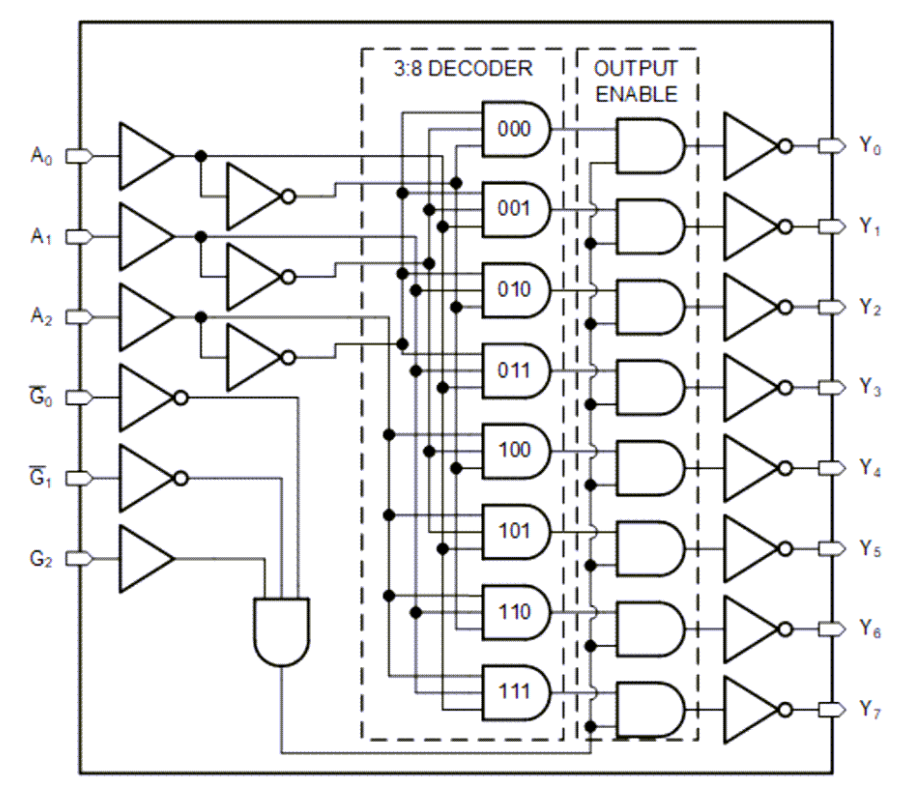

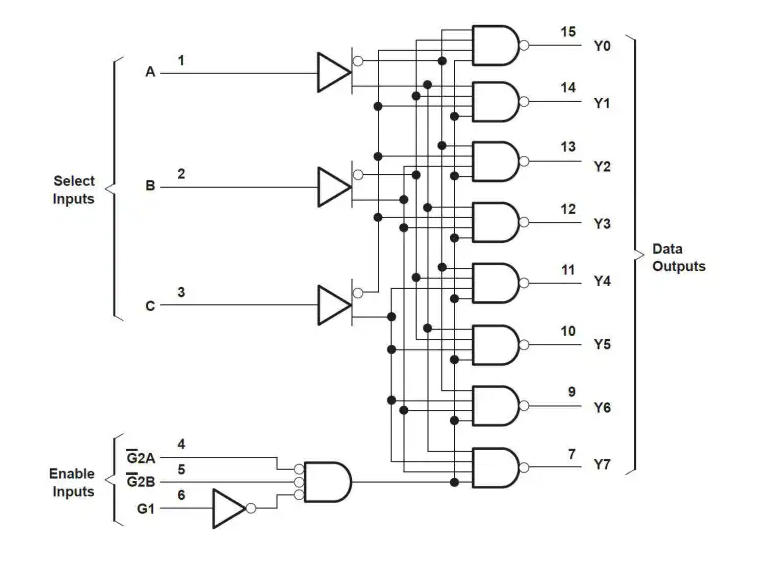

在電子設計領域,解碼器是一種常見且重要的邏輯器件,它能夠將輸入的二進制代碼轉換為特定的輸出信號。今天我們要深入探討的是德州儀器(TI)的SN74AC138 - Q1,一款3 - 8解碼器/解復用器,它在眾多電子系統中發揮著關鍵作用。

文件下載:sn74ac138-q1.pdf

一、規格參數

1. 絕對最大額定值

絕對最大額定值規定了器件在不被永久損壞的前提下能夠承受的最大應力。例如,電源電壓范圍(VCC)為 - 0.5V至7V,輸入和輸出電壓范圍(VI和VO)為 - 0.5V至VCC + 0.5V。需要特別注意的是,超出這些額定值可能會導致器件永久性損壞,即使短暫超出推薦工作條件,也可能影響器件的可靠性、功能性和壽命。

| 參數 | 描述 | 最小值 | 最大值 | 單位 |

|---|---|---|---|---|

| VCC | 電源電壓范圍 | -0.5 | 7 | V |

| VI | 輸入電壓范圍 | -0.5 | VCC + 0.5V | V |

| VO | 輸出電壓范圍 | -0.5 | VCC + 0.5V | V |

| ...... | ...... | ...... | ...... | ...... |

2. ESD額定值

靜電放電(ESD)是電子器件的一大潛在威脅,SN74AC138 - Q1在這方面有明確的額定值。人體模型(HBM)下為±2000V(AEC Q100 - 002標準,HBM ESD分類等級2),帶電設備模型(CDM)下為±1000V(AEC Q100 - 011標準,CDM ESD分類等級C4B)。在實際操作中,必須采取適當的靜電防護措施,以避免ESD對器件造成損害。

3. 推薦工作條件

推薦工作條件是確保器件正常、穩定工作的參數范圍。電源電壓(VCC)推薦范圍為1.5V至6V,不同的VCC對應著不同的高、低電平輸入電壓要求。例如,當VCC = 1.5V時,高電平輸入電壓(VIH)最小值為1.2V,低電平輸入電壓(VIL)最大值為0.3V。在設計電路時,務必使器件工作在這些推薦條件下。

二、器件特性

1. 平衡CMOS推挽輸出

SN74AC138 - Q1采用平衡CMOS推挽輸出結構,意味著器件能夠吸收和提供相似的電流。這種輸出結構在驅動輕負載時能夠產生快速的邊沿,但同時也可能會引發振鈴現象。因此,在設計電路板時,需要充分考慮布線和負載條件,避免出現振鈴問題。此外,要嚴格控制輸出功率,防止因過流而損壞器件,必須始終遵循絕對最大額定值中定義的電氣和熱限制。

2. 標準CMOS輸入

標準CMOS輸入具有高阻抗的特點,通常可以用一個電阻與輸入電容并聯的模型來表示。在計算最壞情況下的電阻時,可以使用絕對最大額定值中的最大輸入電壓和電氣特性中的最大輸入泄漏電流,通過歐姆定律(R = V ÷ I)來計算。需要注意的是,輸入信號必須快速在有效邏輯狀態之間轉換,否則會導致功耗過大甚至引發振蕩。在實際應用中,絕對不要讓標準CMOS輸入處于浮空狀態,未使用的輸入必須連接到VCC或GND。

3. 可焊側翼

部分封裝的SN74AC138 - Q1具備可焊側翼,這種設計有助于提高焊接后的側面潤濕性,使得QFN封裝在自動光學檢測(AOI)中更易于檢查。可焊側翼可以是凹陷或階梯狀的,為焊料提供了額外的附著面積,從而可靠地形成側面焊腳。

4. 鉗位二極管結構

器件的輸入和輸出都配備了正負極鉗位二極管。然而,需要特別注意的是,電壓超過絕對最大額定值表中規定的值可能會損壞器件。在滿足輸入和輸出鉗位電流額定值的前提下,輸入和輸出電壓額定值可以適當超出。

三、功能模式

| SN74AC138 - Q1的功能模式由三個使能輸入和三個二進制選擇輸入共同決定。通過這些輸入的不同組合,可以選擇八個輸出線中的一個,被選中的輸出線為低電平,其余輸出線為高電平。具體的功能表如下: | 輸入(G2、G1、G0、A2、A1、A0) | 輸出(Y0 - Y7) |

|---|---|---|

| X X H X X X | H H H H H H H H | |

| L X X X X X | H H H H H H H H | |

| X H X X X X | H H H H H H H H | |

| H L L L L L | L H H H H H H H | |

| ...... | ...... |

四、應用與實現

1. 典型應用示例

在一個使用5位輸入選擇32個輸出中的1個的應用中,可以使用四個SN74AC138 - Q1 3 - 8解碼器。此時,需要一個外部反相器來完成整個電路。被選中的輸出為低電平,其余輸出為高電平。

2. 設計要求

- 電源考慮:確保所需的電源電壓在推薦工作條件規定的范圍內,電源電壓決定了器件的電氣特性。正電壓電源必須能夠提供足夠的電流,包括所有輸出所需的總電流、最大靜態電源電流(ICC)以及開關所需的瞬態電流。同時,要注意器件的功耗和熱增加,可以參考相關的應用報告進行計算。

- 輸入考慮:輸入信號必須超過VIL(max)才能被視為邏輯低電平,超過VIH(min)才能被視為邏輯高電平,且不能超過絕對最大額定值中的最大輸入電壓范圍。未使用的輸入必須連接到VCC或地,推挽輸出不能直接連接在一起,以免產生過大電流損壞器件。

3. 詳細設計步驟

- 添加去耦電容:從VCC到GND添加一個去耦電容,電容應盡可能靠近器件,并且在電氣上靠近VCC和GND引腳。

- 控制輸出電容負載:確保輸出的電容負載 ≤ 50pF,可通過提供短而合適尺寸的走線來實現。

- 控制輸出電阻負載:確保輸出的電阻負載大于(VCC / IO(max))Ω,以防止違反絕對最大額定值中的最大輸出電流。

- 考慮熱問題:雖然邏輯門的熱問題通常不是主要關注點,但可以使用相關應用報告中的步驟來計算功耗和熱增加。

4. 電源供應建議

電源電壓可以在推薦工作條件規定的最小和最大電源電壓額定值之間選擇。在啟動時,電源應在規定的上電斜坡速率范圍內上升。每個VCC端子都應配備一個良好的旁路電容,對于SN74AC138Q1,建議使用0.1μF的旁路電容,為了抑制不同頻率的噪聲,可以并聯多個旁路電容。

5. 布局指南

- 旁路電容放置:旁路電容應靠近器件的正電源端子,提供電氣上短的接地返回路徑,使用寬走線以最小化阻抗,并盡量將器件、電容和走線放置在電路板的同一側。

- 信號走線幾何形狀:信號走線寬度為8mil至12mil,長度小于12cm以最小化傳輸線效應,避免信號走線出現90°角,在信號走線下方使用完整的接地平面,并對信號走線周圍的區域進行填充。對于長度超過12cm的走線,使用阻抗控制走線,在輸出附近使用串聯阻尼電阻進行源端匹配,避免分支走線,如果必須分支,應單獨緩沖信號。

總結

SN74AC138 - Q1作為一款功能強大的3 - 8解碼器/解復用器,在電子設計中具有廣泛的應用前景。通過深入了解其規格參數、器件特性、功能模式以及應用實現方法,電子工程師可以更好地利用這款器件,設計出更加穩定、可靠的電子系統。在實際設計過程中,務必嚴格遵循器件的各項參數和設計指南,以確保系統的性能和可靠性。你在使用類似解碼器的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗。

-

電子設計

+關注

關注

42文章

1681瀏覽量

49848

發布評論請先 登錄

Texas Instruments SN74AC138-Q1 3線至8線反相解碼器/解復用器數據手冊

Texas Instruments SN74AHCT138/SN74AHCT138Q-Q1解復用器/解碼器數據手冊

深入剖析SN74AC138 - Q1:3 - 8解碼器的設計與應用指南

深入剖析SN74AC138 - Q1:3 - 8解碼器的設計與應用指南

評論