SN74LV8T151-EP數據選擇器/多路復用器的設計與應用

在電子設計領域,數據選擇器/多路復用器是常見且關鍵的器件。今天我們就來深入探討德州儀器(TI)的SN74LV8T151-EP這款產品,從其規格參數、特性到實際應用設計,為大家展開詳細介紹。

文件下載:sn74lv8t151-ep.pdf

1. 產品概述

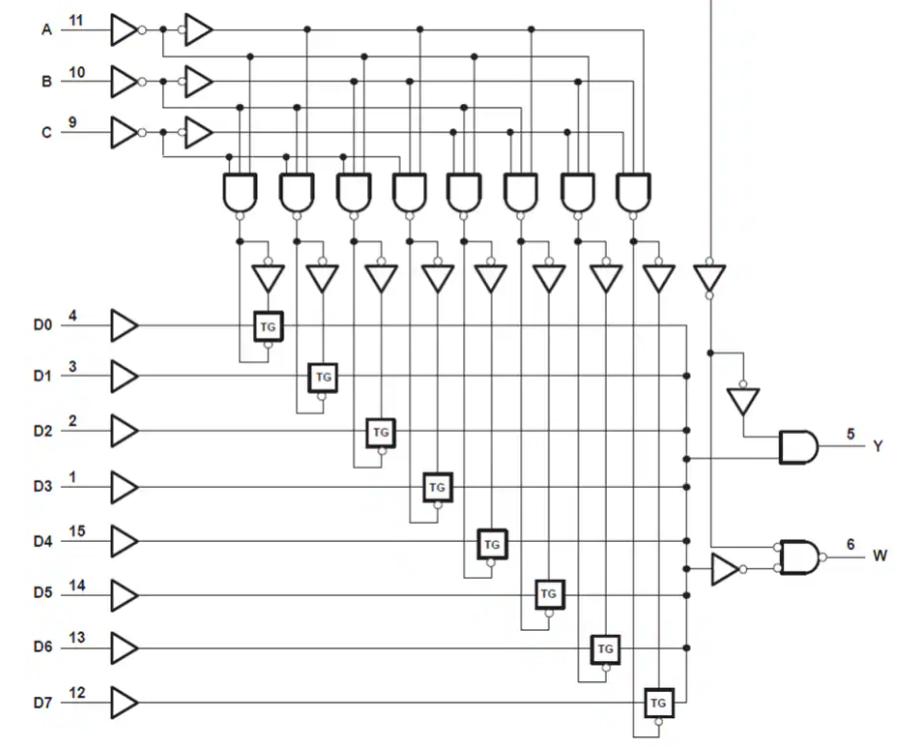

SN74LV8T151-EP是一款數據選擇器/多路復用器,能實現對八個數據源的全二進制解碼選擇。它采用PW(TSSOP,16)封裝,封裝尺寸為5mm x 6.4mm,主體尺寸為5mm x 4.4mm。

2. 規格參數

2.1 絕對最大額定值

這規定了器件在特定條件下能承受的極限參數。例如,VCC電源電壓范圍為 -0.5V 到 7V,輸入電壓范圍(VI)同樣是 -0.5V 到 7V 等。需要注意的是,超出這些絕對最大額定值可能會導致器件永久性損壞,即使短暫超出推薦工作條件但在絕對最大額定值內,雖可能不造成損壞,但器件可能無法完全正常工作,還會影響可靠性、功能、性能并縮短使用壽命。

2.2 ESD 額定值

靜電放電(ESD)是電子器件的一大威脅。該器件的人體模型(HBM)ESD 額定值為 ±2000V,帶電設備模型(CDM)為 ±1000V。JEDEC 文檔指出,500V HBM 和 250V CDM 可在標準 ESD 控制流程下實現安全制造。

2.3 推薦工作條件

明確了器件正常工作的最佳參數范圍。如 VCC 電源電壓推薦為 1.8V 到 5.5V,輸入電壓(VI)為 0V 到 5.5V 等。不同的電源電壓對應著不同的高電平輸入電壓(VIH)和低電平輸入電壓(VIL)要求,這在實際設計中需要嚴格遵循。

2.4 電氣特性

包含了眾多參數,如輸出高電平電壓(VOH)、輸出低電平電壓(VOL)、輸入電流(II)、電源電流(ICC)等。這些參數在不同的測試條件和電源電壓下有不同的取值范圍,為電路設計提供了精確的數據參考。

2.5 傳播延遲時間

衡量了信號從輸入到輸出的延遲情況。不同的輸入輸出組合、負載電容和電源電壓下,傳播延遲時間(TPLH、TPHL)有所不同。例如,在 CL = 15pF、Vcc = 1.8V 時,從 A、B、C 到 Y 的 TPLH 典型值為 19.1ns,TPHL 典型值為 26.7ns。

3. 典型特性

通過一系列圖表展示了器件在不同條件下的典型特性,如電源電流隨輸入電壓和電源電壓的變化、輸出電壓與電流在高電平和低電平狀態下的關系等。這些特性曲線能幫助工程師更好地理解器件的性能,在設計中進行合理的參數選擇和優化。

4. 詳細特性描述

4.1 平衡 CMOS 推挽輸出

該器件采用平衡 CMOS 推挽輸出結構,意味著它能吸收和源出相似的電流。不過,其驅動能力在輕負載下可能產生快速邊沿,因此在布線和負載條件設計時要考慮防止振鈴。同時,要注意限制輸出功率,避免因過流損壞器件,且未使用的推挽 CMOS 輸出必須保持斷開。

4.2 LVxT 增強輸入電壓

SN74LV8T151-EP 屬于 TI 的 LVxT 邏輯器件家族,具備集成電壓電平轉換功能。其輸入電壓閾值降低,支持向上轉換;輸入能耐受高達 5.5V 的信號,支持向下轉換。輸入信號必須在規定的 VIH(MIN) 和 VIL(MAX) 范圍內,以確保正確的邏輯狀態。未使用的輸入必須連接到有效的高或低電壓電平,可通過上拉或下拉電阻實現。

4.2.1 向上轉換

能將較低電壓的輸入信號轉換為較高電壓的輸出信號。例如,在 5V 電源下,標準 CMOS 輸入的 VIH(MIN) 為 3.5V,而該器件僅為 2V,可實現從 2.5V 到 5V 信號的向上轉換。

4.2.2 向下轉換

可將較高電壓的輸入信號轉換為較低電壓的輸出信號。如在 1.8V VCC 下,能將 5.0V、3.3V 或 2.5V 的標準 CMOS 輸入信號向下轉換為 1.8V CMOS 信號。

4.3 鉗位二極管結構

輸出端有正負鉗位二極管,輸入端只有負鉗位二極管。但要注意,超出絕對最大額定值表中規定的電壓可能會損壞器件,不過在遵守輸入和輸出鉗位電流額定值的情況下,輸入和輸出電壓額定值可以適當超出。

5. 應用與實現

5.1 應用信息

該器件主要用于從八個數據源中選擇一個數據,在數據選擇和多路復用場景中發揮重要作用。

5.2 典型應用

5.2.1 設計要求

- 電源考慮:電源電壓要在推薦工作條件范圍內,正電源需能提供足夠的電流,包括所有輸出的總電流、最大靜態電源電流和開關所需的瞬態電流;地要能吸收相應的電流。同時,要注意負載電容不宜超過 50pF,負載電阻需滿足 (R{L} ≥V{O} / I_{O}) 。

- 輸入考慮:輸入信號必須在規定的電壓范圍內,未使用的輸入要連接到 VCC 或地,可根據情況使用上拉或下拉電阻,電阻值受多種因素限制,通常推薦 10kΩ。

- 輸出考慮:正電源電壓決定輸出高電平電壓,地電壓決定輸出低電平電壓。推挽輸出不能直接連接,同一器件中相同輸入信號的兩個通道可并聯以增強輸出驅動能力,未使用的輸出可浮空,不能直接連接到 VCC 或地。

5.2.2 詳細設計步驟

- 添加去耦電容,放置在靠近器件且與 VCC 和 GND 引腳電氣距離近的位置。

- 確保輸出端的電容負載 ≤ 50pF,可通過合理設計走線實現。

- 保證輸出端的電阻負載大于 (VCC / IO(max))Ω。

- 可通過相關應用報告中的步驟計算功耗和熱增加。

5.3 電源供應建議

電源電壓應在推薦的最小和最大額定值之間,每個 VCC 端子都應配備旁路電容,推薦使用 0.1μF 電容,也可并聯多個電容以抑制不同頻率的噪聲,且電容應盡量靠近電源端子安裝。

5.4 布局設計

5.4.1 布局準則

- 旁路電容應靠近器件的正電源端子放置,提供短的接地返回路徑,使用寬走線以減小阻抗,盡量將器件、電容和走線布置在電路板的同一側。

- 信號走線寬度為 8mil 到 12mil,長度小于 12cm 以減少傳輸線效應,避免 90° 拐角,在信號走線下方使用完整的接地平面,對信號走線周圍區域進行接地填充。對于長度超過 12cm 的走線,應使用阻抗控制走線,在輸出端附近使用串聯阻尼電阻進行源端端接,避免分支,對必須分支的信號進行單獨緩沖。

5.4.2 布局示例

文檔中給出了多種布局示例,包括不同封裝的旁路電容放置、走線拐角處理和阻尼電阻放置等,為實際設計提供了直觀的參考。

6. 器件與文檔支持

TI 提供了豐富的開發工具和文檔支持,包括相關的應用報告、接收文檔更新通知的方式、技術支持論壇等。同時,要注意該集成電路易受 ESD 損壞,需采取適當的防護措施。

總之,SN74LV8T151-EP 是一款功能強大的數據選擇器/多路復用器,但在實際應用中,工程師需要根據其規格參數、特性和設計要求進行精心設計,以確保電路的性能和可靠性。大家在使用過程中遇到過哪些問題呢?歡迎在評論區分享交流。

-

多路復用器

+關注

關注

9文章

1057瀏覽量

66768 -

數據選擇器

+關注

關注

2文章

173瀏覽量

16936

發布評論請先 登錄

Texas Instruments SN74LV8T151-EP數據選擇器多路復用器數據手冊

Texas Instruments SN74LV8T157-EP數據選擇器/多路復用器數據手冊

SN74LV8T151-EP數據選擇器/多路復用器的設計與應用

SN74LV8T151-EP數據選擇器/多路復用器的設計與應用

評論