深度剖析ENC28J60:獨立以太網控制器的設計與應用指南

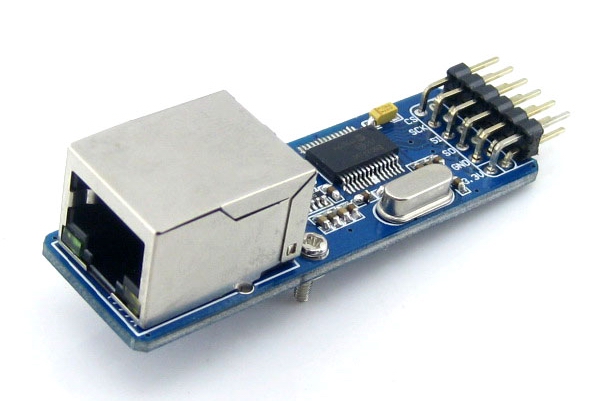

在當今數字化時代,以太網連接在各類電子設備中扮演著至關重要的角色。ENC28J60作為一款具備SPI接口的獨立以太網控制器,以其獨特的功能和廣泛的適用性,成為眾多電子工程師的首選。本文將對ENC28J60進行全面深入的剖析,涵蓋其特性、外部連接、內存組織、SPI接口等多個方面,旨在為工程師們提供一份詳盡的設計與應用指南。

文件下載:ENC28J60T-I ML.pdf

一、ENC28J60概述

ENC28J60專為與具備SPI接口的控制器搭配使用而設計,能夠無縫融入各類以太網網絡環境。它嚴格遵循IEEE 802.3規范,可全面兼容10/100/1000Base - T網絡,具備多種實用特性。

- 核心特性:集成了MAC和10Base - T PHY,支持單10Base - T端口,具備自動極性檢測與校正功能,支持全雙工和半雙工模式。同時,它還擁有可編程的自動重傳、填充和CRC生成功能,以及自動拒絕錯誤數據包的能力,借助SPI接口,時鐘速率最高可達20 MHz。

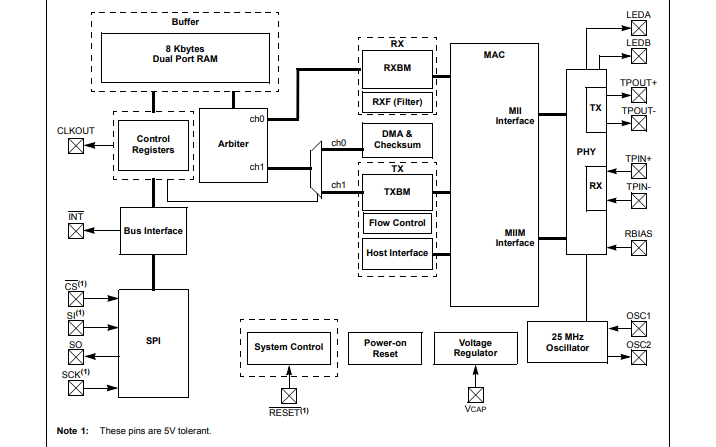

- 功能模塊:主要由SPI接口、控制寄存器、雙端口RAM緩沖器、仲裁器、總線接口、MAC模塊和PHY模塊等七大功能模塊構成。此外,還配備了振蕩器、片上穩壓器、電平轉換器等輔助模塊,以提供5V容忍的I/O和系統控制邏輯。

二、外部連接設計要點

振蕩器配置

- 晶體振蕩器:ENC28J60通常需搭配25 MHz的并聯諧振晶體,連接至OSC1和OSC2引腳。使用串聯諧振晶體可能導致頻率超出制造商規定范圍。

- 外部時鐘源:也可采用外部時鐘源連接至OSC1引腳,但需注意時鐘占空比限制,可添加接地電阻以降低系統噪聲,但可能會增加系統電流。

- 振蕩器啟動定時器:為確保振蕩器和集成PHY穩定運行,ENC28J60內置了振蕩器啟動定時器(OST)。在電源上電復位或從掉電模式喚醒后,需等待7500個OSC1時鐘周期(300 μs),期間可通過SPI總線讀寫寄存器和緩沖器內存,但不宜進行數據包傳輸、接收或訪問MAC、MII、PHY寄存器等操作。當ESTAT寄存器中的CLKRDY位被置位時,方可開始正常的設備操作。

CLKOUT引腳應用

CLKOUT引腳可作為主機控制器時鐘或系統中其他設備的時鐘源。其內部預分頻器可將輸出頻率進行1、2、3、4或8分頻,通過ECOCON寄存器進行配置。在電源上電初期,CLKOUT引腳保持低電平,待OST計數結束后,將輸出默認頻率6.25 MHz(主時鐘除以4)。在改變頻率時,會有2 - 8個OSC1時鐘周期的延遲,期間CLKOUT引腳保持低電平。

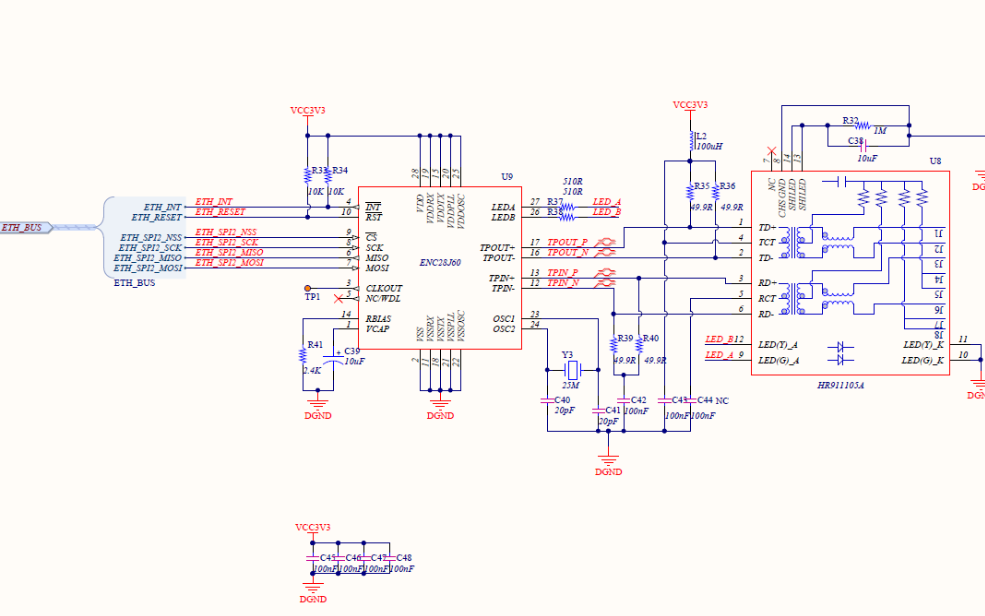

外部組件連接

- 電阻與電容:PHY模塊的內部模擬電路要求在RBIAS引腳與地之間連接一個2.32 kΩ、1%的電阻,以影響TPOUT + / - 信號幅度。同時,需在VCAP引腳與地之間連接一個低ESR的外部濾波電容,典型值為10 μF,最小值為1 μF。

- 脈沖變壓器:TPIN + / - 和TPOUT + / - 引腳需連接額定用于以太網操作的1:1中心抽頭脈沖變壓器。在以太網模塊啟用時,TPOUT引腳會持續吸收電流,通過改變TPOUT + 和TPOUT - 的相對電流來在以太網上創建差分電壓。

- 電源與接地:所有電源引腳需連接至同一電源,所有接地引腳需連接至同一接地節點,每個VDD和VSS引腳對附近應放置一個0.1 μF的陶瓷旁路電容,以減少信號干擾。

- I/O電平轉換:盡管ENC28J60為3.3V器件,但SPI的CS、SCK、SI輸入及RESET引腳具備5V容忍能力。若主機控制器為5V器件,可能需要使用單向電平轉換器,如74HCT08、74ACT125等。

- LED配置:LEDA和LEDB引腳支持自動極性檢測。在系統復位時,ENC28J60會檢測LED的連接方式,并根據PHLCON寄存器的配置驅動LED至默認狀態。可通過LACFG<3:0>和LBCFG<3:0>位分別配置LED的工作極性、閃爍速率和閃爍拉伸間隔。

三、內存組織架構

ENC28J60的內存采用靜態RAM實現,主要包括控制寄存器、以太網緩沖器和PHY寄存器三種類型。

控制寄存器

控制寄存器用于ENC28J60的配置、控制和狀態檢索,可通過SPI接口直接讀寫。其內存被劃分為四個32字節的存儲體,通過ECON1寄存器中的BSEL<1:0>位進行選擇。部分地址未被實現,寫入這些地址將被忽略,讀取返回‘0’。其中,地址1Ah的寄存器為保留寄存器,不應進行讀寫操作。

以太網緩沖器

以太網緩沖器由8 Kbytes的存儲單元組成,分為接收和發送緩沖器空間,其大小和位置可由主機控制器通過SPI接口進行編程設置。

- 接收緩沖器:采用硬件管理的循環FIFO緩沖器,通過ERXSTH:ERXSTL和ERXNDH:ERXNDL寄存器對定義其大小和位置。數據按順序寫入接收緩沖器,當寫入到ERXND指向的內存后,會自動回到ERXST指向的內存開始寫入。主機控制器可在接收邏輯未啟用時對ERXST和ERXND指針進行編程,但在接收邏輯啟用后(ECON1.RXEN置位)則不可修改。

- 發送緩沖器:8 Kbytes內存中未被配置為接收FIFO緩沖器的空間即為發送緩沖器。主機控制器負責管理數據包在發送緩沖器中的位置,在發送數據包前,需編程設置ETXST和ETXND指針,以指定要發送的數據包在發送緩沖器中的位置。

- 緩沖器讀寫:主機控制器通過單獨的讀、寫指針(ERDPT和EWRPT)結合SPI的讀緩沖器內存和寫緩沖器內存命令來訪問以太網緩沖器內容。在順序讀取接收緩沖器時,到達接收緩沖器末尾會發生回繞;在順序寫入緩沖器時,則不會發生回繞。

- DMA訪問:集成的DMA控制器在計算校驗和以及復制內存時需從緩沖器讀取數據,遵循與SPI訪問相同的回繞規則。

PHY寄存器

PHY寄存器用于PHY模塊的配置、控制和狀態檢索,所有PHY寄存器均為16位寬,共32個地址,但僅9個位置被實現。通過MIIM接口訪問PHY寄存器,具體操作包括寫入地址、數據,等待操作完成等步驟。

四、SPI接口指令集

ENC28J60的操作完全依賴于外部主機控制器通過SPI接口發送的命令,共實現了七種指令。

讀控制寄存器命令(RCR)

用于讀取ETH、MAC和MII寄存器的內容。對于ETH寄存器,發送RCR操作碼和5位寄存器地址后,數據將立即從SO引腳移出;對于MAC和MII寄存器,先移出一個虛擬字節,然后再移出數據。操作結束后,將CS引腳置高。

讀緩沖器內存命令(RBM)

允許主機控制器從集成的8 Kbyte發送和接收緩沖器內存中讀取字節。發送RBM操作碼和5位常量1Ah后,數據將從ERDPT指向的內存中移出。若ECON2寄存器中的AUTOINC位被置位,ERDPT指針將自動遞增,實現連續讀取。

寫控制寄存器命令(WCR)

用于向ETH、MAC和MII控制寄存器寫入數據。發送WCR操作碼和5位地址后,將數據寫入指定寄存器。操作結束后,將CS引腳置高。

寫緩沖器內存命令(WBM)

允許主機控制器向集成的8 Kbyte發送和接收緩沖器內存中寫入字節。發送WBM操作碼和5位常量1Ah后,將數據寫入EWRPT指向的內存。若ECON2寄存器中的AUTOINC位被置位,EWRPT指針將自動遞增,實現連續寫入。

位字段設置命令(BFS)

用于設置ETH控制寄存器中的最多8位。發送BFS操作碼和5位地址后,將數據字節與指定寄存器內容進行按位或操作。

位字段清除命令(BFC)

用于清除ETH控制寄存器中的最多8位。發送BFC操作碼和5位地址后,將數據字節取反并與指定寄存器內容進行按位與操作。

系統復位命令(SRC)

允許主機控制器發出系統軟復位命令。發送SRC操作碼和5位軟復位命令常量1Fh后,操作結束將CS引腳置高。

五、以太網數據包處理

數據包格式

正常的IEEE 802.3兼容以太網幀長度在64 - 1518字節之間,由目的MAC地址、源MAC地址、類型/長度字段、數據有效負載、可選填充字段和CRC組成。在傳輸和接收數據時,ENC28J60會自動生成或去除前導碼和幀起始分隔符字節,主機控制器通常無需處理這些內容。

數據包發送

在發送數據包前,需對MAC寄存器進行初始化設置。主機控制器需生成并寫入除前導碼、幀起始分隔符、填充和CRC(若已配置)之外的所有幀字段,并在數據包前添加一個單字節的每包控制字節。設置ETXST和ETXND指針,清除EIR.TXIF,設置EIE.TXIE和EIE.INTIE(若需要中斷),然后設置ECON1.TXRTS開始傳輸。傳輸完成或因錯誤/取消而中止時,ECON1.TXRTS位將被清除,發送狀態向量將被寫入ETXND + 1位置,EIR.TXIF將被置位,并觸發中斷(若已啟用)。

數據包接收

在接收數據包前,需初始化接收緩沖器、配置MAC和接收過濾器。啟用接收功能后,未被過濾的數據包將被寫入循環接收緩沖器。每個數據包前有一個6字節的頭部,包含下一個數據包指針和接收狀態向量。主機控制器可使用RBM命令從下一個數據包指針開始讀取數據包內容,處理完數據包后,需推進接收緩沖器讀取指針ERXRDPT,并將ECON2.PKTDEC位置1,以減少EPKTCNT寄存器的值。

六、接收過濾器配置

為減輕主機控制器的處理負擔,ENC28J60集成了多種接收過濾器,包括單播、模式匹配、Magic Packet?、哈希表、多播和廣播過濾器。這些過濾器由ERXFCON寄存器配置,可通過ANDOR位進行邏輯與或邏輯或操作。通過合理配置過濾器,可自動拒絕不需要的數據包。

七、雙工模式選擇與配置

ENC28J60不支持自動雙工協商,若要實現全雙工通信,需與遠程節點進行手動配置。

半雙工模式

當MACON3.FULDPX = 0且PHCON1.PDPXMD = 0時,ENC28J60工作在半雙工模式。在此模式下,同一時間只能有一個以太網控制器進行數據傳輸。若發生沖突,硬件將根據沖突發生的時間采取相應的處理措施:若在“沖突窗口”內發生沖突,將進行隨機指數退避延遲后重新嘗試傳輸;若在“沖突窗口”外發生沖突,則立即中止傳輸。默認情況下,半雙工模式會將發送的數據包回環至自身,可通過設置PHCON2.HDLDIS位來停止此行為。

全雙工模式

當MACON3.FULDPX = 1且PHCON1.PDPXMD = 1時,ENC28J60工作在全雙工模式。在此模式下,數據包可同時進行發送和接收,不會發生沖突。默認情況下,全雙工模式不會將發送的數據包回環至自身,若需要進行診斷,可設置PHCON1.PLOOPBK位。

八、流量控制策略

半雙工模式

在半雙工模式下,設置EFLOCON.FCEN0位可啟用流量控制。此時,以太網介質上會自動發送交替的‘1’和‘0’(55h)的連續前導碼模式,阻止其他節點進行通信。當主機控制器發送數據包時,前導碼模式將停止,發送完成或中止后,前導碼模式將自動恢復。由于此模式可能對網絡產生不利影響且效果不佳,建議僅在經過適當測試的封閉網絡環境中使用。

全雙工模式

在全雙工模式下,通過發送IEEE 802.3規范定義的暫停控制幀來實現硬件流量控制。主機控制器需設置MACON1寄存器中的TXPAUS和RXPAUS位,當接收緩沖器空間不足時,將EFLOCON寄存器寫入02h以開啟流量控制,硬件將定期發送包含暫停定時器值的暫停幀;當有足夠空間時,將EFLOCON寄存器寫入03h以關閉流量控制,硬件將發送一個包含暫停定時器值為0000h的暫停幀。

九、復位操作流程

ENC28J60支持多種復位方式,包括上電復位、系統復位、僅發送復位、僅接收復位和雜項MAC和PHY子系統復位。

上電復位(POR)

當VDD上升超過一定閾值時,芯片內部會產生上電復位脈沖,使設備進入初始化狀態。為確保正常復位,需滿足VDD的最小上升速率要求。上電復位后,雙端口緩沖器內存內容未知,但所有寄存器將加載為指定的復位值。部分功能在復位后需等待OSC啟動定時器結束方可訪問。

系統復位

可通過RESET引腳或SPI接口的系統復位命令進行系統復位。復位后,所有PHY寄存器在復位結束后至少50 μs內不應進行讀寫操作,所有寄存器將恢復到默認復位值,雙端口緩沖器內存狀態保持不變。

僅發送復位

通過向ECON1寄存器的TXRST位寫入‘1’來執行僅發送復位。若正在發送數據包,硬件將自動清除TXRTS位并中止傳輸,僅復位發送邏輯。

僅接收復位

通過向ECON1寄存器的RXRST位寫入‘1’來執行僅接收復位。若正在接收數據包,硬件將自動清除RXEN位并中止接收,僅復位接收邏輯。

PHY子系統復位

向PHCON1寄存器的PRST位寫入‘1’可復位PHY模塊。復位后,所有PHY寄存器內容將恢復到默認復位值,但PHY不能立即退出復位狀態,需等待一段時間,待硬件自動清除PRST位后,主機控制器方可使用PHY。

十、中斷管理機制

ENC28J60具備多個中斷源和一個中斷輸出引腳,通過EIE寄存器控制中斷使能,EIR寄存器記錄中斷標志。當啟用的中斷發生時,中斷引腳將保持低電平,直到主機控制器清除或屏蔽所有導致中斷的標志。建議使用位字段清除(BFC)SPI命令來重置EIR寄存器中的標志位,以避免在寫入命令期間意外改變標志。

主要中斷類型

- 接收錯誤中斷(RXERIF):表示接收緩沖器溢出或接收緩沖器中的數據包過多,無法再存儲新數據包。

- 發送錯誤中斷(TXERIF):表示發送中止,可能由過多沖突、后期沖突、數據包過大等原因導致。

- 發送中斷(TXIF):表示請求的數據包傳輸已結束。

- 鏈路更改中斷(LINKIF):表示鏈路狀態已更改,需通過設置PHIE.PLNKIE和PGEIE位來啟用。

- DMA中斷(DMAIF):表示DMA模塊已完成內存復制或校驗和計算。

- 接收數據包待處理中斷(PKTIF):表示接收緩沖器中存在一個或多個數據數據包。

喚醒功能

ENC28J60支持Wake - On - LAN/Remote Wake - up功能,可通過配置接收過濾器和中斷掩碼寄存器,在接收到喚醒數據包(如Magic Packet)時喚醒處于低功耗模式的主機控制器。

十一、DMA控制器應用

ENC28J60集成的雙用途DMA控制器可用于在8 Kbyte內存緩沖器內復制數據,也可計算與多種行業標準協議兼容的16位校驗和。

內存復制操作

為在緩沖器內復制內存,需適當編程設置EDMAST、EDMAND和EDMADST寄存器對,設置EIE.DMAIE和EIE.INTIE(若需要中斷),清除EIR.DMAIF,確認ECON1.CSUMEN位已清除,然后設置ECON1.DMAST開始復制。復制完成后,DMA硬件將清除DMAST位,設置DMAIF位,并觸發中斷(若已啟用)。

校驗和計算操作

計算校驗和時,需編程設置EDMAST和EDMAND寄存器對,清除EIR.DMAIF,設置EIE.DMAIE和EIE.INTIE(若需要中斷),然后設置ECON1.CSUMEN和ECON1.DMAST開始計算。計算完成后,硬件將清除DMAST位,設置DMAIF位,并觸發中斷(若已啟用),計算結果將存儲在EDMACSH和EDMACSL寄存器中。

十二、內置自測試控制器使用方法

ENC28J60的內置自測試(BIST)模塊可用于驗證8 Kbyte內存緩沖器中每個位的正常運行。通過EBSTCON、EBSTSD、EBSTCSH和EBSTCSL四個寄存器來操作BIST控制器,支持隨機數據填充、地址填充和模式移位填充三種操作模式。

測試步驟

- 編程設置EDMAST寄存器對

-

SPI接口

+關注

關注

0文章

283瀏覽量

36797 -

ENC28J60

+關注

關注

0文章

36瀏覽量

22410 -

以太網控制器

+關注

關注

0文章

52瀏覽量

13197

發布評論請先 登錄

ENC28J60以太網模塊與Arduino的連接方案介紹

新型以太網控制器ENC28J60及其接口技術

stm32有自帶的以太網模塊與ENC28J60控制器有什么區別?

獨立以太網控制器ENC28J60電子資料

ENC28J60 spi 接口 以太網 網絡模塊 提供 代碼

微雪電子ENC28J60以太網模塊簡介

ENC28J60的網口資料詳細資料說明

ENC28J60帶SPI接口的獨立以太網控制器數據手冊免費下載

深度剖析ENC28J60:獨立以太網控制器的設計與應用指南

深度剖析ENC28J60:獨立以太網控制器的設計與應用指南

評論