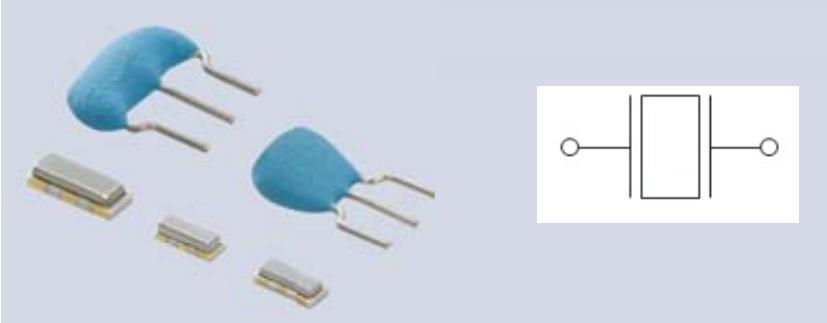

在電子電路中,石英晶體諧振器作為核心頻率控制元件,其性能直接影響系統(tǒng)的穩(wěn)定性和可靠性。為了確保晶體諧振器與電路實(shí)現(xiàn)最佳匹配,設(shè)計(jì)工程師需重點(diǎn)關(guān)注以下幾個(gè)核心要素:

一、負(fù)性阻抗:振蕩穩(wěn)定性的基石

負(fù)性阻抗(-R)是振蕩電路起振的關(guān)鍵參數(shù),其大小直接決定振蕩的可靠性和穩(wěn)定性。根據(jù)行業(yè)標(biāo)準(zhǔn),負(fù)性阻抗應(yīng)至少達(dá)到晶體諧振阻抗(Rr)的3倍,而實(shí)際設(shè)計(jì)中建議提升至5倍以上,以縮短起振時(shí)間并增強(qiáng)抗干擾能力。

設(shè)計(jì)要點(diǎn):

.增益優(yōu)化?:通過調(diào)整振蕩回路增益(gm)來提升負(fù)性阻抗,例如在皮爾斯振蕩器中合理設(shè)置反饋電阻(RF)。

.?穩(wěn)定性測(cè)試?:采用可變電阻串聯(lián)法,逐步增大電阻直至振蕩停止,以此驗(yàn)證負(fù)性阻抗是否滿足設(shè)計(jì)要求。

二、激勵(lì)功率:平衡驅(qū)動(dòng)與保護(hù)的藝術(shù)

激勵(lì)功率是驅(qū)動(dòng)晶體諧振器機(jī)械振動(dòng)的能量來源,其強(qiáng)度需精確控制以避免性能下降或器件損壞。

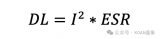

功率計(jì)算與調(diào)節(jié):

??測(cè)量方法?:使用高頻電流探頭檢測(cè)流過晶體的電流(Ix),通過公式DL = I2 × RL計(jì)算激勵(lì)功率,其中RL = Rr × (1 + Co/CL)2。

??調(diào)節(jié)策略?:

?減小Cg(門極電容)或Cd(漏極電容)以降低驅(qū)動(dòng)強(qiáng)度。

?增大Rd(阻尼電阻)抑制過驅(qū)動(dòng)風(fēng)險(xiǎn)。

??推薦范圍?:MHz級(jí)晶體的激勵(lì)功率控制在1~100μW,KHz級(jí)晶體則需低于1μW。

三、工作頻率:負(fù)載電容的精準(zhǔn)匹配

輸出頻率的準(zhǔn)確性取決于電路負(fù)載電容(Cpcb)與晶體標(biāo)稱負(fù)載電容(CL)的一致性。兩者匹配時(shí),晶體工作在諧振頻率(Fr),實(shí)現(xiàn)最佳頻率穩(wěn)定性。

頻率校準(zhǔn)方法:

.?負(fù)載電容計(jì)算?:

?公式:CL = C1 × C2 / (C1 + C2) + Cs

?Cs為雜散電容,包括PCB分布電容和IC結(jié)電容,需通過近場(chǎng)探頭實(shí)測(cè)優(yōu)化。

.?頻率微調(diào)?:

?根據(jù)Fpcb = Fr × (1 + C1 / (2 × (Co + CL)))調(diào)整C1、C2,使輸出頻率接近標(biāo)稱值。

?示例:若Fr=12MHz,Co=3pF,CL=18pF,則Fpcb≈12.0003MHz,誤差可忽略。

四、設(shè)計(jì)實(shí)踐:從理論到落地的步驟

.?晶振選型?:優(yōu)先選擇低ESR(等效串聯(lián)電阻)的晶體,提升起振可靠性。

.?電路布局?:

?縮短晶振走線,減少寄生電感。

?遠(yuǎn)離高頻信號(hào)源,降低電磁干擾。

.?保護(hù)措施?:串聯(lián)小電阻(RS)限制過驅(qū)動(dòng)電流,延長(zhǎng)晶體壽命。

.?驗(yàn)證流程?:

?測(cè)試振蕩安全系數(shù)(OSF),確保MHz級(jí)OSF>5,KHz級(jí)OSF>3。

?校準(zhǔn)驅(qū)動(dòng)功率,避免超限運(yùn)行。

五、常見問題與解決方案

??不起振?:檢查負(fù)性阻抗是否達(dá)標(biāo),或激勵(lì)功率是否過低。

??頻率偏移?:驗(yàn)證負(fù)載電容匹配性,調(diào)整C1、C2補(bǔ)償雜散電容。

??間歇振蕩?:優(yōu)化電路布局,減少外界干擾。

通過系統(tǒng)化設(shè)計(jì),工程師可顯著提升晶體諧振器的性能,為通信、計(jì)時(shí)等應(yīng)用提供穩(wěn)定可靠的頻率基準(zhǔn)。

-

晶振

+關(guān)注

關(guān)注

35文章

3598瀏覽量

73655 -

諧振器

+關(guān)注

關(guān)注

4文章

1169瀏覽量

67540 -

控制元件

+關(guān)注

關(guān)注

0文章

52瀏覽量

3732

發(fā)布評(píng)論請(qǐng)先 登錄

探秘晶體諧振器穩(wěn)定性運(yùn)行

石英晶體諧振器的頻率與電阻溫度特性及其影響因素

儲(chǔ)存石英晶體諧振器應(yīng)用與原理

晶體振蕩器與晶體諧振器的區(qū)別

使用MEMS振蕩器代替晶體諧振器的 8 大理由(一)

石英晶體諧振器分析和設(shè)計(jì)基礎(chǔ)

晶體諧振器的振動(dòng)頻率和它的測(cè)量方法

陶瓷諧振器與石英晶體諧振器的區(qū)別

石英晶體諧振器設(shè)計(jì)中的關(guān)鍵參數(shù)

晶體諧振器與電路匹配設(shè)計(jì):實(shí)現(xiàn)穩(wěn)定頻率輸出的關(guān)鍵

晶體諧振器與電路匹配設(shè)計(jì):實(shí)現(xiàn)穩(wěn)定頻率輸出的關(guān)鍵

評(píng)論