Synopsys ARC-V 處理器中的高級(jí)指令融合引入了一種新型機(jī)制,用于融合常見的 RISC-V 指令對(duì),旨在提高處理器流水線效率,特別是針對(duì)資源受限的嵌入式處理器。通過融合來自不同功能單元的指令, 它將單發(fā)射、順序執(zhí)行的處理器擴(kuò)展為雙指令發(fā)射。

重要的是,該機(jī)制并未引入新的指令,完全兼容 RISC-V 架構(gòu),并且對(duì)軟件透明,確保與現(xiàn)有軟件和硬件環(huán)境的無縫集成。通過減少流水線開銷并簡(jiǎn)化指令處理,高級(jí)指令融合顯著提升嵌入式處理的效率。

該方法還具備可適應(yīng)的設(shè)計(jì)原則,可以從雙指令融合擴(kuò)展到多指令融合,從而惠及整個(gè)生態(tài)系統(tǒng)中的 RISC-V 處理器實(shí)現(xiàn)。

嵌入式 RISC-V 設(shè)計(jì)面臨的挑戰(zhàn)

隨著嵌入式系統(tǒng)不斷演進(jìn),設(shè)計(jì)人員面臨在嚴(yán)格的功耗和成本限制下實(shí)現(xiàn)更高性能和日益異構(gòu)的處理架構(gòu)的挑戰(zhàn)。這一轉(zhuǎn)變部分源于邊緣人工智能(Edge AI)的快速擴(kuò)展,越來越多的工作負(fù)載被推向數(shù)據(jù)源附近,這要求更智能、更強(qiáng)大的嵌入式解決方案。

與此同時(shí),開放標(biāo)準(zhǔn)的 RISC-V 架構(gòu)正在獲得廣泛推動(dòng),尤其在微控制器單元(MCU)領(lǐng)域,其采用率和出貨量處于領(lǐng)先地位。這些處理器必須在滿足極端功耗、安全性和可靠性標(biāo)準(zhǔn)的同時(shí),支持邊緣復(fù)雜的工作負(fù)載。

RISC-V 指令集架構(gòu)(ISA)設(shè)計(jì)為簡(jiǎn)潔且模塊化,使用大量簡(jiǎn)單指令可以降低 CPU 功耗和面積。然而,這種指令冗余可能帶來性能限制,因?yàn)閺?fù)雜操作需要更多周期來完成。

雖然雙發(fā)射、多發(fā)射以及亂序執(zhí)行等技術(shù)可以提升每周期指令數(shù)(IPC)和性能,但它們通常會(huì)增加面積需求,這對(duì)資源受限的嵌入式處理器來說是一個(gè)挑戰(zhàn)。

指令融合是一項(xiàng)眾所周知的技術(shù),它利用可用的硬件資源來增加指令級(jí)并行性(ILP)。指令融合以最小的面積開銷提升 ILP 和 CPU 性能,特別適用于在小型、順序執(zhí)行的處理器中提高性能密度。

本文描述了一種新穎的高級(jí)指令融合技術(shù),用于在微架構(gòu)層面融合成對(duì)的 RISC-V 指令。該技術(shù)在避免引入單獨(dú)的流水線的前提下,實(shí)現(xiàn)了雙發(fā)射處理器的主要效率優(yōu)勢(shì),同時(shí)保持 RISC-V 兼容性。

什么是高級(jí)指令融合?

架構(gòu)級(jí)融合 vs 微架構(gòu)級(jí)融合

某些指令集在架構(gòu)級(jí)別融合指令,另一些指令集則在微架構(gòu)/實(shí)現(xiàn)層面進(jìn)行指令融合。典型示例包括加載/存儲(chǔ)對(duì)以及帶自動(dòng)增量的加載/存儲(chǔ)。在某些指令集(例如:ARM 和 ARC)中,這些在架構(gòu)級(jí)別融合,即:這些操作由單條指令完成。其他指令集(例如:RISC-V)則采取不同的方法,保持架構(gòu)指令簡(jiǎn)潔,將融合操作交由微架構(gòu)實(shí)現(xiàn)。

微架構(gòu)級(jí)融合相比架構(gòu)級(jí)融合的主要優(yōu)勢(shì)包括:

微架構(gòu)級(jí)融合能夠?qū)崿F(xiàn)更激進(jìn)的優(yōu)化,例如即使內(nèi)存地址不連續(xù)也可以融合加載指令對(duì)

不同 ISA 之間的二進(jìn)制兼容性更易維護(hù),因?yàn)楹?jiǎn)單或小型處理器無需實(shí)現(xiàn)指令融合

在微架構(gòu)級(jí)別實(shí)現(xiàn)融合要求處理器具有足夠的指令獲取帶寬。簡(jiǎn)單的 RISC ISA(例如:RISC-V)比較冗長(zhǎng),因此比在架構(gòu)級(jí)別執(zhí)行指令融合的 ISA 消耗更多指令獲取帶寬。

簡(jiǎn)單的順序單發(fā)射處理器每周期的指令獲取帶寬通常不超過 4 字節(jié)。這對(duì)微架構(gòu)融合構(gòu)成了嚴(yán)重限制。大多數(shù)融合對(duì)需要 16 位壓縮指令。因此,在資源受限的嵌入式處理器中利用微架構(gòu)融合的第一步是增加其指令獲取帶寬。

實(shí)現(xiàn)細(xì)節(jié)

資源受限的 RISC-V 設(shè)計(jì)中的高級(jí)指令融合

傳統(tǒng)的融合指令對(duì)不需要額外的寄存器文件讀寫帶寬。與其他 RISC-V 指令一樣,一個(gè)融合指令對(duì)最多從寄存器文件讀取兩個(gè)源操作數(shù),并產(chǎn)生一個(gè)結(jié)果。

然而,某些融合指令對(duì)候選會(huì)打破這一規(guī)則:

加載雙指令(Load-double):融合兩個(gè)加載指令時(shí),需要兩個(gè)寄存器寫端口

存儲(chǔ)雙指令(Store-double):融合兩個(gè)存儲(chǔ)指令時(shí),需要三個(gè)寄存器讀端口(存儲(chǔ)指令有一個(gè)公共基地址,但每個(gè)存儲(chǔ)指令需要獨(dú)立的存儲(chǔ)數(shù)據(jù)操作數(shù))

乘加指令(MAC):融合乘法和加法時(shí),需要三個(gè)寄存器文件讀端口

要利用這些高級(jí)融合指令對(duì)(雙加載、雙存儲(chǔ)和 MAC),需要額外的硬件資源。更具體地說:寄存器文件應(yīng)能夠提供三個(gè)源操作數(shù),并增加第二個(gè)寄存器寫端口。

高級(jí)指令融合技術(shù)增加了額外的硬件資源,并提高了其利用率。它通過利用微架構(gòu)融合框架,在順序執(zhí)行處理器上實(shí)現(xiàn)了有限的雙發(fā)射能力。采用這種方法,任何映射到不同的功能單元、最多需要三個(gè)源操作數(shù)、并且最多產(chǎn)生兩個(gè)目標(biāo)寄存器的兩個(gè)獨(dú)立的指令,都可以被視為高級(jí)融合(雙發(fā)射)候選對(duì)。

這些指令在前端通過預(yù)解碼的操作碼和寄存器操作數(shù)標(biāo)識(shí)符進(jìn)行融合。預(yù)解碼的寄存器操作數(shù)標(biāo)識(shí)符用于檢測(cè)高級(jí)融合指令對(duì)之間是否存在數(shù)據(jù)依賴關(guān)系。解碼器被增強(qiáng)以接收融合指令的附加信息,但不會(huì)被復(fù)制。融合指令對(duì)中的每條指令被分發(fā)至對(duì)應(yīng)的功能單元。處理器的后端指令融合基本無感,除了增加架構(gòu) PC 和處理由融合指令觸發(fā)的異常之外,不需要引入單獨(dú)的流水線。

圖 1 展示了帶有高級(jí)指令融合的 RISC-V 處理器前端的典型實(shí)現(xiàn)。一些示例包括以下指令對(duì):LOAD+ALU、LOAD+BR、LOAD+MPY、ST+BR、ST+ALU。

性能結(jié)果

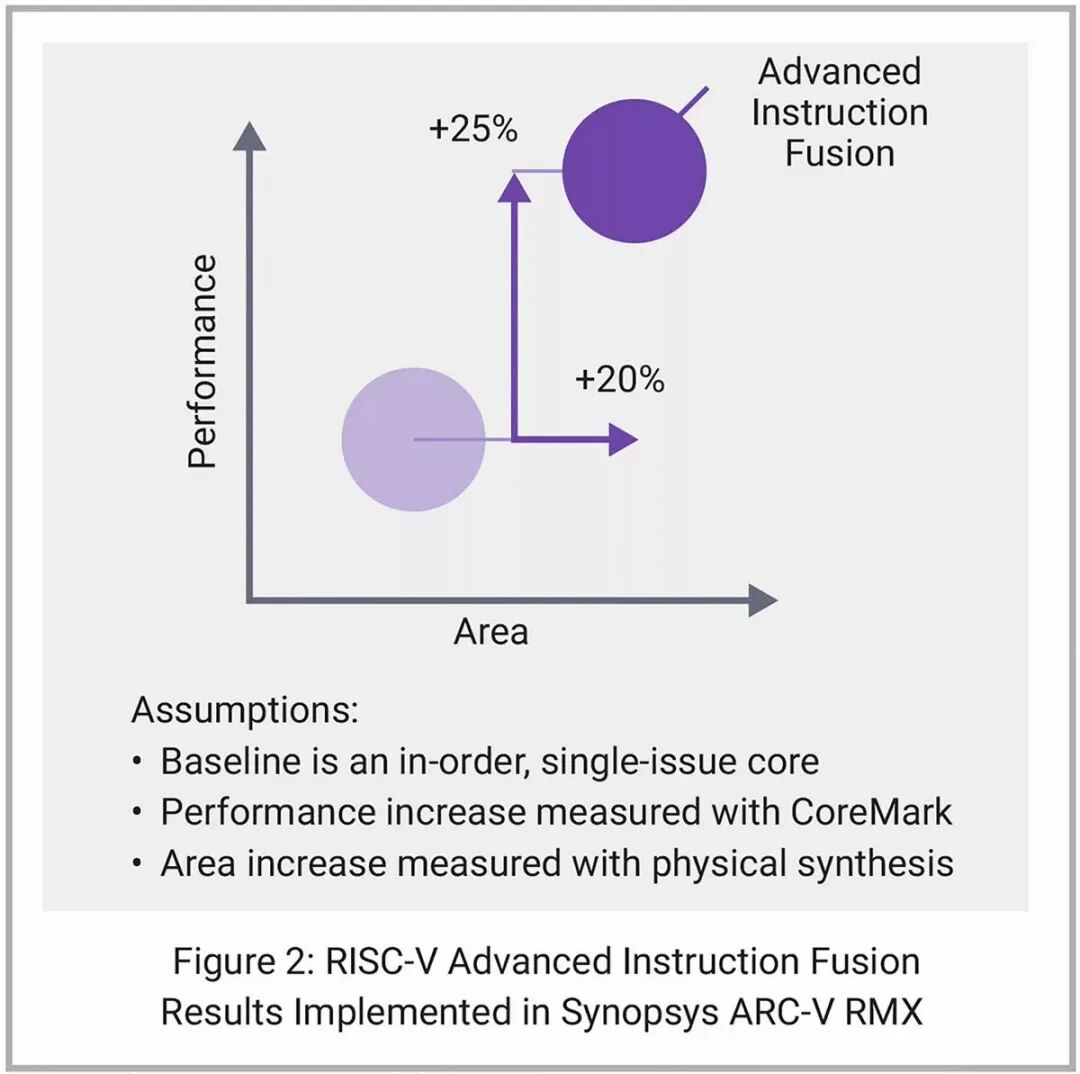

Pollack 定律指出,微架構(gòu)增強(qiáng)帶來的性能提升通常隨復(fù)雜度增加的平方根增長(zhǎng)。圖 2 顯示,對(duì)于 Synopsys ARC-V RMX(一款帶有高級(jí)指令融合的 RISC-V 嵌入式處理器),測(cè)得的 CoreMark/MHz 表明其性能提升與硅面積呈線性關(guān)系,帶來了更大的性能優(yōu)勢(shì)。此外,由于高級(jí)指令融合僅產(chǎn)生固定的面積開銷,性能密度的提升也更加顯著。

結(jié)論

高級(jí)指令融合為在資源受限的嵌入式系統(tǒng)中提供了一種有效提升處理器流水線效率的方法,其核心是融合常見的 RISC-V 指令對(duì)。該技術(shù)在不引入新指令或需要軟件修改的前提下,通過在單發(fā)射、順序執(zhí)行處理器上實(shí)現(xiàn)來自不同功能單元的指令融合,完成雙指令發(fā)射,實(shí)現(xiàn)了顯著的性能提升,并完全兼容 RISC-V 架構(gòu)。流水線開銷降低和簡(jiǎn)化指令處理帶來了顯著的效率提升,同時(shí)這種可擴(kuò)展的設(shè)計(jì)支持未來擴(kuò)展到多指令融合。總體而言,高級(jí)指令融合為整個(gè) RISC-V 生態(tài)系統(tǒng)中高效提升處理器性能提供了一種實(shí)用且可擴(kuò)展的解決方案。

關(guān)鍵要點(diǎn)

理想的嵌入式系統(tǒng)設(shè)計(jì):該技術(shù)專為面積和功耗受限的小型、順序執(zhí)行處理器設(shè)計(jì),適用于無法采用傳統(tǒng)多發(fā)射或亂序架構(gòu)的場(chǎng)景。

無需更改 ISA 即可提升性能:高級(jí)指令融合在不引入新指令或破壞 RISC-V 兼容性的情況下,提高 IPC 和流水線效率。

微架構(gòu)級(jí)融合優(yōu)勢(shì):相比架構(gòu)級(jí)融合,在微架構(gòu)級(jí)別進(jìn)行融合支持更靈活、更激進(jìn)的優(yōu)化策略。

硬件高效雙發(fā)射:通過融合來自不同功能單元的指令,實(shí)現(xiàn)雙指令發(fā)射,僅需適度增加硬件資源,如增加寄存器端口。

可擴(kuò)展設(shè)計(jì):融合框架具有適應(yīng)性,可擴(kuò)展支持多指令融合,推動(dòng)在整個(gè) RISC-V 生態(tài)系統(tǒng)中更廣泛采用。

-

處理器

+關(guān)注

關(guān)注

68文章

20283瀏覽量

253204 -

嵌入式

+關(guān)注

關(guān)注

5202文章

20519瀏覽量

335375 -

指令

+關(guān)注

關(guān)注

1文章

623瀏覽量

37588 -

RISC-V

+關(guān)注

關(guān)注

49文章

2907瀏覽量

53188

原文標(biāo)題:突破能效瓶頸:RISC-V 高級(jí)指令融合如何實(shí)現(xiàn)性能密度躍升

文章出處:【微信號(hào):Synopsys_CN,微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

【RISC-V開放架構(gòu)設(shè)計(jì)之道|閱讀體驗(yàn)】RISC-V基礎(chǔ)整數(shù)指令集

RISC-V的MCU與ARM對(duì)比

rIsc-v的缺的是什么?

RISC-V指令集的特點(diǎn)總結(jié)

RISC-V指令集概述

關(guān)于RISC-V芯片的應(yīng)用學(xué)習(xí)總結(jié)

RISC-V B擴(kuò)展介紹及實(shí)現(xiàn)

RISC-V有哪些特點(diǎn)

一文看懂RISC-V代碼密度

什么是RISC-V? RISC-V指令具有哪些特點(diǎn)應(yīng)用?

優(yōu)化的關(guān)鍵,RISC-V中的性能監(jiān)控

risc-v是什么意思

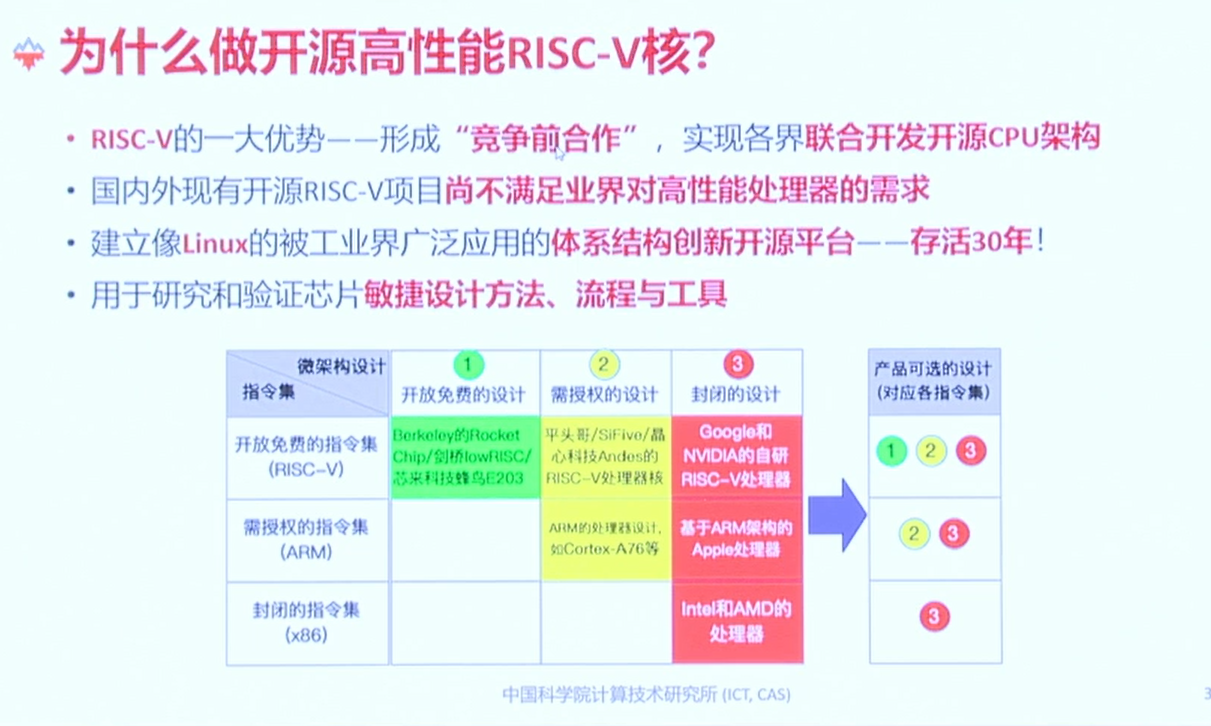

為什么做開源高性能RISC-v核,香山開源高性能RISC-V處理器開發(fā)流程

risc-v中國(guó)峰會(huì)直播:如何優(yōu)化RISC-V指令集架構(gòu)的代碼密度?

第一屆RISC-V中國(guó)峰會(huì)看點(diǎn) risc-v開發(fā)要怎么優(yōu)化risc-v指令集架構(gòu)代碼密度

RISC-V高級(jí)指令融合如何實(shí)現(xiàn)性能密度躍升

RISC-V高級(jí)指令融合如何實(shí)現(xiàn)性能密度躍升

評(píng)論