在云計算與 AI訓練等萬卡級大規模集群中,數據需要在計算節點、存儲系統與高速網絡設備之間進行持續、高速的交換。在這一架構下,系統性能的瓶頸不僅來自算力本身,也越來越多地受到時鐘質量的制約。

對于 100/200/400GbE以太網、InfiniBand等高速互連鏈路而言,時鐘的抖動、穩定性與信號完整性,直接影響SerDes的誤碼率、鏈路穩定性以及RDMA等低延遲通信能力。

一顆性能可靠的時鐘源,已成為保障大規模并行系統穩定運行的基礎器件。

一、晶振選型:為什么是 3225 / 156.25MHz / LVDS?

在實際工程應用中,3225封裝、156.25MHz、3.3V LVDS輸出的有源晶振,已成為高速互連與網絡系統中被廣泛采用的成熟方案。

1.封裝選擇:3225——密度與可靠性的平衡點

高密度適配:3.2×2.5 mm封裝,適用于網卡、交換芯片、FPGA周邊等高集成PCB設計

可靠性更優:相比小封裝,3225在焊接強度、熱應力緩沖及長期運行可靠性方面表現更穩健,更適合7×24小時連續運行環境

2.頻率選擇:156.25MHz——高速以太網的典型基準頻點,156.25MHz是100GbE、400GbE等高速以太網架構中常用的SerDes參考時鐘頻點,通過芯片內部 PLL,可派生多路同源、低抖動時鐘,用于高速收發通道同步。在網絡接口與交換設備中,屬于成熟且工程驗證充分的基礎頻率方案

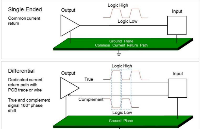

3.輸出方式:LVDS——高速系統中的信號完整性保障

差分結構天然抑制共模噪聲,適用于高速、高噪聲板級環境,擺幅較小、邊沿可控,有助于降低 EMI風險,簡化EMC設計,驅動能力適中,可滿足多路時鐘輸入需求,減少額外緩沖器件

二、工程師選型關注點

在云計算與 AI集群項目中,晶振選型除基礎參數外,工程師通常重點關注:

相位抖動:常見要求為 12kHz–20MHz積分范圍內< 1ps RMS,以保證高速?SerDes?足夠的時序裕量

頻率穩定度:通常為 ±25ppm或更優,覆蓋-40℃ 至+85℃/ +105℃ 工況,保障系統長期同步

電源噪聲抑制能力:影響系統對電源設計的容忍度,直接關系整體魯棒性

啟動時間與一致性:對大規模部署系統尤為重要,關系節點間啟動同步與長期一致性

三、系統應用價值

在萬卡級集群環境中,穩定的高頻差分時鐘可帶來明確的工程收益:

降低高速鏈路誤碼率,減少數據重傳與鏈路異常

提升系統長期運行穩定性,適配高負載、連續運行場景

簡化系統時鐘架構設計,有利于不同子系統間的方案統一

四、云計算工程實例

在云計算與 AI訓練集群項目中,系統在高速計算節點與網絡交換模塊中,選用了3225封裝156.25MHz LVDS有源晶振 作為基礎時鐘源:

應用位置:高速網絡接口、互連模塊及交換芯片參考時鐘

部署規模:隨集群規模擴展,單項目月度用量穩定在 數千只級別

工程價值:在大規模并行部署條件下,滿足系統對時鐘一致性與長期運行穩定性的設計預期

五、時鐘雖小,卻決定系統上限

在算力規模持續擴張的背景下,晶振元器件已不再是“可替代的通用元件”,而是決定系統可靠性與運行效率的重要基礎。3225封裝156.25MHz LVDS有源晶振,憑借成熟的工程應用基礎與穩定的系統表現,已成為高速云計算與AI集群中的務實選擇。

以 SJK晶振 為代表的晶振廠商,正持續圍繞高速互連與云計算應用場景,優化產品一致性與工程可靠性,為下一代數據中心與算力基礎設施提供穩定的時間基準支持。

-

有源晶振

+關注

關注

1文章

1011瀏覽量

22941 -

差分晶振

+關注

關注

0文章

187瀏覽量

2087

發布評論請先 登錄

想用CDCI6214輸出4個156.25MHz的LVDS時鐘,參考時鐘用的是25MHz晶振,該如何配置?

從25G PHY到AI平臺:差分晶振FCO-PG系列關鍵應用全解讀

從SFP到OSFP:FCom差分晶振覆蓋全類型光模塊的時鐘設計方案

差分輸出VCXO振蕩器 | FCom富士晶振 - 低抖動時鐘解決方案

AD9106不輸出波形只是將時鐘源改成180MHz的LVDS晶振

用于高速AD的低抖動時鐘穩定電路

YXC石英有源差分晶振,頻點156.25mhz,輸出方式HCSL,應用于高性能服務器

高穩定低抖動156.25?MHz LVDS晶振:破解高速AI與云計算時鐘瓶頸

高穩定低抖動156.25?MHz LVDS晶振:破解高速AI與云計算時鐘瓶頸

評論