深入解析DS90UB91xQ-Q1:FPD-Link III的卓越之選

在汽車電子領域,攝像頭與視頻處理器之間的數據傳輸需求日益增長,對高速、可靠且低延遲的連接方案的需求也愈發迫切。DS90UB91xQ-Q1系列芯片組,作為德州儀器(TI)推出的一款專為滿足此類需求而設計的產品,以其卓越的性能和豐富的特性,在汽車電子市場中占據了重要地位。今天,我們就來深入探討一下DS90UB91xQ-Q1芯片組的特點、應用以及設計要點。

文件下載:ds90ub913q-q1.pdf

芯片概述

DS90UB91xQ-Q1芯片組由DS90UB913Q-Q1 serializer(串行器)和DS90UB914Q-Q1 deserializer(解串器)組成,為電子控制單元(ECU)中的成像器和視頻處理器之間提供了穩定可靠的連接。該芯片組支持10 - 100 MHz的輸入像素時鐘,能夠處理10位和12位的數據,非常適合用于汽車前后視攝像頭、停車輔助環視系統等應用場景。

特性亮點

- 高速數據傳輸:通過單差分對實現高速前向通道和雙向控制通道的數據傳輸,最高支持1.4 Gbps的線速率,確保了視頻數據的實時、準確傳輸。

- 低延遲雙向控制:雙向控制通道支持400 kHz的I2C通信,實現了成像器與ECU之間的低延遲雙向通信,無需額外的控制線。

- DC平衡編碼:采用嵌入式時鐘和DC平衡編碼技術,支持AC耦合互連,有效減少了信號傳輸中的直流偏移問題,提高了信號質量。

- 自適應均衡:接收器內置自適應均衡器,能夠自動補償電纜損耗,確保在長達25米的屏蔽雙絞線(STP)上實現可靠的數據傳輸。

- 多模式支持:支持12位低頻模式(10 - 50 MHz)、12位高頻模式(15 - 75 MHz)和10位模式(20 - 100 MHz),可根據不同的應用需求靈活配置。

- 錯誤檢測:提供奇偶校驗和CRC校驗功能,可對前向通道和反向通道的數據進行錯誤檢測,確保數據的完整性。

- EMI/EMC優化:解串器采用交錯輸出和可編程擴頻時鐘生成(SSCG)技術,有效降低了電磁干擾(EMI),提高了系統的抗干擾能力。

應用場景

前后視攝像頭

在汽車碰撞緩解系統中,前后視攝像頭起著至關重要的作用。DS90UB91xQ-Q1芯片組的單差分對互連和高速數據傳輸能力,使得攝像頭能夠將高分辨率的視頻數據實時傳輸到ECU中,為駕駛員提供清晰的視野,及時發現潛在的危險。

停車輔助環視系統

停車輔助環視系統需要多個攝像頭同時工作,以提供車輛周圍的全景視圖。DS90UB914Q-Q1解串器的2:1多路復用器功能,允許用戶在兩個串行器輸入之間進行選擇,方便實現多攝像頭的連接和切換。同時,雙向控制通道的支持使得ECU能夠對攝像頭進行實時控制和配置。

功能特性詳解

串行幀格式

高速前向通道由28位數據組成,包括視頻數據、同步信號、I2C和奇偶校驗位。數據經過隨機化、平衡和加擾處理,以優化在AC耦合鏈路上的信號傳輸。雙向控制通道數據與高速前向數據一起通過單串行鏈路傳輸,實現了全雙工通信。

線速率計算

不同模式下,芯片組通過內部時鐘分頻和倍頻來實現不同的線速率。具體計算公式如下:

- 12位低頻模式:Line rate = fPCLK × 28,例如fPCLK = 50 MHz時,線速率為1.4 Gbps。

- 10位模式:Line rate = fPCLK / 2 × 28,例如fPCLK = 100 MHz時,線速率為1.4 Gbps。

- 12位高頻模式:Line rate = fPCLK × (2 / 3) × 28,例如fPCLK = 75 MHz時,線速率為1.4 Gbps。

解串器多路復用器

DS90UB914Q-Q1解串器的2:1多路復用器允許用戶選擇兩個串行器輸入中的一個作為活動通道。通過SEL引腳或寄存器控制,可以方便地實現攝像頭的切換。

錯誤檢測

芯片組通過前向通道的一個奇偶校驗位和反向通道的4位CRC校驗位進行錯誤檢測。檢測到的錯誤數量分別存儲在串行器和解串器的8位寄存器中,方便用戶進行監控和調試。

雙向控制總線和I2C模式

I2C兼容接口允許通過雙向控制通道對芯片組進行編程。SCL和SDA線為開漏輸出,需要外部上拉電阻。芯片組支持標準模式(100 kHz)和快速模式(400 kHz)的I2C通信。

從時鐘拉伸

在I2C通信中,芯片組支持從時鐘拉伸功能,即在每個I2C傳輸的第9個時鐘(ACK信號之前),從設備可以將SCL線拉低,以等待遠程外設的響應。

I2C透傳

I2C透傳功能允許獨立尋址從設備,可選擇是否將I2C指令傳輸到遠程I2C設備。通過該功能,可以實現對遠程總線上特定設備的訪問和通信。

設備ID地址解碼

串行器和解串器分別通過ID[x]和IDx[0:1]引腳來設置物理從設備地址。通過不同的電阻值,可以為每個設備分配唯一的地址,最多支持5個串行器和16個解串器設備。

可編程控制器

芯片組內置I2C從控制器,可用于配置可編程寄存器和控制通用輸入輸出(GPIO)引腳。通過I2C接口,可以方便地對芯片組進行參數設置和功能控制。

多攝像頭同步

對于需要多個攝像頭進行幀同步的應用,建議使用GPIO引腳傳輸控制信號。系統控制器提供場同步輸出,攝像頭接收輔助同步輸入,以實現多個攝像頭的同步。

通用輸入輸出(GPIO)

串行器有4個GPO引腳,解串器有4個GPIO引腳。這些引腳可以配置為輸入或輸出,用于控制和響應各種命令。在使用外部振蕩器作為參考時鐘時,GPO3和GPIO2引腳有特殊的配置。

LVCMOS VDDIO選項

串行器支持1.8 V、2.8 V和3.3 V的輸入電壓,解串器支持1.8 V和3.3 V的輸出電壓,可根據系統接口的需求進行靈活配置。

解串器自適應輸入均衡(AEQ)

解串器的接收器輸入提供自適應輸入均衡濾波器,可補償介質損耗。均衡水平可以通過寄存器進行手動選擇,也可以使用CMLOUTP/CMLOUTN引腳觀察自適應均衡器的輸出。

EMI降低

- 解串器交錯輸出:接收器交錯輸出切換,在定義的窗口內隨機分布轉換,減少了同時切換的輸出數量,降低了電源噪聲和整體EMI。

- 擴頻時鐘生成(SSCG):解串器的并行數據和時鐘輸出具有可編程的SSCG范圍(10 - 100 MHz),通過SSC控制寄存器可以控制調制速率和調制頻率變化,生成不同的SSC配置文件。

設備功能模式

外部振蕩器作為參考時鐘

當成像器提供的像素時鐘抖動超出芯片組的容限時,建議使用外部振蕩器作為參考時鐘。在這種模式下,DS90UB913Q-Q1的GPO3引腳作為外部振蕩器的輸入,GPO2引腳將分頻后的時鐘輸出反饋給成像器。

成像器像素時鐘作為參考時鐘

芯片組也可以使用成像器的像素時鐘作為參考時鐘。在這種模式下,串行器和解串器的GPIO引腳可以正常配置和使用。

模式引腳配置

串行器和解串器的MODE引腳用于選擇工作模式。通過不同的電阻值,可以選擇使用成像器的PCLK或外部振蕩器作為參考時鐘,以及選擇不同的數據模式(12位低頻模式、12位高頻模式或10位模式)。

時鐘數據恢復狀態標志(LOCK)、輸出使能(OEN)和輸出狀態選擇(OSS_SEL)

LOCK引腳用于指示解串器的PLL是否鎖定。OEN和OSS_SEL引腳用于控制輸出的狀態,包括數據、GPIO和時鐘的輸出。

多設備尋址

對于需要在同一I2C總線上訪問多個相同地址的攝像頭設備的應用,芯片組支持從ID匹配/別名功能,通過編程SLAVE_ID_MATCH寄存器,可以為每個設備分配唯一的地址。

掉電模式

串行器和解串器都有PDB輸入引腳,用于啟用或進入掉電模式。在掉電模式下,設備可以節省功耗,當數據傳輸恢復時,能夠快速恢復正常工作。

像素時鐘邊緣選擇(TRFB / RRFB)

TRFB和RRFB寄存器用于選擇像素時鐘的邊緣。對于串行器,該寄存器決定數據鎖存的邊緣;對于解串器,該寄存器決定數據選通的邊緣。

上電要求和PDB引腳

上電時,VDDIO電源需要先達到預期的工作電壓,然后再釋放PDB信號。可以通過外部RC網絡確保PDB信號在所有VDD電源穩定后到達。

內置自測試(BIST)

芯片組支持AT-Speed內置自測試功能,可用于測試高速串行鏈路和低速反向通道。通過BISTEN引腳和GPIO0、GPIO1引腳,可以選擇不同的時鐘源和測試頻率。測試結果可以通過PASS引腳和寄存器進行監控。

寄存器映射

芯片組提供了豐富的寄存器,用于配置和監控各種功能。串行器和解串器的寄存器分別用于控制數據傳輸、錯誤檢測、模式選擇、GPIO配置等功能。詳細的寄存器映射信息可以參考數據手冊。

應用與實現

應用信息

芯片組僅支持通過集成的DC平衡解碼方案實現AC耦合互連。在FPD-Link III信號路徑中,需要串聯外部AC耦合電容。為了減少封裝寄生效應導致的信號質量下降,建議使用最小尺寸的AC耦合電容。

典型應用

DS90UB91xQ-Q1芯片組通常用于點對點配置,通過屏蔽雙絞線電纜連接串行器和解串器。在設計時,需要注意電纜和連接器的差分阻抗應為100 Ω,以確保信號的穩定傳輸。

設計要求

- 傳輸介質:建議使用屏蔽雙絞線電纜,芯片組提供內部終端以減少阻抗不連續性。電纜長度取決于電纜質量、連接器、電路板和電氣環境等因素。

- 自適應均衡器 - 損耗補償:自適應均衡器可以補償互連組件的差分插入損耗,但補償能力有限。在確定最大電纜長度時,需要考慮抖動、偏斜、ISI、串擾等因素對信號完整性的影響。

詳細設計流程

在設計過程中,需要參考典型連接圖進行串行器和解串器的連接。同時,要注意電源供應、布局布線等方面的要求,以確保系統的穩定性和性能。

電源供應建議

芯片組設計為從1.8 V的輸入核心電壓電源供電。為了減少不同電路部分之間的開關噪聲影響,一些設備提供了單獨的電源和接地端子。在PCB設計中,通常不需要單獨的電源層,但可以使用外部濾波器為敏感電路(如PLL)提供干凈的電源。

布局設計

布局指南

- 低噪聲電源供應:PCB布局和堆疊應設計為為設備提供低噪聲電源。使用薄電介質(2 - 4 mils)的電源/接地夾層可以提高電源系統的性能。

- 分離高低頻信號:將高頻或高電平的輸入輸出信號分開,以減少雜散噪聲的拾取、反饋和干擾。

- 外部旁路電容:建議使用RF陶瓷和鉭電解電容作為外部旁路電容,RF電容值范圍為0.01 - 0.1 μF,鉭電容值范圍為2.2 - 10 μF。

- 四層板設計:使用至少四層板,包括電源層和接地層。將LVCMOS信號遠離差分線,以防止耦合。

- 差分互連:推薦使用100 Ω的緊密耦合差分對,遵循S、2S和3S規則進行間距設計。

布局示例

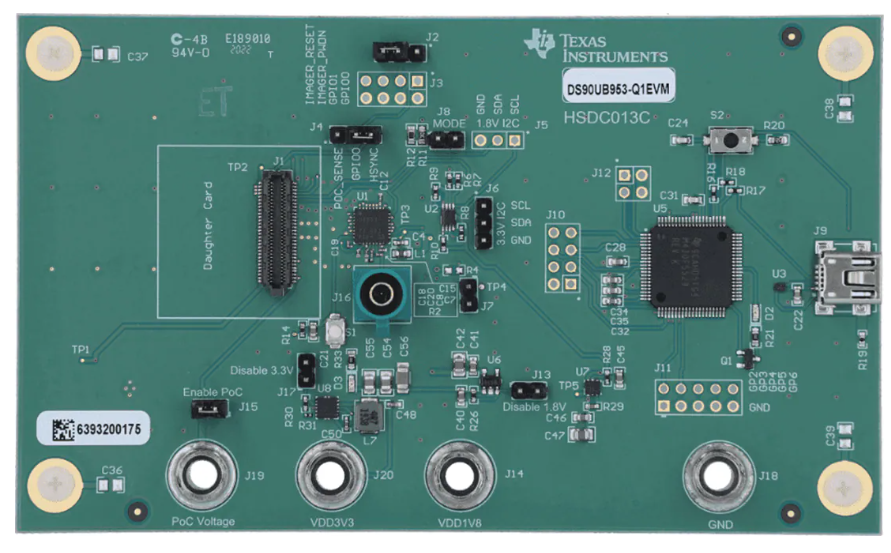

參考DS90UB913Q-Q1串行器和DS90UB914Q-Q1解串器評估套件的布局設計,可以了解正確的布線和焊接技術。同時,要注意WQFN封裝的模板開口和焊盤尺寸的要求。

設備和文檔支持

德州儀器提供了豐富的文檔和社區資源,包括相關文檔、技術支持、工具和軟件等。通過這些資源,可以方便地獲取芯片組的詳細信息和設計指導。

總結

DS90UB91xQ-Q1芯片組以其高速、可靠、低延遲的特點,為汽車電子領域的攝像頭與視頻處理器之間的數據傳輸提供了優秀的解決方案。通過深入了解其特性、應用和設計要點,電子工程師可以更好地利用該芯片組,開發出高性能、穩定可靠的汽車電子系統。在實際設計過程中,要根據具體的應用需求和系統要求,合理選擇參數和配置,確保系統的最優性能。同時,要注意布局布線、電源供應等方面的細節,以提高系統的穩定性和抗干擾能力。希望本文對大家在使用DS90UB91xQ-Q1芯片組進行設計時有所幫助。如果你在設計過程中遇到任何問題,歡迎在評論區留言交流。

-

汽車電子

+關注

關注

3046文章

9065瀏覽量

173067 -

數據傳輸

+關注

關注

9文章

2220瀏覽量

67697

發布評論請先 登錄

DS90UB947-Q1,一款OpenLDI到FPD-Link III橋接器件詳解 pdf

DS90UB91xQ-Q1 10MHz至100MHz、10位和12位直流均衡FPD-link III串行器和解串器數據表

DS90UB953-Q1 FPD-Link III串行器評估模塊技術解析

深入解析DS90UB91xQ-Q1:FPD-Link III的卓越之選

深入解析DS90UB91xQ-Q1:FPD-Link III的卓越之選

評論