一前言

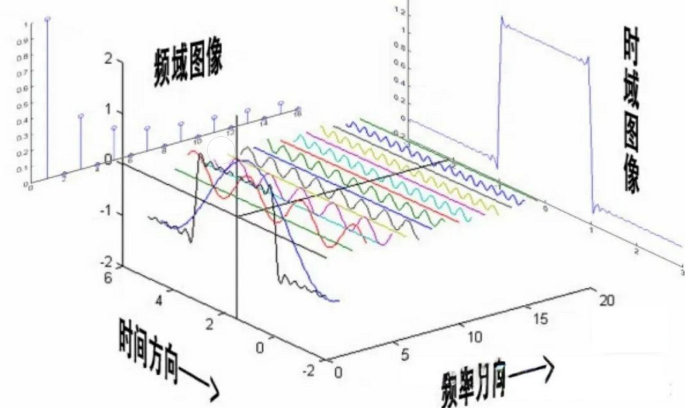

時鐘信號是時序邏輯的基礎,它作為數字電路系統的心臟,在數字電路中具有重要意義。時鐘信號在數字系統中并非完美的方波,其快速邊沿(上升/下降時間)包含了極其豐富的高次諧波成分。這些高次諧波雖然對數字電路的邏輯功能沒有直接影響,但在電磁兼容(EMC)和信號完整性(SI)中帶來了顯著的危害與痛點。

圖1 時鐘

二時鐘高次諧波解決方案

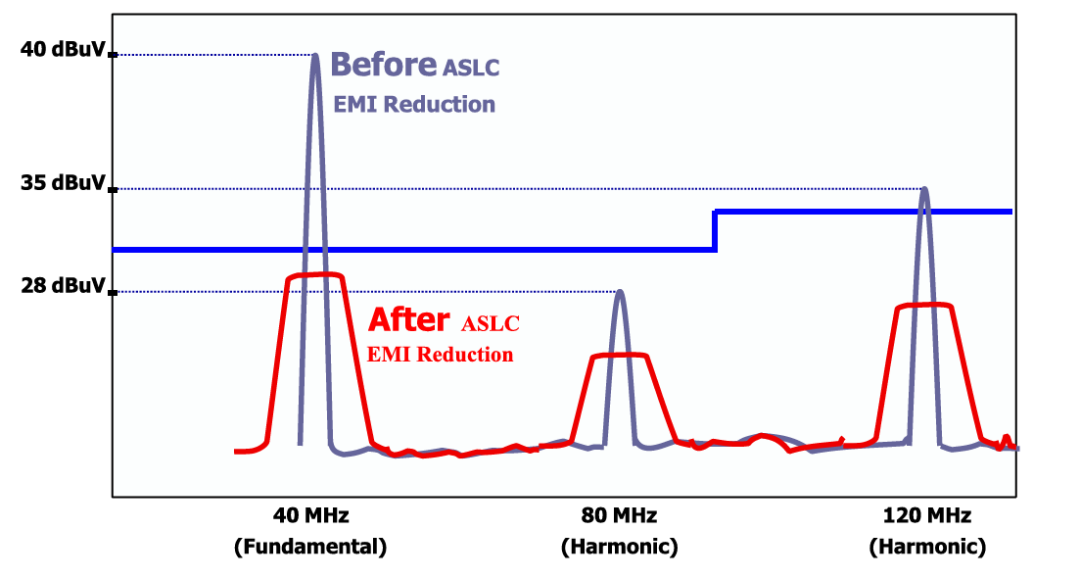

針對這種高次諧波的時鐘最有效的手段就是展頻技術(SSC)。

展頻技術是讓時鐘頻率在極小的范圍內周期性調制,將能量分散到更寬頻帶,從而達到降低尖峰能量。展頻技術可以讓我們從源頭去解決時鐘噪聲問題,針對時鐘的高次諧波效果更好,每次諧波展頻抑制效果都會得到加強。

圖2 展頻效果

現在很多SOC芯片方案都能支持軟件展頻,通過軟件設置對時鐘信號進行調制,從而達到展頻效果。但從很多客戶反饋來看,軟件展頻的效果都不盡人意,從而導致很多工程師對展頻技術失去了信心。

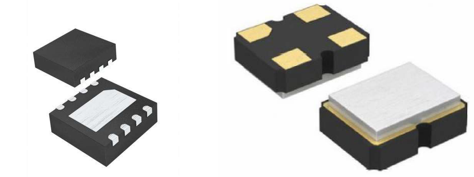

目前比較主流的還是使用硬件展頻去針對時鐘,而硬件展頻一種是展頻IC針對主時鐘(晶振信號)進行展頻后提供給主控;另一種就是展頻晶振,它會帶展頻效果的有源晶振,可以直接輸出帶展頻效果的時鐘信號給主控。

圖3 展頻IC與展頻晶振

三案例分享

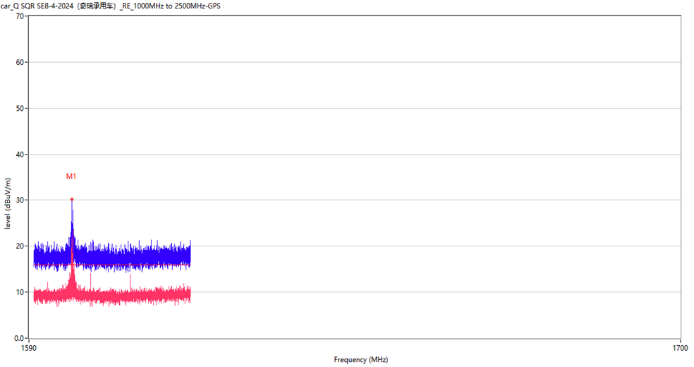

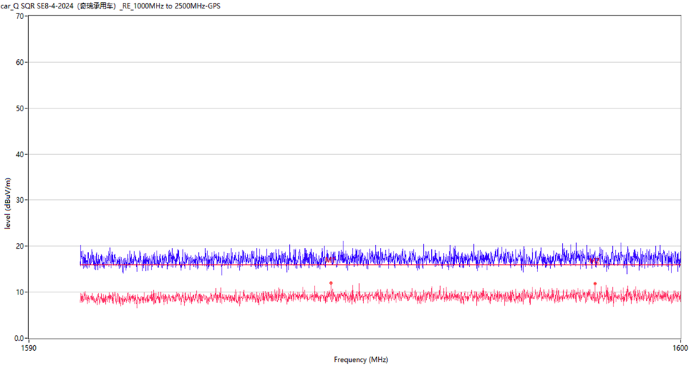

這次分享的是一個車機與中控屏一套的產品,下圖是摸底數據:

圖4 摸底數據

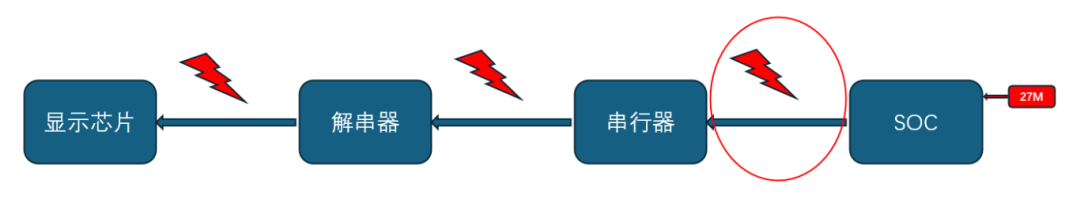

產品測試問題點在1G以上的頻段,頻點為1597M。通過排查我們發現只要插了視頻線就會存在這個頻點,然后近場頻譜測試把問題鎖定在SOC輸出的視頻信號到串行器 (SERializer)這一部分存在對應頻點。

圖5 簡單圖示

針對這里的視頻走線信號進行了RC濾波、屏蔽等措施都沒有效果,發現就算在這一段濾波抑制下來的能量會被串行器(SERializer)進行增強后串行傳輸出去,導致濾波等措施沒有效果。

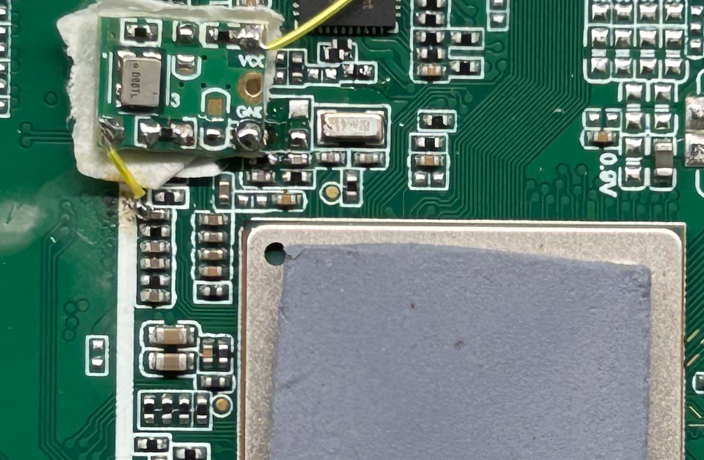

圖6 展頻晶振措施

既然從數據傳輸路徑去抑制沒有效果,那就只能從時鐘源頭去抑制,就用上我們的展頻晶振產品demo對SOC的參考時鐘27M無源晶振進行替換驗證。

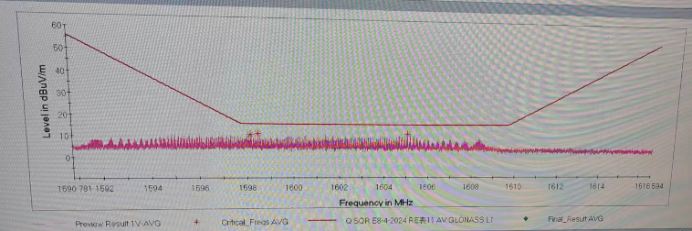

圖7 整改數據

圖8 客戶第三方驗證數據

【分析】:

從源頭時鐘進行展頻,所有參考此時鐘的時鐘信號都會有展頻效果,其高次諧波的時鐘信號展頻效果更優,能量強度抑制更好。串行器 (SERializer)接收到的也是展頻過后的時鐘信號,同時因為它接收到的時鐘信號高次諧波的能量強度更低,就算經過串行器增益過后的能量強度也不會太高。

四總結

時鐘信號的高次諧波是數字系統電磁兼容性設計中的”隱形殺手”。其危害主要在于逐漸嚴格要求的電磁輻射和傳導干擾測試標準中導致產品認證失敗、系統性能下降甚至功能失效。在高速信號時代,時鐘設計、電路選擇、PCB布局布線、電源設計、屏蔽濾波等多個環節采取綜合措施,并在性能和EMC之間找到最佳平衡點,這是一個持續性的挑戰。

-

諧波

+關注

關注

7文章

950瀏覽量

44558 -

時鐘

+關注

關注

11文章

1993瀏覽量

135122 -

Re

+關注

關注

0文章

74瀏覽量

33836

發布評論請先 登錄

高次諧波對電氣設備的危害

AD9957輸入的時鐘頻譜有高次諧波而且奇數次諧波功率基本和主頻一樣

RE測試高頻諧波超標該如何調整?

高次諧波過流保護的原因是什么?怎么解決?

高次諧波的危害

高次諧波過流保護方案

RE時鐘高次諧波解決方案

RE時鐘高次諧波解決方案

評論