高速數據傳輸利器:DS250DF810八通道多速率重定時器的深度解析

在當今高速數據傳輸的時代,信號的完整性和可靠性至關重要。德州儀器(TI)的DS250DF810作為一款具有集成信號調節功能的八通道多速率重定時器,為解決長距離高速串行鏈路中的信號衰減、串擾和抖動等問題提供了強大的解決方案。本文將對DS250DF810進行全面的剖析,包括其特性、應用、工作原理、寄存器配置以及設計注意事項等方面,幫助電子工程師更好地理解和應用這款器件。

文件下載:ds250df810.pdf

一、DS250DF810特性亮點

1. 多速率支持與獨立鎖定

DS250DF810的每個通道都能獨立鎖定在20.2752至25.8Gbps的連續范圍內,同時支持10.3125Gbps、12.5Gbps等子速率。這種廣泛的速率支持使得該器件能夠適應多種不同的高速數據傳輸標準,如IEEE802.3bj 100GbE、Infiniband EDR和OIF CEI - 25G - LR/MR/SR/VSR等電氣接口,為不同的應用場景提供了極大的靈活性。

2. 超低延遲與低功耗設計

在25.78125Gbps的數據速率下,DS250DF810的典型延遲小于500ps,能夠滿足高速數據傳輸對低延遲的嚴格要求。同時,該器件采用單電源供電,無需低抖動參考時鐘,并集成了交流耦合電容,不僅降低了電路板布線的復雜程度,還節省了物料清單(BOM)成本。此外,通過合理配置不同的工作模式,如部分功能的啟用或禁用,可以有效降低功耗,提高系統的能效。

3. 集成均衡與信號調節功能

器件集成了自適應連續時間線性均衡器(CTLE)、自適應判決反饋均衡器(DFE)以及帶有3抽頭有限脈沖響應(FIR)濾波器的低抖動發射器。CTLE和DFE能夠自適應地補償信號在傳輸過程中的損耗和失真,而FIR濾波器則可以對輸出信號進行預 - 失真處理,以進一步提高信號的質量。這種組合式的均衡技術使得DS250DF810能夠在高達35dB的通道損耗下仍能實現穩定的數據傳輸,確保了信號的可靠性和完整性。

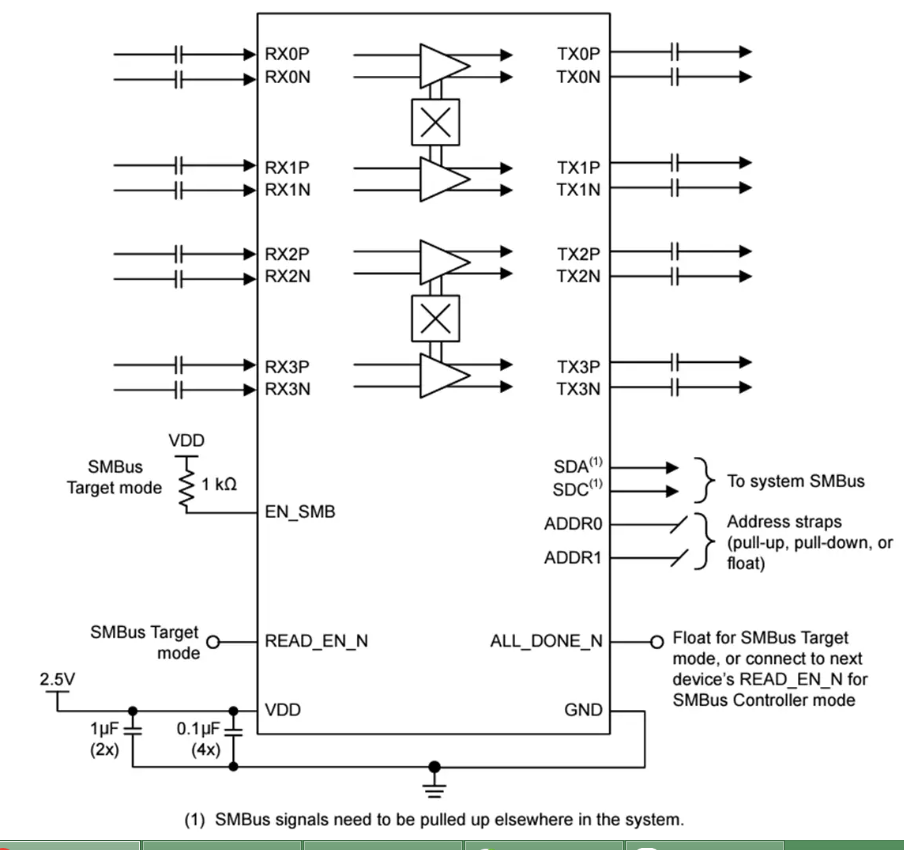

4. 交叉點開關與診斷功能

DS250DF810在每兩組相鄰的通道之間集成了2×2交叉點開關,可實現通道的交叉和扇出功能,為系統設計提供了更多的靈活性和冗余性。此外,器件還配備了非破壞性片上眼圖張開度監視器(EOM)和PRBS模式校驗器/發生器,可用于系統內的診斷和測試,幫助工程師快速定位和解決信號傳輸過程中出現的問題。

二、主要應用場景

1. 背板/中板長度延長

在數據中心、通信設備等大型系統中,背板和中板的信號傳輸距離較長,容易出現信號衰減和串擾等問題。DS250DF810憑借其強大的均衡和重定時功能,能夠有效延長背板和中板上高速串行鏈路的傳輸距離,提高信號的質量和穩定性,確保數據的可靠傳輸。

2. 前端口光學模塊抖動消除

在光學通信系統中,前端口光學模塊的信號抖動會影響系統的性能和可靠性。DS250DF810可以對輸入的高速串行數據進行重定時和抖動消除處理,為后續的光學模塊提供干凈、穩定的信號,從而提高整個光學通信系統的性能。

三、工作原理與關鍵模塊

1. 數據路徑關鍵模塊

DS250DF810的數據路徑主要由AC - 耦合接收器、信號檢測電路、CTLE、可變增益放大器(VGA)、交叉點開關、DFE、時鐘和數據恢復(CDR)、校準時鐘以及帶有FIR濾波器的差分驅動器等關鍵模塊組成。

AC - 耦合接收器和發射器集成了220nF的交流耦合電容,確保了信號的共模電壓兼容性,并消除了系統PCB上對交流耦合電容的需求。信號檢測電路能夠實時監測輸入信號的能量水平,根據信號的有無自動開啟或關閉高速數據路徑的其余部分,從而實現功耗的優化。

2. 自適應均衡器

CTLE是一個完全自適應的均衡器,它在鎖相過程中根據水平眼圖張開度(HEO)和垂直眼圖張開度(VEO)的計算結果進行自適應調整。CTLE由4個階段組成,每個階段具有2位的增益控制,提供了256種不同的增益組合。在CDR鎖定且CTLE自適應完成后,其增益水平將保持不變,直到收到手動重新自適應命令或CDR重新進入鎖相狀態。

DFE是一個5抽頭的均衡器,可以手動啟用并配置為僅在鎖相過程中自適應或連續自適應。通過調整DFE的抽頭極性和權重,可以有效減少串擾、反射和符號間干擾(ISI)的影響,提高信號的質量。

3. 時鐘和數據恢復(CDR)

CDR模塊由鎖相環(PLL)、PPM計數器以及輸入和輸出數據復用器組成,能夠從輸入數據中恢復出干凈的時鐘信號,并對數據進行重定時。CDR的帶寬可以根據需要進行調整,默認情況下,在全速率模式下為5.5MHz(典型值),在子速率模式下為5.3MHz(典型值)。

CDR需要一個25MHz的校準時鐘來運行PPM計數器,該時鐘不用于時鐘和數據恢復,因此對其抖動要求不高。通過編程設置CDR的數據速率,可以使其適應不同的輸入數據速率。

4. 差分驅動器與FIR濾波器

DS250DF810的輸出驅動器配備了一個3抽頭的FIR濾波器,可實現前 - 光標和后 - 光標均衡,以補償輸出通道的頻率相關損耗。FIR濾波器的系數可以通過寄存器進行配置,用戶在配置時需要遵循一定的規則,如系數絕對值之和不超過31,以及前 - 光標和后 - 光標的符號與主光標的符號關系等,以實現不同的濾波效果。

通過調整FIR濾波器的主光標系數,可以控制輸出驅動器的差分電壓幅值(VOD),同時結合前 - 光標和后 - 光標系數的調整,可以實現對輸出信號的進一步均衡和優化。

四、寄存器配置與編程

1. 寄存器類型與功能

DS250DF810具有三種類型的寄存器:全局寄存器、共享寄存器和通道寄存器。全局寄存器主要用于選擇通道寄存器或共享寄存器,以及讀取設備的ID和版本信息;共享寄存器用于設備級的配置、狀態讀取和控制;通道寄存器則用于控制和配置每個獨立通道的特定功能,所有通道的通道寄存器集相同且可以獨立配置。

2. 寄存器編程注意事項

在對寄存器進行編程時,由于許多寄存器被劃分為位字段,因此在修改部分位字段時,需要先讀取寄存器的當前值,修改所需的位后再寫回寄存器。部分寄存器位具有特定的接口約束,如只讀(R)、讀寫(RW)或讀寫自清除(RWSC)等,在編程時需要注意遵循這些約束。

五、設計注意事項

1. 電源設計

在設計電源時,需要確保電源能夠提供符合推薦工作條件的直流電壓、交流噪聲和啟動斜坡時間。可以根據文檔中提供的最大電流值來選擇合適的電源調節器,并進行適當的電源濾波和去耦處理,以滿足器件的電源需求。

2. 布局設計

布局設計對于器件的性能至關重要。去耦電容應盡可能靠近VDD引腳放置,以減少電源噪聲的影響。高速差分信號TXnP/TXnN和RXnP/RXnN應緊密耦合、 skew匹配和阻抗控制,并盡量避免使用過孔。如果必須使用過孔,應采取措施最小化過孔 stub,以提高信號的完整性。

此外,還應在高速差分信號焊盤下方使用GND relief,以抵消焊盤電容,提高信號質量。同時,在器件下方放置GND過孔,將器件連接的GND平面與其他層的GND平面相連,有助于提高器件的散熱性能。

3. 時鐘設計

DS250DF810需要一個25MHz(±100 ppm)的單端CMOS時鐘作為校準時鐘。該時鐘可以通過多個器件的CAL_CLK_IN和CAL_CLK_OUT引腳進行菊花鏈連接,以避免使用多個振蕩器。在設計時鐘輸入電路時,如果振蕩器的輸出為2.5V CMOS,則無需使用交流耦合電容或電阻梯。

六、總結

DS250DF810作為一款功能強大的八通道多速率重定時器,在高速數據傳輸領域具有廣泛的應用前景。其多速率支持、超低延遲、集成均衡和信號調節功能以及豐富的診斷功能,使其成為解決長距離高速串行鏈路信號傳輸問題的理想選擇。通過合理的寄存器配置和精心的設計布局,工程師可以充分發揮DS250DF810的性能優勢,為高速數據傳輸系統的設計提供可靠的保障。

在實際應用中,電子工程師還需要根據具體的系統需求和設計要求,對DS250DF810進行進一步的優化和調整。同時,要密切關注器件的性能指標和工作狀態,及時解決可能出現的問題,以確保整個系統的穩定運行。希望本文能夠為電子工程師在使用DS250DF810進行設計時提供有益的參考和指導。

-

高速數據傳輸

+關注

關注

0文章

297瀏覽量

7227

發布評論請先 登錄

DS250DF810 DS250DF810 25Gbps 多速率 8 通道重定時器

高速數據傳輸利器:DS250DF810八通道多速率重定時器的深度解析

高速數據傳輸利器:DS250DF810八通道多速率重定時器的深度解析

評論