以下文章來源于OpenFPGA,作者碎碎思

TinyFPGA-Bootloader:FPGA 上的開源 USB 引導加載器解決方案

在 FPGA 設計中,一個常見但略顯繁瑣的環節是:如何方便地將新的比特流加載到 FPGA。尤其是在沒有專用 USB-JTAG/編程芯片或者在低成本板卡中,傳統的編程方式可能需要額外硬件或較復雜流程。

而 TinyFPGA?Bootloader 項目正是為了解決這個痛點——它是一個 開源的 USB 引導加載器(bootloader)IP,可直接在 FPGA 的可編程邏輯中實現,從而以 USB 虛擬串口的形式向 SPI Flash 編程上傳比特流。

項目簡介

名稱:TinyFPGA-Bootloader

開源地址:GitHub(由 TinyFPGA 組織維護)

https://github.com/tinyfpga/TinyFPGA-Bootloader

許可證:Apache-2.0

功能:通過 USB 虛擬串口(USB CDC)將主機側的命令發送至 FPGA 內部的 bootloader,再由 bootloader 內部橋接至 SPI Flash,從而完成 FPGA 配置或用戶鏡像加載。

硬件需求示例:

FPGA 板卡需具備 USB_P、USB_N 3.3 V 信號。

FPGA 配置需來源于外部 SPI Flash。

USB_P 信號連接上拉電阻(1.5 kΩ)并建議通過 usb_pu 信號控制。

建議支持多鏡像啟動(bootloader + 用戶鏡像)結構。

核心特點

● 無需額外 USB 轉 SPI 芯片

由于 bootloader 完全在 FPGA 內部邏輯實現,板卡可以省去專用 USB 編程芯片,從而降低成本、簡化硬件設計。

● 使用熟悉的串口方式編程

主機將 FPGA 識別為“虛擬串口設備”,用戶通過簡單的命令即可觸發 bootloader 功能,降低入門門檻。

● 支持用戶鏡像 + bootloader 鏡像分區

該設計支持多鏡像結構:bootloader 位于 SPI Flash 的專用區域,用戶配置位于另一鏡像區,bootloader 在啟動后可跳轉至用戶鏡像,或執行更新機制。

● 板卡元數據存儲機制

SPI Flash 的安全寄存器頁可用于存儲諸如板卡名稱、FPGA 型號、硬件版本、序列號、地址映射等元數據,便于通用軟件識別板卡并自動執行編程。元數據采用 JSON 格式,清晰易讀。

● SPI Flash 編程協議公開

bootloader 支持通過 “Access SPI” 命令在 USB 虛擬串口上執行任意 SPI Flash 訪問操作(寫、讀、擦除等)。設計者可以查看 README 文檔中的完整協議描述。

例程

該項目中有幾款開發板的例程,核心還是自家制作的Tiny系列開發板:

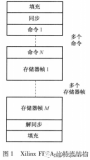

當然也有針對Xilinx A7系列入門開發板例程:

打開后即可查看相關DEMO:

注意:Vivado版本2017

適用場景

低成本 FPGA板卡:希望減少外部編程芯片、簡化 USB 接口設計。

FPGA 教學 / 原型開發:快速將新鏡像下載至板卡,在實驗室或教學環境中尤為便利。

可編程系統 / 多鏡像方案:支持 bootloader + 用戶鏡像結構,適合需要遠程更新或 EEPROM 風格的機制。

硬件開發者希望精簡流程:將編程流程簡化為“插 USB → 虛擬串口 → 下載鏡像”,提升工程效率。

使用建議 &注意事項

在使用前請確認板卡 USB_P/N 信號設計正確、上拉電阻接入、“usb_pu”控制是否支持。

必須保證 FPGA 時鐘系統能產生準確穩定的 48 MHz 給 USB 棧,否則可能導致 USB 連接不可靠。

設計 SPI Flash 容量時建議考慮“多鏡像 + 用戶數據”結構,需要預留足夠空間。

雖然 bootloader 功能強大,但安全機制(如加密鏡像、鏡像簽名、保護區)需由用戶自行實現。

若需將該 bootloader 集成至大型 FPGA/SoC 項目,請評估板卡資源占用、邏輯干擾和時序影響。

總結

TinyFPGA-Bootloader 是一個非常實用、工程友好、開源可信的解決方案,適合在 FPGA 板卡設計中快速實現 USB 引導加載功能。它不僅降低了硬件復雜性,也顯著簡化了鏡像下載、更新與板卡上板流程。這對于教學、原型開發、板卡小批量生產都是一個極佳選擇。

注意大bit流的下載時間~

倉庫地址

https://github.com/tinyfpga/TinyFPGA-Bootloader

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636199 -

開源

+關注

關注

3文章

4203瀏覽量

46120 -

比特流

+關注

關注

0文章

11瀏覽量

8398 -

GitHub

+關注

關注

3文章

488瀏覽量

18660

原文標題:不用 JTAG 也能刷 FPGA:TinyFPGA-Bootloader 讓比特流加載更簡單

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

了解FPGA比特流結構

如何使用IMPACT在FPGA xilinx中下載比特流

中途向ICAP中止寫入部分比特流

怎么在我的比特流中攻擊BRAM

如何集成Pynq FPGA教程或與Pynq通信?

無法在spi flash中加載比特流

怎么將Microblaze processsor比特串文件下載到FPGA中?

怎么在Virtex-7 FPGA上下載比特流?

請問如何在沒有靜態路由的情況下生成部分比特流?

是否需要在flash上??切換黃金比特流和多重比特流的位置?

使用IMPACT(ISE)將比特流下載到Zynq設備中而無需啟動ARM?

Zynq開發板FPGA比特流文件下載方式

使用加密和身份驗證來保護UltraScale/UltraScale+ FPGA比特流

使用TinyFPGA-Bootloader將比特流加載到FPGA

使用TinyFPGA-Bootloader將比特流加載到FPGA

評論