HDMI(High Definition Multimedia Interface,高清晰度多媒體接口)是一種全數(shù)字化視頻和音頻傳輸接口,可以傳輸未壓縮的音頻及視頻信號。HDMI向下兼容DVI(數(shù)字視頻接口,只能用來傳輸視頻,而不能同時傳輸音頻)。DVI 和HDMI 接口協(xié)議在物理層均使用TMDS 標(biāo)準(zhǔn)傳輸數(shù)據(jù)。

雖然本文案例是直接通過FPGA控制ADV7513芯片實現(xiàn)HDMI音視頻輸出,不需要用RTL去實現(xiàn)TMDS算法,但是TMDS是HDMI技術(shù)的基礎(chǔ),了解TMDS算法和數(shù)據(jù)傳輸?shù)臅r序有助于用戶更好的理解和控制ADV7513器件。

1 了解TMDS

TMDS(Transition Minimized Differential Signaling最小化傳輸差分信號) 是由Silicon Image公司開發(fā)的一項高速數(shù)據(jù)傳輸技術(shù),目的是減少信號跳變(從而降低電磁干擾),實現(xiàn)直流平衡,以及抗干擾傳輸。

TMDS傳輸系統(tǒng)分為兩個部分:發(fā)送端(Source)和接收端(Sink)。HDMI的數(shù)據(jù)傳輸擁有三個TMDS通道,每個通道的傳輸信號如下:

HDMI通過時分復(fù)用技術(shù),在視頻信號的消隱期內(nèi)將音頻和輔助數(shù)據(jù)打包插入,與視頻數(shù)據(jù)一起通過TMDS通道傳輸。HDMI的某一幀的數(shù)據(jù)傳輸參考圖如下:

可見HDMI的數(shù)據(jù)傳輸分三個傳輸階段(控制期、數(shù)據(jù)島期、視頻數(shù)據(jù)期),每個階段傳輸?shù)臄?shù)據(jù)如下:

視頻數(shù)據(jù)期(Video Data Period):這是最主要的階段,用于傳輸有效的像素數(shù)據(jù)。TMDS通道2傳輸B(藍(lán)色)分量數(shù)據(jù),TMDS通道1傳輸G(綠色)分量數(shù)據(jù),TMDS通道0傳輸R(紅色)分量數(shù)據(jù)。

數(shù)據(jù)島期(Data Island Period):發(fā)生在行消隱期(HBlank)和場消隱期(VBlank)內(nèi),但避開最開始的控制期。用于傳輸音頻數(shù)據(jù)和輔助數(shù)據(jù),還包括HSYNC行同步和VSYNC場同步信號。

控制期(Control Period):發(fā)生在行消隱期(HBlank) 和場消隱期(VBlank) 的開始部分。傳輸2位的同步控制信號(HSYNC行同步和VSYNC場同步)和前導(dǎo)碼(Preamble)。

總結(jié)HDMI的TMDS數(shù)據(jù)傳輸過程: TMDS發(fā)送端收到控制器(FPGA)傳來的視頻/音頻/控制數(shù)據(jù),然后對這些數(shù)據(jù)進(jìn)行編碼和并/串轉(zhuǎn)換,再將數(shù)據(jù)分別分配到獨立的傳輸通道發(fā)送出去。接收端(顯示器)接收來自發(fā)送端的串行信號,對其進(jìn)行解碼和串/并轉(zhuǎn)換,然后發(fā)送到顯示器的控制端。與此同時也接收時鐘信號,以實現(xiàn)同步。

下面通過對比單端傳輸和差分傳輸?shù)牟煌瑏韼椭x者理解TMDS為何采用差分方式傳輸信號。

單端傳輸:用一根信號線對GND的電壓值來表示邏輯"0"和"1";

差分傳輸:用兩根信號線來傳輸一路信號,兩根信號線上傳輸?shù)男盘柗迪嗟龋辔徊顬?80°(極性相反),用它們的差值來表示邏輯"0"和"1"。

差分傳輸有利于消除共模干擾(差分傳輸?shù)膬筛€通常布在一起,當(dāng)其中一方受干擾時,另一方也受到同樣的干擾。這樣,在采樣時能夠相互抵消,從而減小干擾,增強(qiáng)抗干擾能力)。

2 HDMI 接口定義

HDMI自問世以來,為了適應(yīng)不同設(shè)備的需求,發(fā)展出了幾種物理接口類型。同時,所有類型的HDMI接口都基于相同的核心信號定義(TMDS通道等19個引腳),只是物理尺寸和針腳排列不同,最常見的是Type A(標(biāo)準(zhǔn)HDMI接口)引腳排列和定義如下:

注:

1. 每個TMDS數(shù)據(jù)對(正、負(fù))和時鐘對都有自己的專用屏蔽線(Pin 2, 5, 8, 11),這對于保證高速信號傳輸?shù)耐暾院蜏p少干擾至關(guān)重要。

2. EDID (Extended Display Identification Data 即擴(kuò)展顯示識別數(shù)據(jù)): 源設(shè)備通過DDC通道(Pin 15-SCL, Pin 16-SDA)讀取顯示器/電視的分辨率、刷新率、音頻支持等信息,從而正確地設(shè)置視頻輸出參數(shù)。

3. HDCP(High-bandwidth Digital Content Protection,即高帶寬數(shù)字內(nèi)容保護(hù)協(xié)議):HDCP是一種由Intel開發(fā)的數(shù)字版權(quán)管理技術(shù),主要用于保護(hù)數(shù)字音頻和視頻內(nèi)容在傳輸過程中的安全,防止未經(jīng)許可的復(fù)制或非法錄制。HDCP的工作原理是通過加密傳輸信號,確保只有經(jīng)過授權(quán)的接收設(shè)備才能解密并顯示內(nèi)容。在HDCP協(xié)議中,EDID扮演著關(guān)鍵角色。源設(shè)備會檢查接收設(shè)備的EDID以確認(rèn)其是否支持HDCP,如果發(fā)現(xiàn)不兼容或無效的EDID,源設(shè)備將不會發(fā)送加密內(nèi)容,從而保護(hù)了內(nèi)容的版權(quán)。

3 DE10-Nano的HDMI電路

DE10-Nano 的 HDMI 局部特細(xì)圖:

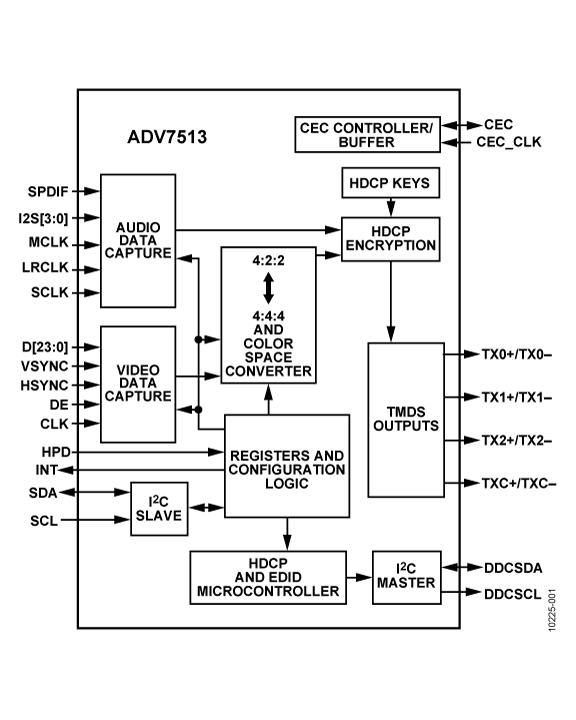

開發(fā)板通過Analog Devices的ADV7513為用戶提供高性能HDMI發(fā)射器,其支持HDMI v1.4功能(包括支持3D視頻,支持分辨率最高達(dá)1080p和UXGA,像素時鐘高達(dá)165MHz等)。ADV7513通過串行I2C總線接口進(jìn)行控制,該接口連接到Cyclone V SoC FPGA上的引腳。電路原理圖如下所示。

有關(guān)ADV7513 HDMI TX的詳細(xì)信息,請訪問制造商網(wǎng)站或在DE10-Nano 資料壓縮包(System CD)的DatasheetHDMI文件夾中查看。

ADV7513 與FPGA之間的引腳連接如下:

下表列出了HDMI接口引腳分配和信號名稱:

-

FPGA

+關(guān)注

關(guān)注

1656文章

22317瀏覽量

631100 -

HDMI

+關(guān)注

關(guān)注

34文章

1876瀏覽量

158993 -

音視頻

+關(guān)注

關(guān)注

4文章

577瀏覽量

31218

原文標(biāo)題:2-DE10-Nano的HDMI方塊移動案例——HDMI接口介紹(含TMDS)

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何用FPGA控制ADV7513實現(xiàn)HDMI畫面顯示和音頻播放

ADV7513芯片是否支持DE模式的RGB輸入,是否可以在內(nèi)部產(chǎn)生Hsync和Vsync信號呢?

2款音視頻處理芯片

ADV7513是HDMI發(fā)送器,是AD9889的升級版本

例說FPGA連載89:多分辨率HDMI顯示驅(qū)動設(shè)計之功能概述

ADV7513具有哪些特性參數(shù)應(yīng)用?

基于DK-VIDEO-GW2A18-PG484開發(fā)板的HDMI視頻縮小DEMO系統(tǒng)

ADV7513 165 MHz高性能HDMI發(fā)送器

高性能HDMI發(fā)送器ADV7513的主要特性及應(yīng)用電路

ADV7513:165 MHz,高性能HDMI傳輸數(shù)據(jù)Sheet

適用于任何OS平臺(Exe)的ADV7513 HDMI發(fā)送器庫API源代碼

AN-1270: 基于ADV7511/ADV7511W/ADV7513的視頻發(fā)生器

通過FPGA控制ADV7513芯片實現(xiàn)HDMI音視頻輸出

通過FPGA控制ADV7513芯片實現(xiàn)HDMI音視頻輸出

評論