在當(dāng)今的電子設(shè)計領(lǐng)域,模擬 - 數(shù)字轉(zhuǎn)換器(ADC)扮演著至關(guān)重要的角色,尤其是在需要高精度數(shù)據(jù)采集和處理的應(yīng)用中。今天,我們將深入探討德州儀器(Texas Instruments)的一款高性能ADC——ADS850,它以其出色的性能和豐富的特性,成為眾多應(yīng)用場景的理想選擇。

文件下載:ads850.pdf

一、ADS850概述

ADS850是一款具有高動態(tài)范圍的14位ADC,它采用全差分輸入結(jié)構(gòu),支持單端或差分輸入接口,輸入范圍靈活可變。該轉(zhuǎn)換器運用數(shù)字誤差校正技術(shù),確保了14位的線性度,并通過校準(zhǔn)程序校正電容和增益失配問題。此外,ADS850還配備了高帶寬的跟蹤保持電路,在奈奎斯特速率及以上都能提供出色的雜散性能。

二、關(guān)鍵特性剖析

2.1 高精度與高性能

- 高無雜散動態(tài)范圍(SFDR):在奈奎斯特頻率下可達(dá)85dB,這意味著它能夠有效抑制雜散信號,為系統(tǒng)提供更純凈的數(shù)字輸出。

- 高信噪比(SNR):達(dá)到76dB,能夠準(zhǔn)確地捕捉微弱信號,提高信號檢測的精度。

- 低功耗:僅250mW,適合對功耗要求較高的應(yīng)用場景,延長設(shè)備的續(xù)航時間。

2.2 靈活的輸入配置

- 輸入方式多樣:支持差分或單端輸入,可根據(jù)實際應(yīng)用需求靈活選擇。

- 輸入范圍靈活:具有靈活的輸入范圍,還配備過范圍指示器,方便用戶及時了解輸入信號是否超出范圍。

- 參考源可選:可選擇內(nèi)部或外部參考源,滿足不同應(yīng)用場景的需求。

2.3 邏輯兼容性

支持+3V/+5V邏輯I/O,與多種邏輯電路兼容,方便與其他設(shè)備進(jìn)行接口設(shè)計。

三、應(yīng)用領(lǐng)域廣泛

3.1 通信領(lǐng)域

在中頻(IF)和基帶數(shù)字化處理中,ADS850的高動態(tài)范圍和高精度能夠有效提高信號處理的質(zhì)量,確保通信系統(tǒng)的穩(wěn)定運行。

3.2 成像領(lǐng)域

在CCD成像掃描儀和紅外成像等應(yīng)用中,它能夠準(zhǔn)確地將模擬圖像信號轉(zhuǎn)換為數(shù)字信號,為圖像的處理和分析提供可靠的數(shù)據(jù)支持。

3.3 測試測量領(lǐng)域

在測試儀器儀表中,ADS850的高精度和低噪聲特性使其能夠滿足各種精確測量的需求,提高測試結(jié)果的準(zhǔn)確性。

四、電氣特性詳解

4.1 分辨率與溫度范圍

ADS850的分辨率為14位,指定的工作溫度范圍為 -40°C至 +85°C,能夠適應(yīng)較為惡劣的工作環(huán)境。

4.2 轉(zhuǎn)換特性

- 采樣率:最高可達(dá)10MSPS,能夠快速地對模擬信號進(jìn)行采樣,滿足高速數(shù)據(jù)采集的需求。

- 數(shù)據(jù)延遲:僅7個時鐘周期,確保數(shù)據(jù)能夠及時輸出,減少系統(tǒng)的響應(yīng)時間。

4.3 模擬輸入特性

- 輸入范圍:單端輸入范圍和差分輸入范圍可根據(jù)參考電壓的不同進(jìn)行調(diào)整,具有較強的靈活性。

- 輸入電容:僅20pF,對輸入信號的影響較小,有利于提高信號的傳輸質(zhì)量。

- 輸入帶寬:-3dBFS輸入帶寬可達(dá)270MHz,能夠處理高頻信號。

4.4 動態(tài)特性

- 差分線性誤差:在f = 4.8MHz時,最大誤差為±1.0 LSB,保證了轉(zhuǎn)換的線性度。

- 無雜散動態(tài)范圍(SFDR):在f = 4.8MHz、-1dB輸入時,4Vp-p輸入范圍下可達(dá)75 - 85dBFS,2Vp-p輸入范圍下可達(dá)82dBFS。

- 信噪比(SNR):在f = 4.8MHz、-1dB輸入時,4Vp-p輸入范圍下可達(dá)71 - 76dBFS,2Vp-p輸入范圍下可達(dá)73dBFS。

五、引腳配置與功能

ADS850采用TQFP - 48封裝,引腳功能豐富,下面介紹幾個關(guān)鍵引腳:

- +Vs:+5V電源引腳,為芯片提供穩(wěn)定的電源供應(yīng)。

- GND:接地引腳,確保芯片的電氣接地。

- CLK:轉(zhuǎn)換時鐘輸入引腳,控制芯片的采樣和轉(zhuǎn)換操作。

- CAL:校準(zhǔn)引腳,當(dāng)脈沖為高電平時,將ADC置于校準(zhǔn)模式。

- OVR:過范圍指示器引腳,用于指示輸入信號是否超出范圍。

六、校準(zhǔn)過程與注意事項

校準(zhǔn)過程對于ADS850的性能至關(guān)重要。校準(zhǔn)程序通過一個寬度至少為2個時鐘周期的正脈沖啟動。一旦校準(zhǔn)開始,時鐘必須連續(xù)運行,電源和參考源必須保持穩(wěn)定。校準(zhǔn)寄存器在CAL信號的上升沿復(fù)位,實際校準(zhǔn)過程在CAL信號的下降沿開始。在10MSPS的采樣率下,校準(zhǔn)在32,775個周期結(jié)束,即CAL = 3.28ms。在校準(zhǔn)期間,CAL_BUSY信號保持高電平,ADC的數(shù)字輸出引腳被強制為零,輸入(IN和IN)被禁用。校準(zhǔn)完成后,CAL_BUSY信號變?yōu)榈碗娖剑?個周期后或總共32,775個時鐘周期后,輸出端將出現(xiàn)有效數(shù)據(jù)。如果時鐘發(fā)生變化或溫度變化超過±20°C,應(yīng)重新進(jìn)行校準(zhǔn)以保持性能。

七、輸入驅(qū)動配置

7.1 AC - 耦合輸入配置

這是ADS850最常見的接口配置之一。通過將VREF引腳連接到SEL引腳,可將滿量程輸入范圍定義為2Vp - p。使用低失真電壓反饋放大器OPA642將信號以單端形式交流耦合到ADS850。為了使ADS850在滿量程輸入信號擺動下正常工作,需要對放大器的零中心模擬信號進(jìn)行電平轉(zhuǎn)換,以滿足ADC的輸入范圍要求。通過在驅(qū)動放大器的輸出和轉(zhuǎn)換器的輸入之間使用直流阻斷電容,可以實現(xiàn)簡單的電平轉(zhuǎn)換方案。在這種配置中,頂部和底部參考(REFT,REFB)分別提供+3V和+2V的輸出電壓,使用兩個2kΩ的電阻對創(chuàng)建約+2.5V的共模電壓,將ADS850的輸入(IN,IN)偏置到所需的直流電壓。交流耦合的優(yōu)點是驅(qū)動放大器仍然以接地為基準(zhǔn)的信號擺動工作,這將使失真性能保持在最佳狀態(tài),因為信號擺動保持在運算放大器的線性區(qū)域內(nèi),并且可以保持到電源軌的足夠裕量。考慮使用反相增益配置來消除放大器的共模抑制比(CMR)引起的誤差。在運算放大器的輸出和ADS850的輸入之間添加一個小的串聯(lián)電阻($R_{S}$)在幾乎所有接口配置中都是有益的,它將運算放大器的輸出與容性負(fù)載解耦,避免增益峰值,從而減少噪聲。為了獲得最佳的雜散和失真性能,電阻值應(yīng)保持在100Ω以下。此外,串聯(lián)電阻與100pF電容一起構(gòu)成一個無源低通濾波器,限制寬帶噪聲的帶寬,有助于提高信噪比(SNR)性能。

7.2 DC - 耦合無電平轉(zhuǎn)換

在某些應(yīng)用中,模擬輸入信號可能已經(jīng)偏置在符合ADS850所選輸入范圍和參考電平的電平上。在這種情況下,只需為所選輸入(IN或IN)提供足夠低的源阻抗即可。由于寬帶運算放大器的輸出阻抗在很寬的頻率范圍內(nèi)保持較低,因此應(yīng)始終考慮使用寬帶運算放大器。對于那些需要驅(qū)動放大器提供信號放大(增益≥3)的應(yīng)用,考慮使用去補償電壓反饋運算放大器OPA686。

7.3 DC - 耦合有電平轉(zhuǎn)換

在一些應(yīng)用中,信號路徑的帶寬需要包括直流,此時信號必須直流耦合到ADC。為了實現(xiàn)這一點,接口電路必須提供直流電平轉(zhuǎn)換。如圖2所示的電路采用運算放大器OPA681將以地為中心的輸入信號與所需的直流偏移相加。ADS850通常以+2.5V的共模電壓工作,該電壓在梯形電阻的中心抽頭處建立,并連接到轉(zhuǎn)換器的$\overline{IN}$輸入。OPA681以反相配置工作,電阻$R{1}$和$R{2}$設(shè)置OPA691的直流偏置電平。由于運算放大器的噪聲增益為+2V/V,假設(shè)$R{F}=R{IN}$,施加到其同相輸入的直流偏移電壓必須分壓到+1.25V,從而產(chǎn)生+2.5V的直流輸出電壓。ADS850的IN和$\overline{IN}$輸入之間的直流電壓差實際上會產(chǎn)生一個偏移,可以通過調(diào)整電阻$R{1}$和$R{2}$的值來校正。運算放大器的偏置電流也可能導(dǎo)致不希望的偏移。選擇合適的運算放大器時,應(yīng)考慮輸入偏置電流、輸出電壓擺動、失真和噪聲規(guī)格等因素。需要注意的是,在這個例子中,整個信號相位被反轉(zhuǎn),為了恢復(fù)原始信號極性,可以交換IN和IN的連接。

7.4 單端到差分配置(變壓器耦合)

為ADS850選擇最合適的接口電路時,必須了解性能要求。如果特定應(yīng)用需要交流耦合輸入,則下一步是確定施加信號的方法,即單端或差分。差分輸入配置可能具有明顯的優(yōu)勢,因為在差分模式下,信號擺動可以減小到單端驅(qū)動所需擺動的一半,從而實現(xiàn)良好的SFDR性能。其次,通過差分驅(qū)動ADS850,可以減少偶次諧波。圖3顯示了建議的變壓器耦合接口電路的原理圖。跨次級側(cè)的電阻($R{T}$)應(yīng)設(shè)置為實現(xiàn)輸入阻抗匹配(例如,$R{T}=n^{2} \cdot R_{G}$)。

八、參考源操作

ADS850集成了一個帶隙參考電路,通過簡單選擇相應(yīng)的引腳配置,可以提供+1V或+2V的參考輸出。為了獲得更大的設(shè)計靈活性,內(nèi)部參考源可以關(guān)閉,并使用外部參考電壓。表I提供了可能的參考選項和引腳配置的概述。

| 模式 | 輸入范圍 | SEL | VREF | REFB | REFT |

|---|---|---|---|---|---|

| 內(nèi)部2Vp - p | VREF | SEL | NC | NC | |

| 內(nèi)部4Vp - p | GND | NC | NC | NC | |

| 外部2V < FSR < 4V | +VS | 1V < FSR < 2V | NC | NC | |

| 外部(REFB – REFT) ? 2 | +VS | GND | 1.5V < REFB < 2V | 2V < REFT < 3.5V |

內(nèi)部參考電路的簡單模型如圖4所示,內(nèi)部模塊包括1V帶隙電壓參考、緩沖器、電阻參考梯形網(wǎng)絡(luò)以及為頂部和底部參考提供必要電流到內(nèi)部節(jié)點的驅(qū)動器。如圖所示,緩沖器的輸出出現(xiàn)在$V{REF}$引腳。ADS850的滿量程輸入跨度由$V{REF}$引腳的電壓決定,根據(jù)公式:$Full - Scale Input Span = 2 \cdot V_{REF}$。需要注意的是,該放大器的電流驅(qū)動能力限制在約1mA,不應(yīng)用于驅(qū)動低負(fù)載。可編程參考電路由施加到選擇引腳(SEL)的電壓控制。

頂部參考(REFT)和底部參考(REFB)主要用于外部旁路。為了在所有參考配置下正常工作,必須為參考引腳提供可靠的旁路,以盡量減少時鐘饋通。圖5顯示了推薦的參考去耦配置。

此外,共模電壓(CMV)可以用作參考電平,為驅(qū)動電路提供適當(dāng)?shù)钠啤H欢仨氉⒁獠灰^度加載該節(jié)點,因為它沒有緩沖且具有高阻抗。圖6給出了另一種生成共模電壓的方法,通過在頂部和底部參考引腳之間放置兩個外部精密電阻(公差為1%或更好),共模電平將出現(xiàn)在中點。頂部和底部參考的輸出緩沖器設(shè)計為提供約2mA的輸出電流。

九、外部參考源操作

根據(jù)應(yīng)用需求,使用外部參考源操作ADS850可能是有利的。如果外部參考電路在漂移和精度方面更優(yōu)越,則可以提高直流精度。要使用外部參考源,用戶必須禁用內(nèi)部參考源,如圖7所示。通過將SEL引腳連接到$+V{S}$,內(nèi)部邏輯將關(guān)閉內(nèi)部參考源。同時,內(nèi)部參考緩沖器的輸出與$V{REF}$引腳斷開,此時必須用外部參考源驅(qū)動$V_{REF}$引腳。需要注意的是,應(yīng)保持與內(nèi)部參考源操作類似的旁路方案。

十、數(shù)字輸入與輸出

10.1 過范圍指示(OVR)

ADS850的一個重要特性是其“過范圍”數(shù)字輸出(OVR)引腳。該引腳可用于監(jiān)測任何超出范圍的情況,每當(dāng)施加的模擬輸入電壓超過輸入范圍(由$V_{REF}$設(shè)置)時,就會發(fā)生這種情況。當(dāng)輸入電壓在定義的輸入范圍內(nèi)時,OVR輸出為低電平;當(dāng)輸入電壓超出輸入范圍時,OVR輸出變?yōu)楦唠娖剑摧斎腚妷旱陀诘撞繀⒖茧妷夯蚋哂陧敳繀⒖茧妷簳r。OVR將保持有效狀態(tài),直到模擬輸入返回其正常信號范圍并完成另一次轉(zhuǎn)換。結(jié)合MSB及其補碼與OVR,可以構(gòu)建一個簡單的線索邏輯,用于檢測過范圍和欠范圍條件,如圖8所示。需要注意的是,OVR是一個數(shù)字輸出,它與模擬信號的特定采樣時刻對應(yīng)的位信息一起更新,因此,OVR數(shù)據(jù)與數(shù)字?jǐn)?shù)據(jù)受到相同的流水線延遲(延遲)影響。

10.2 時鐘輸入要求

時鐘抖動對高速、高分辨率ADC的SNR性能至關(guān)重要。它會導(dǎo)致孔徑抖動($t{A}$),從而增加被轉(zhuǎn)換信號的噪聲。ADS850在CLK輸入的上升沿對輸入信號進(jìn)行采樣,因此該邊沿的抖動應(yīng)盡可能小。抖動噪聲對總SNR的貢獻(xiàn)由以下公式給出:$JitterSNR = 20 log \frac{1}{2 \pi f{IN} t{A}}$(rms信號到rms噪聲),其中$f{IN}$是輸入信號頻率,$t{A}$是均方根時鐘抖動。特別是在欠采樣應(yīng)用中,應(yīng)特別考慮時鐘抖動。為了實現(xiàn)最高性能水平,時鐘輸入應(yīng)被視為模擬輸入。時鐘信號的任何過沖或下沖都可能導(dǎo)致性能下降。在高采樣率數(shù)字化時,時鐘應(yīng)具有50%的占空比($t{H}=t_{L}$),以及2ns或更短的快速上升和下降時間。

10.3 數(shù)字輸出特性

ADS850的數(shù)字輸出設(shè)計為與高速TTL和CMOS邏輯系列兼容。數(shù)字輸出的驅(qū)動級通過單獨的電源引腳VDRV供電,該引腳不與模擬電源引腳連接。通過調(diào)整VDRV上的電壓,數(shù)字輸出電平將相應(yīng)變化。因此,可以在+5V模擬電源下操作ADS850,同時將數(shù)字輸出連接到3V邏輯。

建議盡量降低數(shù)據(jù)線上的容性負(fù)載(≤15pF)。較大的容性負(fù)載在輸出變化時需要更高的充電電流,這些高電流浪涌可能會反饋到ADS850的模擬部分,影響性能。如有必要,可以使用外部緩沖器或鎖存器,它們可以將ADS850與總線上的任何數(shù)字噪聲活動隔離開來,避免高頻噪聲反饋。此外,在每個數(shù)據(jù)線上串聯(lián)電阻可能有助于保持ADS850的交流性能,電阻值的選擇取決于轉(zhuǎn)換器看到的容性負(fù)載,100Ω至200Ω的電阻值將限制輸出級在輸出電平從低到高或從高到低變化時為寄生電容充電所需提供的瞬時電流。

十一、接地與去耦

在高頻設(shè)計中,正確的接地和旁路、短引線長度以及使用接地平面尤為重要。建議使用多層PCB板以獲得最佳性能,因為它們具有明顯的優(yōu)勢,如最小化接地阻抗、通過接地層分隔信號層等。建議將ADS850的模擬和數(shù)字接地引腳在IC處連接在一起,并僅連接到系統(tǒng)的模擬接地。

ADS850具有模擬和數(shù)字電源引腳,但應(yīng)將轉(zhuǎn)換器視為模擬組件,所有電源引腳應(yīng)由模擬電源供電。這將確保最一致的結(jié)果,因為數(shù)字電源線通常攜帶高水平的噪聲,否則這些噪聲可能會耦合到轉(zhuǎn)換器中,降低可實現(xiàn)的性能。

由于流水線架構(gòu),轉(zhuǎn)換器還會產(chǎn)生高頻電流瞬變和噪聲,并反饋到電源和參考線中。因此,必須對電源和參考引腳進(jìn)行充分的旁路。圖9顯示了模擬電源的推薦去耦方案。在大多數(shù)情況下,0.1μF的陶瓷芯片電容足以在很寬的頻率范圍內(nèi)保持低阻抗,其有效性在很大程度上取決于與各個電源引腳的接近程度,因此應(yīng)盡可能靠近電源引腳放置。此外,應(yīng)在PCB板上靠近轉(zhuǎn)換器電路的位置放置一個較大尺寸的雙極性電容(1μF至22μF)。

十二、總結(jié)與展望

ADS850作為一款高性能的14位ADC,憑借其高動態(tài)范圍、高精度、低功耗和靈活的輸入輸出配置等優(yōu)點,在通信、成像、測試測量等眾多領(lǐng)域具有廣泛的應(yīng)用前景。在實際設(shè)計中,我們需要根據(jù)具體的應(yīng)用需求,合理選擇輸入驅(qū)動配置、參考源操作方式,并注意時鐘輸入、數(shù)字輸出、接地與去耦等方面的問題,以充分發(fā)揮ADS850的性能優(yōu)勢。隨著電子技術(shù)的不斷發(fā)展,相信ADS850將在更多的應(yīng)用場景中展現(xiàn)出其卓越的性能,為電子工程師們帶來更多的設(shè)計靈感和解決方案。

你在使用ADS850的過程中遇到過哪些問題?或者你對它在特定應(yīng)用中的表現(xiàn)有什么獨特的見解?歡迎在評論區(qū)分享你的

-

adc

+關(guān)注

關(guān)注

100文章

7511瀏覽量

555931 -

數(shù)據(jù)采集

+關(guān)注

關(guān)注

41文章

8038瀏覽量

120881 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4013瀏覽量

130100 -

高帶寬

+關(guān)注

關(guān)注

0文章

49瀏覽量

7945 -

數(shù)字轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

347瀏覽量

28761

發(fā)布評論請先 登錄

ADS850 pdf datasheet

ADS850高動態(tài)范圍、14位模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

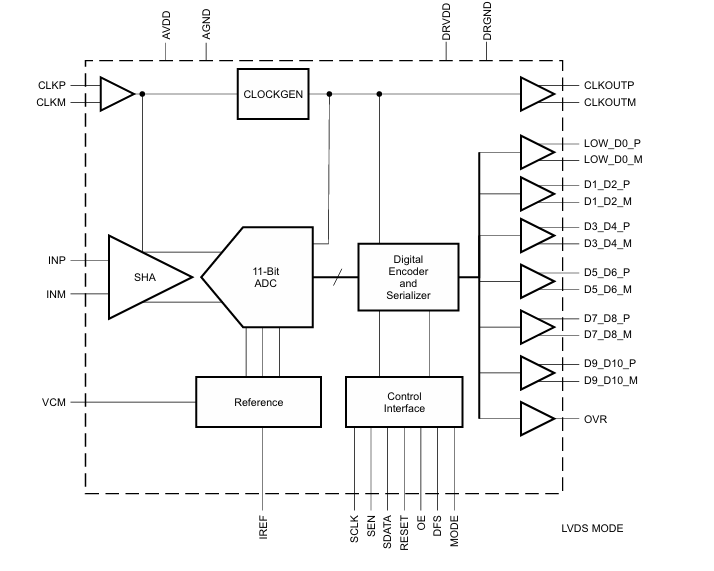

深入解析ADS5517:高性能11位200 MSPS ADC的卓越之選

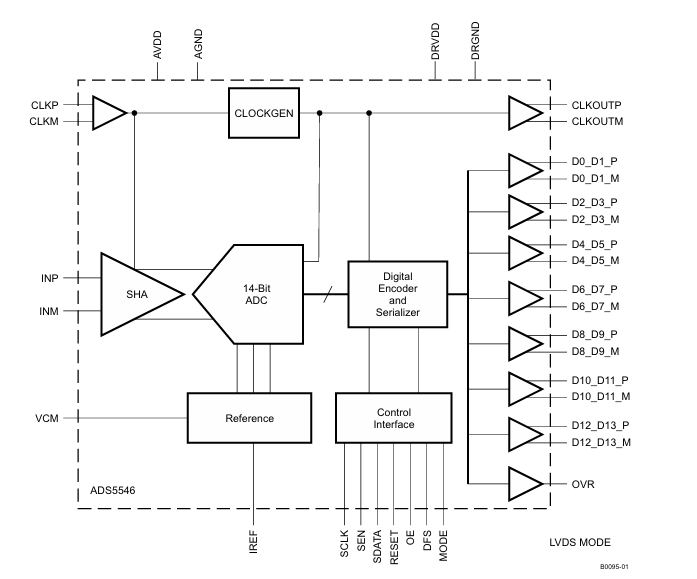

深入剖析ADS5546:高性能14位ADC的卓越之選

深度剖析ADS5521:高性能12位ADC的卓越之選

深入解析ADS8380:高性能18位ADC的卓越之選

深入解析ADS1625/6:高性能18位ADC的卓越之選

解析ADS1625與ADS1626:高性能18位ADC的卓越之選

深入剖析ADS5421:高性能14位ADC的卓越之選

深入解析ADS7852:高性能12位8通道ADC的卓越之選

深入解析ADS850:高性能14位ADC的卓越之選

深入解析ADS850:高性能14位ADC的卓越之選

評論