在AI芯片與高速通信芯片飛速發展的今天,先進封裝技術已成為提升算力與系統性能的關鍵路徑。然而,伴隨芯片集成度的躍升,高密度互連線帶來的信號延遲、功耗上升、波形畸變、信號串擾以及電源噪聲等問題日益凸顯,傳統設計方法在應對這些復雜挑戰時已面臨多重瓶頸。信號完整性(SI)與電源完整性(PI)仿真作為先進封裝設計的核心環節,能夠有效保障系統功能可靠性,維持高密度互連性能,優化電源網絡穩定性,并支撐高密度異構集成的實現,因此對于先進封裝互連系統變得尤為關鍵。在這樣的背景下,法動科技推出的GrityDesigner,作為一款一站式EDA工具,正致力于以智能化手段突破當前先進封裝的設計困局,為工程師提供從芯片到系統的全鏈路性能保障,助力下一代高算力芯片的研發與創新。

Part 01 設計挑戰:從高頻效應到智能化需求

(一)高頻效應與信號完整性挑戰

隨著芯片工作頻率邁入GHz乃至THz量級,高頻效應(如趨膚效應、介質損耗、反射和串擾)對信號完整性的影響呈現指數級增長。傳統基于集總模型的設計方法已無法精確表征高頻電磁場行為,導致信號波形畸變、時序偏差等問題,嚴重制約系統性能提升。

(二)互連線延遲與寄生效應

在先進工藝節點下,互連線延遲已顯著超越門延遲,成為制約芯片性能的關鍵瓶頸。同時,新材料和新結構的引入,以及FinFET/GAAFET等新型器件結構的應用,使得寄生電容、電感和電阻效應更加復雜。互連設計已從傳統的“布線”任務演變為需要精確電磁場建模與協同優化的系統工程。

(三)電源完整性與噪聲控制

在高密度互連系統中,電源網絡的阻抗匹配、電流分布和噪聲控制面臨嚴峻挑戰。電源噪聲(如IR Drop和地彈噪聲)在低電壓、高電流場景下尤為突出,可能導致電壓波動超過容限范圍,嚴重影響的穩定性和性能指標。

(四)低功耗設計壓力

移動設備對續航能力的要求持續提升,而芯片功耗與產品需求之間的差距不斷擴大。在系統級層面,亟需從多個維度實現功耗優化,以滿足日益嚴苛的能效比要求。

(五)三維異構集成的復雜性

三維封裝技術(如2.5D/3D IC)通過芯片堆疊實現更高集成度,但也帶來了復雜的互連結構和信號傳輸路徑等問題。特別是TSV(Through-Silicon Via)和微凸點(Microbump)關鍵互連技術,對設計工具和仿真方法提出了更高的精度和效率要求。

(六)場-路協同仿真的壁壘

電磁場仿真與電路仿真之間的模型不互通,導致設計流程中存在斷點,影響仿真的一致性與效率。亟需建立統一的場-路協同仿真平臺,實現從電磁場到電路行為的無縫銜接,以應對高密度互連系統設計的復雜性。

(七)設計周期與成本壓力

先進封裝設計復雜度呈指數級增長,傳統設計方法耗時長、成本高,難以滿足快速迭代的市場需求。需要在保證性能的同時,通過設計方法學創新和工具鏈優化,顯著縮短設計周期,降低開發成本。

(八)AI與智能化設計需求

隨著AI芯片和高速通信芯片的快速發展,傳統設計方法已難以滿足智能化、自動化設計的需求。亟需將機器學習、深度學習等AI技術引入EDA工具鏈,實現設計空間探索、參數優化和物理實現的智能化,以突破當前的設計瓶頸。

Part 02 GrityDesigner:破局之道

針對先進封裝互連系統中的一系列信號/電源完整性挑戰,GrityDesigner提出了一套系統化、創新性的解決方案,從底層算法到頂層平臺進行全面優化。

(一)高性能全波電磁仿真引擎

采用混合格林函數與自適應算法,顯著降低高密度介質中電磁場計算的復雜度,支持從低頻到高頻的精確仿真。引入高效區域分解方法,支持三維異構封裝(如2.5D/3D IC)的快速仿真,通過并行計算技術實現大規模問題的求解效率。結合多尺度建模技術,實現對TSV、微凸點等關鍵互連結構的高精度電磁特性分析。

(二)AI驅動的建模與優化技術

構建無源電路與幾何參數之間的非線性映射模型,利用深度學習算法實現快速參數提取與優化,顯著提升效率。開發有源器件實時建模框架,結合機器學習方法,在保證精度的同時實現快速仿真,支持動態功耗分析與信號完整性評估。引入AI輔助設計空間探索,通過強化學習算法優化互連拓撲結構與參數配置,縮短設計周期。

(三)信號與電源完整性快速分析

支持多類型模型(如IBIS、SNP、SPICE等)的統一仿真,實現從芯片封裝到PCB的完整鏈路分析。通過快速頻域掃描算法,顯著降低大規模互連網絡的仿真時間,同時保證仿真精度。

(四)信號與電源完整性協同仿真平臺

通過多種仿真方法的深度融合,覆蓋從芯片、封裝到PCB的完整鏈路,系統性地解決阻抗匹配、寄生耦合等高頻問題,確保設計的魯棒性。引入智能噪聲分析與抑制技術,通過優化電源分配網絡(PDN)和去耦電容布局,有效降低IR Drop和地彈噪聲。

(五)三維異構集成設計支持

開發三維互連結構優化引擎,支持TSV、微凸點等關鍵互連技術的快速設計與驗證。支持多芯片異構集成設計,通過智能布局布線優化互連性能,降低延遲與功耗。

(六)場-路協同仿真與設計流程優化

構建統一的場-路協同仿真平臺,實現電磁場仿真與電路仿真的無縫銜接,消除設計流程中的斷點。提供自動化設計流程,通過智能腳本與模板化配置,顯著縮短設計周期,降低開發成本。支持多用戶協同設計,通過云端平臺實現設計數據的實時共享與版本管理。

GrityDesigner的解決方案通過高性能仿真引擎、AI驅動技術、場-路協同仿真優化和三維集成設計支持,全面應對先進封裝互連系統的SIPI挑戰。其核心優勢在于:(1)高精度與高效率的平衡:通過算法創新與AI技術,在保證仿真精度的同時顯著提升效率。(2)系統級設計能力:覆蓋從芯片到系統的完整鏈路,實現信號與電源完整性的協同優化。(3)智能化與自動化:利用AI技術優化設計流程,降低設計復雜度與開發成本。(4)三維異構集成支持:針對2.5D/3D IC等先進封裝技術,提供全面的設計與驗證能力。這一系列創新解決方案為先進封裝互連系統的設計提供了強有力的技術支撐,助力行業突破技術瓶頸,實現更高性能、更低功耗的設計目標。

Part 03 應用場景與市場前

GrityDesigner廣泛應用于移動通信、物聯網、AI芯片、高速通信芯片、高頻高速電子系統等領域,為高密度互連系統提供全面的解決方案。其高效的全波電磁仿真和AI驅動的建模技術,顯著提升了設計效率和精度,滿足了市場對高性能、低功耗芯片的迫切需求。

Part 04 未來展望

隨著AI芯片與高速通信的持續發展,先進封裝技術將面臨更多挑戰。GrityDesigner將繼續致力于技術創新,不斷優化仿真算法和建模技術,為下一代高算力芯片的研發提供堅實的技術基礎,推動行業進步。

Part 05 結語

GrityDesigner不僅僅是一款仿真工具,更是一個整合電磁分析、AI建模、信號完整性、電源完整性、時域仿真與系統驗證的一體化平臺。它致力于在“后摩爾時代”幫助工程師突破先進封裝的設計壁壘,實現從芯片到系統的全鏈路性能保障。作為AI智馭高密度互連未來的一站式平臺,GrityDesigner將繼續引領高速高密度互連技術的發展,為下一代高算力芯片的研發保駕護航。

-

eda

+關注

關注

72文章

3125瀏覽量

183386 -

AI芯片

+關注

關注

17文章

2140瀏覽量

36827 -

先進封裝

+關注

關注

2文章

552瀏覽量

1047

原文標題:破解先進封裝困局! GrityDesigner突破高密度互連難題,磨礪信號及電源完整性之利器

文章出處:【微信號:FaradayDynamics,微信公眾號:法動科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

低軌衛星相控陣天線的核心互連方案:SMP系列射頻連接器在高密度陣列中的關鍵作用

MACOM公司推出高密度銅互連解決方案

MPO分支光纜:高密度光纖布線的核心組件

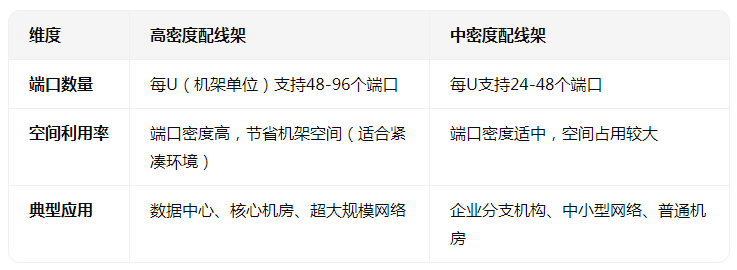

高密度配線架特殊場景與前沿趨勢

高密度光纖布線:未來的數據通信解決方案

6盤位免工具硬盤盒!ICY DOCK高密度存儲,釋放你的5.25寸光驅位

哪種工藝更適合高密度PCB?

高密度互連線路板的應用領域

白城LP-SCADA工業產線高密度數據采集 實時響應無滯后

高密度配線架和中密度的區別

mpo高密度光纖配線架的安裝方法

光纖高密度odf是怎么樣的

二次回流如何破解復雜封裝難題?專用錫膏解密高密度集成難題

法動科技EDA工具GrityDesigner突破高密度互連難題

法動科技EDA工具GrityDesigner突破高密度互連難題

評論