在電子設(shè)計領(lǐng)域,A/D轉(zhuǎn)換器(ADC)是連接模擬世界和數(shù)字世界的關(guān)鍵橋梁。今天,我們要深入探討一款性能卓越的A/D轉(zhuǎn)換器——TI的ADC12L063,它在眾多應(yīng)用場景中都有著出色的表現(xiàn)。

文件下載:adc12l063.pdf

一、產(chǎn)品概述

ADC12L063是一款單芯片CMOS模擬 - 數(shù)字轉(zhuǎn)換器,能夠以最低62兆樣本每秒(MSPS)的速度將模擬輸入信號轉(zhuǎn)換為12位數(shù)字字。它采用差分、流水線架構(gòu),并配備數(shù)字誤差校正和片上采樣保持電路,在提供出色動態(tài)性能的同時,還能最大限度地減小芯片尺寸和功耗。該器件在單3.3V電源下工作,在62 MSPS時僅消耗354 mW的功率(包括參考電流),并且具有掉電功能,可將功耗降低至僅50 mW。

(一)產(chǎn)品特性

- 單電源操作:僅需一個+3.3V電源,簡化了電源設(shè)計。

- 低功耗:正常工作時功耗低,掉電模式下功耗更低,適合對功耗敏感的應(yīng)用。

- 片上參考緩沖器:方便使用,提高了參考電壓的穩(wěn)定性。

(二)應(yīng)用領(lǐng)域

ADC12L063的應(yīng)用非常廣泛,涵蓋了超聲和成像、儀器儀表、蜂窩基站/通信接收器、聲納/雷達、xDSL、無線本地環(huán)路、數(shù)據(jù)采集系統(tǒng)以及DSP前端等領(lǐng)域。

二、關(guān)鍵規(guī)格參數(shù)

(一)靜態(tài)特性

- 分辨率:12位,無丟失碼,能夠提供較高的精度。

- 積分非線性(INL):典型值為±1.0 LSB,最大值為±2.4 LSB,反映了轉(zhuǎn)換器輸出與理想直線的偏差程度。

- 差分非線性(DNL):典型值為±0.5 LSB,衡量了相鄰代碼之間的步長偏差。

- 增益誤差:正誤差最大為 - 0.8 %FS,負誤差最大為 +0.1 ±3 %FS,體現(xiàn)了實際增益與理想增益的差異。

- 偏移誤差:在 $V{IN+} = V{IN-}$ 時,典型值為 +0.1,最大值為 ±0.9 %FS,是輸入為零時輸出與理想值的偏差。

(二)動態(tài)特性

- 全功率帶寬:170 MHz,表明該轉(zhuǎn)換器在較寬的頻率范圍內(nèi)都能保持較好的性能。

- 信噪比(SNR):在 $f{IN} = 1 MHz$ 時,典型值為66 dB;在 $f{IN} = 10 MHz$ 時,最小值為63.3 dB,反映了信號與噪聲的比例關(guān)系。

- 無雜散動態(tài)范圍(SFDR):在 $f{IN} = 1 MHz$ 時,典型值為82 dB;在 $f{IN} = 10 MHz$ 時,最小值為78 dB,衡量了轉(zhuǎn)換器抑制雜散信號的能力。

(三)其他參數(shù)

- 數(shù)據(jù)延遲:6個時鐘周期,這是從采樣到輸出有效數(shù)據(jù)的延遲時間。

- 電源電壓:+3.3V ± 300 mV,在這個電壓范圍內(nèi),轉(zhuǎn)換器能夠穩(wěn)定工作。

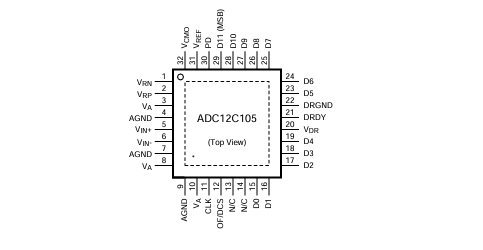

三、引腳說明與等效電路

ADC12L063共有32個引腳,可分為模擬輸入輸出、數(shù)字輸入輸出、模擬電源和數(shù)字電源等幾類。下面我們來詳細了解一下各個引腳的功能。

(一)模擬輸入輸出引腳

- VIN+ 和 VIN-:分別為非反相和反相模擬信號輸入引腳。在1.0V參考電壓下輸入信號電平為1.0 Vp.p。為獲得最佳性能,建議使用差分輸入信號;對于單端操作,可將VIN - 連接到Vcm。

- VREF:參考輸入引腳,應(yīng)通過一個0.1 μF的單片電容旁路到AGND。VREF的標(biāo)稱值為1.0V,范圍應(yīng)在0.8V至1.2V之間。

(二)數(shù)字輸入輸出引腳

- CLK:數(shù)字時鐘輸入引腳,時鐘頻率范圍為1 MHz至70 MHz(典型值),在62 MHz時性能有保證。采樣在時鐘上升沿進行。

- OE:輸出使能引腳,低電平時使能三態(tài)數(shù)據(jù)輸出引腳;高電平時,輸出處于高阻態(tài)。

- PD:掉電輸入引腳,高電平時將轉(zhuǎn)換器置于掉電模式,功耗降低至50 mW;低電平時,轉(zhuǎn)換器處于活動模式。

- D0 - D11:數(shù)字數(shù)據(jù)輸出引腳,組成12位轉(zhuǎn)換結(jié)果。D0是最低有效位(LSB),D11是最高有效位(MSB)。

(三)電源引腳

- VA:正模擬電源引腳,應(yīng)連接到穩(wěn)定的+3.3V電源,并通過0.1 μF單片電容和10 μF電容旁路到AGND。

- AGND:模擬電源的接地引腳。

- VD:正數(shù)字電源引腳,應(yīng)連接到與VA相同的穩(wěn)定+3.3V電源,并通過0.1 μF單片電容和10 μF電容旁路到DGND。

- DGND:數(shù)字電源的接地引腳。

四、電氣特性

(一)靜態(tài)特性

在靜態(tài)特性方面,分辨率、INL、DNL、增益誤差和偏移誤差等參數(shù)都對轉(zhuǎn)換器的精度有著重要影響。例如,INL和DNL反映了轉(zhuǎn)換器輸出的線性度,較小的INL和DNL值意味著更準(zhǔn)確的轉(zhuǎn)換結(jié)果。

(二)動態(tài)特性

動態(tài)特性中的全功率帶寬、SNR、SFDR等參數(shù)則體現(xiàn)了轉(zhuǎn)換器在不同頻率下的性能表現(xiàn)。全功率帶寬決定了轉(zhuǎn)換器能夠處理的信號頻率范圍,而SNR和SFDR則反映了信號的質(zhì)量和抗干擾能力。

(三)電源特性

電源特性方面,模擬電源電流、數(shù)字電源電流和輸出電源電流等參數(shù)影響著整個系統(tǒng)的功耗。通過合理設(shè)計電源電路,可以降低系統(tǒng)的功耗,提高能源效率。

五、應(yīng)用注意事項

(一)工作條件

為了確保ADC12L063的正常工作,建議遵循以下工作條件:

- $3.0 V \leq V_{A} \leq 3.6 V$

- $V{D}=V{A}$

- $1.5 V \leq V{D R} \leq V{D}$

- $1 MHz \leq f_{C L K} \leq 70 MHz$

- $0.8 V \leq V_{REF} \leq 1.2 V$

(二)模擬輸入

模擬輸入信號的質(zhì)量對轉(zhuǎn)換結(jié)果至關(guān)重要。建議使用差分輸入信號,并確保輸入信號的峰 - 峰值電壓等于參考電壓 $V{REF}$,且以 $V{CM}$ 為中心。同時,要注意輸入信號的幅度和相位關(guān)系,避免因信號偏差導(dǎo)致的誤差。

(三)數(shù)字輸入

數(shù)字輸入信號中的時鐘信號(CLK)要穩(wěn)定且抖動小,時鐘頻率應(yīng)在規(guī)定范圍內(nèi)。此外,時鐘信號的占空比也會影響轉(zhuǎn)換器的性能,雖然ADC12L063在35% - 65%的占空比范圍內(nèi)都能保持較好的性能,但仍建議盡量接近50%。

(四)輸出

在驅(qū)動高電容總線時要格外小心,因為輸出驅(qū)動器需要為每次轉(zhuǎn)換充電,過大的電容會導(dǎo)致瞬時數(shù)字電流增大,從而產(chǎn)生片上接地噪聲并耦合到模擬電路中,降低動態(tài)性能。為了減少這種影響,可以在每個數(shù)據(jù)輸出線上串聯(lián)47Ω - 56Ω的電阻,并在ADC輸出和其他電路之間連接緩沖器。

(五)電源供應(yīng)

電源供應(yīng)方面,電源引腳應(yīng)通過10 μF電容和0.1 μF陶瓷芯片電容旁路,且這些電容應(yīng)靠近電源引腳放置。同時,要確保電源噪聲低于100 mVP - P,避免在電源引腳出現(xiàn)過壓情況。

(六)布局和接地

正確的布局和接地對于保證準(zhǔn)確轉(zhuǎn)換至關(guān)重要。應(yīng)將模擬電路和數(shù)字電路分開布局,將ADC12L063置于兩者之間。DR GND引腳不應(yīng)與其他接地引腳靠近連接,以防止輸出電流瞬變產(chǎn)生的噪聲影響轉(zhuǎn)換過程。此外,要盡量縮短時鐘線的長度,并避免時鐘線與其他信號交叉。

六、常見應(yīng)用陷阱及解決方法

(一)輸入電壓超出電源軌

輸入電壓超出電源軌可能導(dǎo)致錯誤或不穩(wěn)定的操作。為避免這種情況,所有輸入電壓不應(yīng)超過電源軌100 mV。對于可能出現(xiàn)過沖或下沖的高速數(shù)字組件,可以在其輸入串聯(lián)50Ω - 100Ω的電阻。

(二)驅(qū)動高電容數(shù)字數(shù)據(jù)總線

驅(qū)動高電容數(shù)字數(shù)據(jù)總線會增加輸出驅(qū)動器的負擔(dān),導(dǎo)致動態(tài)性能下降。解決方法是對數(shù)字數(shù)據(jù)輸出進行緩沖,并在每個數(shù)字輸出端添加47Ω - 56Ω的串聯(lián)電阻,以限制輸出電流。

(三)使用不合適的放大器驅(qū)動模擬輸入

由于輸入電容會隨時鐘相位變化,使用不合適的放大器可能導(dǎo)致性能下降。建議選擇能夠穩(wěn)定驅(qū)動動態(tài)負載的放大器,如LMH6702、LMH6622和LMH6628,并在放大器輸出端添加小串聯(lián)電阻和電容。

(四)參考引腳超出指定范圍

參考引腳的電壓應(yīng)在0.8V - 1.2V范圍內(nèi),超出此范圍可能導(dǎo)致性能下降。因此,要確保參考電壓穩(wěn)定在指定范圍內(nèi)。

(五)時鐘源抖動過大或時鐘線過長

時鐘源抖動過大或時鐘線過長會導(dǎo)致采樣間隔變化,從而增加輸出噪聲并降低SNR和SINAD性能。解決方法是使用無抖動的時鐘源,并通過緩沖器將ADC時鐘與數(shù)字電路隔離,同時盡量縮短時鐘線的長度。

七、總結(jié)

ADC12L063是一款性能卓越、功能強大的A/D轉(zhuǎn)換器,它在低功耗、高速度和高精度等方面都有著出色的表現(xiàn)。然而,在實際應(yīng)用中,我們需要注意各個方面的細節(jié),包括工作條件、輸入輸出信號處理、電源供應(yīng)、布局和接地等,以確保其能夠發(fā)揮出最佳性能。希望通過本文的介紹,能幫助電子工程師們更好地理解和應(yīng)用ADC12L063,在實際項目中取得更好的設(shè)計效果。大家在使用過程中遇到過哪些問題呢?歡迎在評論區(qū)分享交流。

-

MSPS

+關(guān)注

關(guān)注

0文章

574瀏覽量

28985 -

adc

+關(guān)注

關(guān)注

100文章

7527瀏覽量

556358 -

A/D轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

178瀏覽量

11868 -

數(shù)字轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

347瀏覽量

28796

發(fā)布評論請先 登錄

ADC12L063,pdf datasheet (12-Bi

MCP37D11-200 12位200 Msps A/D轉(zhuǎn)換器

DN104-1.25Msps 12位A/D轉(zhuǎn)換器刀盤功耗和尺寸

THS12082低功耗、12位、8 MSPS模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12L063單芯片CMOS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

THS1207低功耗、12位、6 msps模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12C105:高性能12位A/D轉(zhuǎn)換器的深度剖析

深入剖析ADC12C170:高性能12位A/D轉(zhuǎn)換器的技術(shù)解析

ADC12DL065:高性能12位A/D轉(zhuǎn)換器的深度解析

深入剖析ADC12DL080:高性能12位A/D轉(zhuǎn)換器的設(shè)計與應(yīng)用

剖析ADC12L080:12位高速A/D轉(zhuǎn)換器的卓越性能與應(yīng)用指南

深入剖析ADC12QS065:高性能12位A/D轉(zhuǎn)換器的設(shè)計與應(yīng)用

ADC12DL066:高性能12位A/D轉(zhuǎn)換器的深度解析

探索 ADC12D040:雙 12 位、40 MSPS A/D 轉(zhuǎn)換器的卓越性能與應(yīng)用

深入解析ADC12L066:高性能12位A/D轉(zhuǎn)換器的全方位指南

ADC12L063:12位、62 MSPS、低功耗A/D轉(zhuǎn)換器深度解析

ADC12L063:12位、62 MSPS、低功耗A/D轉(zhuǎn)換器深度解析

評論