在電子工程師的設(shè)計(jì)工作中,A/D轉(zhuǎn)換器是至關(guān)重要的組件,它能將模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),為后續(xù)的數(shù)字處理提供基礎(chǔ)。今天,我們就來(lái)詳細(xì)探討TI公司的ADC12C170這款高性能12位、170 MSPS、1.1 GHz帶寬的A/D轉(zhuǎn)換器。

文件下載:adc12c170.pdf

一、ADC12C170概述

ADC12C170采用CMOS工藝制造,能夠以高達(dá)170 MSPS的速率將模擬輸入信號(hào)轉(zhuǎn)換為12位數(shù)字字。它采用差分流水線(xiàn)架構(gòu),結(jié)合數(shù)字誤差校正和片上采樣保持電路,在降低功耗和外部組件數(shù)量的同時(shí),提供了出色的動(dòng)態(tài)性能。其獨(dú)特的采樣保持級(jí)實(shí)現(xiàn)了1.1 GHz的全功率帶寬,這使得它在高頻信號(hào)處理方面表現(xiàn)卓越。

(一)主要特性

- 高帶寬與低功耗:1.1 GHz全功率帶寬,在170 MSPS時(shí)僅消耗715 mW功率,同時(shí)具備內(nèi)部精密1.0V參考,減少了外部參考電路的設(shè)計(jì)。

- 靈活的時(shí)鐘與輸出格式:支持單端或差分時(shí)鐘模式,時(shí)鐘占空比穩(wěn)定器可在寬范圍的輸入時(shí)鐘占空比下保持性能。輸出數(shù)據(jù)格式可選擇偏移二進(jìn)制或2的補(bǔ)碼,并且與ADC14155、ADC11C125、ADC11C170引腳兼容,方便工程師進(jìn)行設(shè)計(jì)升級(jí)和替換。

- 多種工作模式:具備掉電和睡眠模式,掉電模式下功耗可降至5 mW,睡眠模式下功耗為50 mW,且都能實(shí)現(xiàn)快速喚醒,滿(mǎn)足不同應(yīng)用場(chǎng)景下的節(jié)能需求。

(二)應(yīng)用領(lǐng)域

ADC12C170適用于多種應(yīng)用場(chǎng)景,如高IF采樣接收器、無(wú)線(xiàn)基站接收器、功率放大器線(xiàn)性化、多載波多模式接收器、測(cè)試測(cè)量設(shè)備、通信儀器和雷達(dá)系統(tǒng)等。這些應(yīng)用對(duì)信號(hào)處理的速度和精度要求較高,ADC12C170的高性能特性能夠很好地滿(mǎn)足這些需求。

二、關(guān)鍵規(guī)格參數(shù)

(一)靜態(tài)參數(shù)

- 分辨率:無(wú)缺失碼的分辨率為12位,確保了轉(zhuǎn)換的準(zhǔn)確性。

- 線(xiàn)性度:積分非線(xiàn)性(INL)在全量程輸入時(shí)最大為±0.85 LSB,差分非線(xiàn)性(DNL)最大為±0.54 LSB,保證了轉(zhuǎn)換的線(xiàn)性度。

- 增益誤差與偏移誤差:正增益誤差(PGE)和負(fù)增益誤差(NGE)在規(guī)定范圍內(nèi),偏移誤差(VOFF)也較小,并且增益誤差和偏移誤差的溫度系數(shù)都很低,確保了在不同溫度環(huán)境下的穩(wěn)定性。

(二)動(dòng)態(tài)參數(shù)

- 信噪比(SNR):在$f_{IN}=70 MHz$時(shí),典型值為67.2 dBFS,能夠有效抑制噪聲,提高信號(hào)質(zhì)量。

- 無(wú)雜散動(dòng)態(tài)范圍(SFDR):在$f_{IN}=70 MHz$時(shí),典型值為85.4 dBFS,減少了雜散信號(hào)的干擾。

- 有效位數(shù)(ENOB):在$f_{IN}=70 MHz$時(shí),典型值為10.8位,反映了轉(zhuǎn)換器的實(shí)際性能。

三、引腳說(shuō)明與等效電路

(一)模擬輸入輸出引腳

- VIN+和VIN -:差分模擬輸入引腳,差分滿(mǎn)量程輸入信號(hào)電平為參考電壓的兩倍,每個(gè)輸入引腳信號(hào)以共模電壓VCM為中心。

- VRP、VRN和VRM:這些引腳用于參考電壓相關(guān)操作,VRP和VRN應(yīng)通過(guò)低ESL的0.1 μF電容旁路到AGND,VRM可提供差分模擬輸入的共模電壓VCM。

- VREF:可作為+1.0V內(nèi)部參考電壓輸出或外部參考電壓輸入,使用內(nèi)部參考時(shí)需用0.1 μF低ESL電容去耦。

(二)數(shù)字輸入輸出引腳

- DO - D11:構(gòu)成12位轉(zhuǎn)換結(jié)果的數(shù)字?jǐn)?shù)據(jù)輸出引腳,輸出電平與CMOS兼容。

- OVR:過(guò)范圍指示輸出,當(dāng)輸入幅度超過(guò)12位轉(zhuǎn)換范圍時(shí)置高。

- DRDY:數(shù)據(jù)就緒選通信號(hào),用于時(shí)鐘輸出數(shù)據(jù),其上升沿應(yīng)用于捕獲輸出數(shù)據(jù)。

(三)電源引腳

- VA:正模擬電源引腳,應(yīng)連接到安靜的+3.3V源,并通過(guò)0.01 uF和0.1 uF電容旁路到AGND。

- VD:正數(shù)字電源引腳,連接到+3.3V源并旁路到DGND。

- VDR:輸出驅(qū)動(dòng)器的正電源引腳,連接到+1.8V源并旁路到DRGND。

四、工作原理與功能描述

(一)轉(zhuǎn)換過(guò)程

ADC12C170在雙+3.3V和+1.8V電源下工作,通過(guò)差分流水線(xiàn)架構(gòu)和誤差校正電路將差分模擬輸入信號(hào)數(shù)字化為12位。模擬輸入在時(shí)鐘下降沿采集,經(jīng)過(guò)7個(gè)時(shí)鐘周期的流水線(xiàn)延遲后,數(shù)字?jǐn)?shù)據(jù)在DRDY信號(hào)下降沿輸出。

(二)時(shí)鐘與數(shù)據(jù)格式選擇

CLK_SEL/DF引腳允許用戶(hù)選擇單端或差分時(shí)鐘輸入以及偏移二進(jìn)制或2的補(bǔ)碼輸出數(shù)據(jù)格式。時(shí)鐘頻率范圍為5 MHz至170 MHz,典型性能在170 MSPS時(shí)完全指定。

(三)電源管理

通過(guò)PD/Sleep引腳可選擇掉電和睡眠模式。掉電模式下,除電壓參考電路外的所有電路均被禁用,功耗降至5 mW;睡眠模式下,除電壓參考電路和其伴隨的片上緩沖器外的部分電路被禁用,功耗降至50 mW。正常操作時(shí),PD/Sleep引腳應(yīng)連接到模擬地(AGND)。

五、設(shè)計(jì)注意事項(xiàng)

(一)模擬輸入設(shè)計(jì)

- 信號(hào)輸入:差分模擬輸入引腳應(yīng)驅(qū)動(dòng)源阻抗小于100Ω的信號(hào),匹配差分輸入的源阻抗可改善偶次諧波性能。輸入信號(hào)的相對(duì)相位誤差會(huì)影響轉(zhuǎn)換性能,對(duì)于單頻正弦波,可用公式$E_{FS}=4096\left(1 - sin \left(90^{\circ}+ dev\right)\right)$描述全量程誤差。

- 驅(qū)動(dòng)電路:ADC12C170的模擬輸入有內(nèi)部采樣保持電路,時(shí)鐘高電平時(shí)為采樣階段,低電平時(shí)為保持階段。為減少采樣保持充電毛刺的影響,可使用外部電阻和電容網(wǎng)絡(luò)隔離毛刺并過(guò)濾寬帶噪聲。

- 共模電壓:輸入共模電壓VCM應(yīng)在1.4V至1.6V范圍內(nèi),推薦使用VRM(引腳45)作為輸入共模電壓。

(二)參考引腳設(shè)計(jì)

ADC12C170可使用內(nèi)部1.0V參考或外部0.9V至1.1V參考。VREF引腳應(yīng)始終通過(guò)0.1 μF電容旁路到地,較低的參考電壓會(huì)降低信噪比,過(guò)高的參考電壓可能會(huì)降低總諧波失真。所有與參考電壓和模擬輸入信號(hào)相關(guān)的接地應(yīng)在單點(diǎn)安靜處連接到接地平面,以減少接地路徑中的噪聲電流影響。

(三)時(shí)鐘輸入設(shè)計(jì)

- 時(shí)鐘模式:CLK_SEL/DF引腳可配置為單端或差分時(shí)鐘模式,差分時(shí)鐘模式下兩個(gè)時(shí)鐘信號(hào)應(yīng)相位相反且幅度相同。

- 時(shí)鐘性能:時(shí)鐘信號(hào)的占空比會(huì)影響A/D轉(zhuǎn)換器的性能,ADC12C170的占空比穩(wěn)定器可在30%至70%的時(shí)鐘占空比范圍內(nèi)保持性能。為獲得最佳動(dòng)態(tài)性能,時(shí)鐘源應(yīng)具有尖銳的過(guò)渡區(qū)域且無(wú)抖動(dòng),可使用緩沖器隔離時(shí)鐘與數(shù)字電路。

(四)數(shù)字輸出設(shè)計(jì)

數(shù)字輸出為1.8V CMOS信號(hào),包括D0 - D11、DRDY、OVR和OGND。數(shù)據(jù)應(yīng)在DRDY信號(hào)上升沿捕獲和鎖存。驅(qū)動(dòng)高電容總線(xiàn)時(shí)需注意,過(guò)大的輸出電容會(huì)導(dǎo)致動(dòng)態(tài)性能下降,可通過(guò)適當(dāng)?shù)呐月贰⑾拗戚敵鲭娙莺妥⒁饨拥仄矫鎭?lái)減少問(wèn)題。為減少輸出開(kāi)關(guān)噪聲,可使用可編程邏輯器件(PLD)進(jìn)行電平轉(zhuǎn)換,并在數(shù)字輸出端插入約22Ω的串聯(lián)電阻。

(五)電源與布局設(shè)計(jì)

- 電源:電源引腳應(yīng)通過(guò)0.1 μF和0.01 μF陶瓷芯片電容旁路,模擬電源引腳的噪聲應(yīng)保持在100 mVP - P以下。VDR引腳可在1.6V至2.0V范圍內(nèi)供電,降低電源電壓會(huì)增加tOD,可能需要電平轉(zhuǎn)換器與非1.8V CMOS設(shè)備接口。

- 布局與接地:正確的接地和信號(hào)布線(xiàn)對(duì)于確保準(zhǔn)確轉(zhuǎn)換至關(guān)重要。應(yīng)將模擬和數(shù)字區(qū)域分開(kāi),ADC12C170置于兩者之間。避免模擬和數(shù)字線(xiàn)路交叉,尤其是時(shí)鐘線(xiàn)路應(yīng)盡可能短且與其他線(xiàn)路隔離。電感和變壓器的布局應(yīng)避免磁耦合,模擬輸入應(yīng)與噪聲信號(hào)跡線(xiàn)隔離。

六、總結(jié)

ADC12C170是一款性能卓越的12位A/D轉(zhuǎn)換器,具有高帶寬、低功耗、靈活的時(shí)鐘和輸出格式等優(yōu)點(diǎn)。在實(shí)際設(shè)計(jì)中,如果能充分理解其工作原理和特性,并注意各個(gè)引腳的使用和布局布線(xiàn)等方面的問(wèn)題,將有助于發(fā)揮其最佳性能,滿(mǎn)足各種應(yīng)用場(chǎng)景的需求。希望通過(guò)本文的介紹,能為電子工程師在使用ADC12C170進(jìn)行設(shè)計(jì)時(shí)提供有益的參考。大家在實(shí)際應(yīng)用中遇到過(guò)哪些問(wèn)題呢?歡迎在評(píng)論區(qū)分享交流。

-

無(wú)線(xiàn)基站

+關(guān)注

關(guān)注

0文章

69瀏覽量

12794 -

A/D轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

185瀏覽量

11902 -

模擬信號(hào)

+關(guān)注

關(guān)注

8文章

1234瀏覽量

54744 -

高頻信號(hào)處理

+關(guān)注

關(guān)注

1文章

6瀏覽量

759

發(fā)布評(píng)論請(qǐng)先 登錄

ADC12C170,pdf datasheet (12-Bi

ADS5525高性能12位、170 MSPS A/D轉(zhuǎn)換器數(shù)據(jù)表

ADC12C170高性能CMOS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

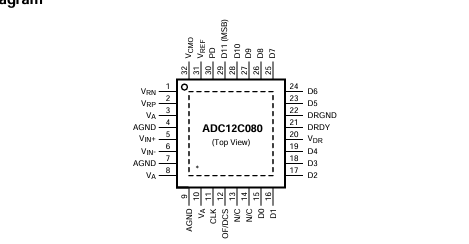

深入剖析ADC12C080:高性能12位A/D轉(zhuǎn)換器的技術(shù)指南

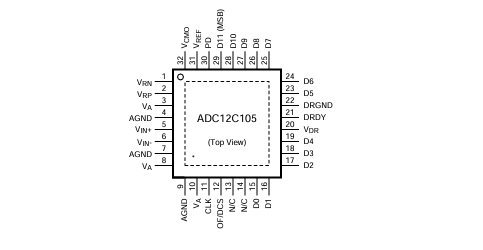

ADC12C105:高性能12位A/D轉(zhuǎn)換器的深度剖析

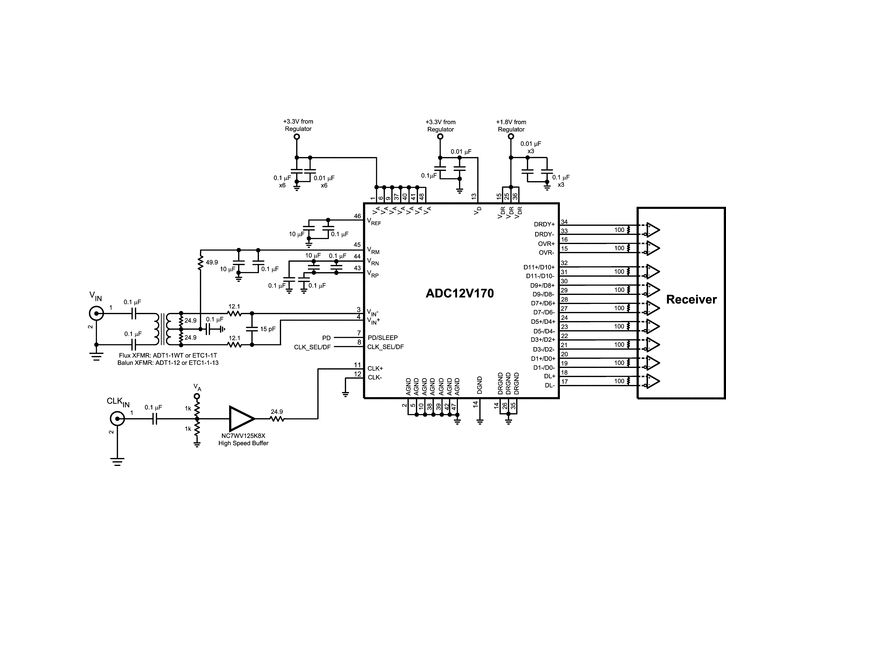

深入剖析ADC12V170:高性能A/D轉(zhuǎn)換器的卓越之選

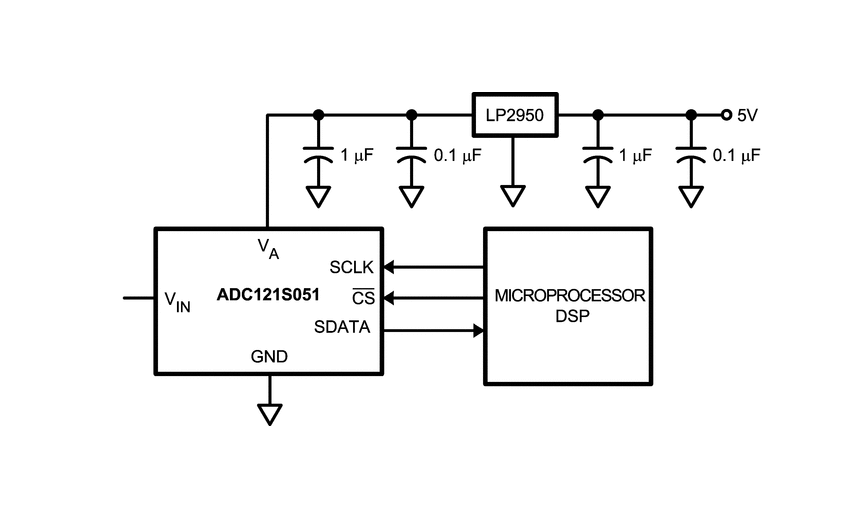

深入剖析ADC121S051:高性能單通道12位A/D轉(zhuǎn)換器的設(shè)計(jì)與應(yīng)用

深入剖析ADC12DL080:高性能12位A/D轉(zhuǎn)換器的設(shè)計(jì)與應(yīng)用

深入剖析ADC121S625:高性能12位A/D轉(zhuǎn)換器的卓越之選

深入剖析ADC12QS065:高性能12位A/D轉(zhuǎn)換器的設(shè)計(jì)與應(yīng)用

ADC12DL066:高性能12位A/D轉(zhuǎn)換器的深度解析

深入解析ADC12L066:高性能12位A/D轉(zhuǎn)換器的全方位指南

深入剖析ADC12C170:高性能12位A/D轉(zhuǎn)換器的技術(shù)解析

深入剖析ADC12C170:高性能12位A/D轉(zhuǎn)換器的技術(shù)解析

評(píng)論