在當今的電子設計領域,高精度、高速的模擬 - 數字轉換器(ADC)是許多應用的核心組件。德州儀器(Texas Instruments)的ADS8382就是這樣一款出色的ADC,它具有18位分辨率、600-kHz采樣率,適用于醫療儀器、光網絡、高精度數據采集系統等多種應用場景。本文將對ADS8382進行詳細的技術剖析,幫助電子工程師更好地了解和使用這款芯片。

文件下載:ads8382.pdf

一、ADS8382概述

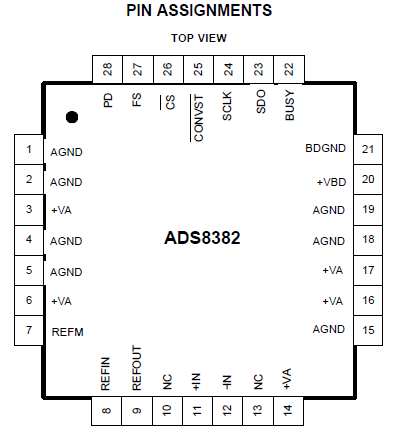

ADS8382是一款高性能的18位、600-kHz A/D轉換器,具有全差分、偽雙極性輸入。它采用電容式逐次逼近寄存器(SAR)架構,自帶采樣和保持功能。芯片集成了高速CMOS串行接口,時鐘速度最高可達40 MHz,還配備了片上參考緩沖器和4.096-V參考電壓源。此外,它支持偽雙極性輸入,輸入范圍可達±4.2 V,并且自帶轉換時鐘,具有零延遲的特點。

(一)特性亮點

- 高精度:典型積分非線性(INL)為±1.25 LSB,最大為±3 LSB;無失碼分辨率達到18位,確保了在寬溫度范圍內的高精度轉換。

- 高動態性能:在輸入頻率$f_{i}=1 kHz$時,信納比(SINAD)達到96 dB,無雜散動態范圍(SFDR)達到120 dB,能夠有效抑制噪聲和雜散信號。

- 高速接口:支持高達40 MHz的高速串行接口,方便與微控制器或其他數字設備進行通信。

- 低功耗:在600 kHz采樣率下功耗僅為115 mW,在休眠模式下為15 mW,在掉電模式下僅為10 μW,適合低功耗應用。

- 寬輸入范圍:偽雙極性輸入范圍可達±4.2 V,滿足多種信號采集需求。

(二)應用領域

ADS8382的高性能特性使其在多個領域得到廣泛應用,包括醫療儀器(如心電圖機、超聲設備等)、光網絡(如光纖通信中的信號采集)、高精度數據采集系統、磁力計等。

二、技術規格詳解

(一)絕對最大額定值

在使用ADS8382時,需要注意其絕對最大額定值,以確保芯片的安全和穩定運行。例如,輸入電壓范圍為 - 0.3 V至 + VA + 0.3 V,工作溫度范圍為 - 40°C至85°C,存儲溫度范圍為 - 65°C至150°C。超出這些范圍可能會導致芯片損壞或性能下降。

(二)電氣特性

-

模擬輸入特性

- 滿量程輸入電壓:輸入電壓范圍為 - Vref至Vref,絕對輸入電壓范圍為 - 0.2 V至Vref + 0.2 V。

- 輸入共模范圍:為(Vref/2) - 0.2 V至(Vref/2) + 0.2 V,確保了在不同共模電壓下的穩定性能。

- 采樣電容:測量值為40 pF,輸入泄漏電流典型值為1 nA。

-

系統性能特性

- 分辨率:無失碼分辨率為18位,確保了高精度的轉換結果。

- INL和DNL:積分線性度(INL)和差分線性度(DNL)是衡量ADC線性度的重要指標。在觀察到安靜區時,INL典型值為±1.25 LSB,最大為±3 LSB;DNL典型值為±0.6 LSB,最大為±1.5 LSB。

- 偏移誤差和增益誤差:偏移誤差(Eo)典型值為±0.25 mV,增益誤差(EG)典型值為±0.075% FS。

- 共模抑制比(CMRR):在直流時達到80 dB,有效抑制了共模干擾。

-

動態特性

- 轉換時間和吞吐量:轉換時間典型值為1.16 μs,吞吐量可達600 kHz,滿足高速數據采集的需求。

- SINAD和SFDR:在不同輸入頻率下,SINAD和SFDR表現出色,確保了高動態性能。

(三)數字輸入/輸出特性

ADS8382的數字接口采用CMOS邏輯,支持高速串行通信。高電平輸入電壓(VIH)為 + VBD - 1 V至 + VBD + 0.3 V,低電平輸入電壓(VIL)為 - 0.3 V至0.8 V。數據以2的補碼形式輸出,方便與數字系統進行接口。

(四)電源要求

芯片的模擬電源電壓(+VA)范圍為4.75 V至5.25 V,數字電源電壓(+VBD)范圍為2.7 V至5.25 V。在600 kHz采樣率下,模擬電源電流典型值為22 mA,數字電源電流典型值為1 mA(+VBD = 5 V,負載電容為10 pF時)。

三、工作原理

(一)SAR架構

ADS8382采用逐次逼近寄存器(SAR)架構,基于電荷再分配原理工作。在采樣階段,輸入信號被采樣到內部電容陣列上;在轉換階段,通過逐次比較的方式將模擬信號轉換為數字信號。這種架構具有轉換速度快、功耗低的優點。

(二)參考電壓

芯片內置了4.096-V的參考電壓源,但也支持外部參考電壓輸入。當使用內部參考時,需要在REFIN和REFM引腳之間連接0.1-μF旁路電容和1-μF存儲電容,以確保參考電壓的穩定性。

(三)模擬輸入

模擬輸入通過 + IN和 - IN引腳接入,輸入范圍為 - 0.2 V至Vref + 0.2 V。在采樣時間內,輸入信號需要能夠為內部40 pF的采樣電容充電至18位的穩定水平。在保持模式下,輸入電阻大于1 GΩ。

(四)數字接口

ADS8382的數字接口支持SPI協議,方便與微控制器或其他數字設備進行通信。在讀取數據時,需要注意避免在指定的安靜區進行操作,以防止性能下降。

四、時序要求和控制

(一)轉換和采樣控制

轉換和采樣通過CONVST和CS引腳進行控制。當CONVST_QUAL引腳出現下降沿時,芯片從采樣階段進入轉換階段;當CONVST為高電平且CS為低電平時,芯片開始采樣。

(二)數據讀取操作

數據讀取可以在轉換或采樣期間進行,但需要注意避免在BUSY信號下降沿附近開始讀取操作,以防止數據丟失。在SPI接口模式下,數據通過SCLK時鐘信號進行移位輸出。

(三)安靜區要求

為了避免性能下降,需要在轉換和采樣過程中觀察三個安靜區($t{quiet1}$、$t{quiet2}$和$t_{quiet3}$),在這些區域內,接口控制信號應保持穩定。

五、電源管理

(一)全功率下降模式

當PD引腳為高電平時,芯片進入全功率下降模式,功耗降至2 μA。在恢復正常工作時,需要注意前兩次轉換結果可能不準確,因為芯片需要加載校準值。

(二)休眠模式

如果在轉換結束時CONVST_QUAL為低電平,芯片將自動進入休眠模式,功耗為3 mA。在休眠模式下,芯片可以通過采樣開始命令恢復正常工作。

六、布局考慮

(一)模擬和數字信號隔離

由于ADS8382常與數字邏輯電路一起使用,因此需要注意模擬信號和數字信號的隔離,以減少數字噪聲對模擬信號的干擾。

(二)電源和參考電壓穩定性

電源和參考電壓的穩定性對ADC的性能至關重要。需要使用適當的旁路電容和儲能電容,確保電源和參考電壓的穩定。

(三)接地設計

AGND和BDGND引腳應連接到干凈的接地平面,以減少接地噪聲的影響。

七、應用示例

(一)SPI模式下的600-KSPS吞吐量

通過合理設計SPI接口的時序,可以實現600-KSPS的吞吐量。具體的時序圖可以參考文檔中的示例。

(二)使用FS信號的串行接口

也可以使用幀同步信號FS來實現600-KSPS的吞吐量,這種方式可以根據具體應用需求進行選擇。

八、總結

ADS8382是一款高性能、低功耗的18位、600-kHz全差分偽雙極性輸入ADC,具有高精度、高動態性能、高速接口等優點。在使用時,需要注意其技術規格、時序要求、電源管理和布局設計等方面,以確保芯片的最佳性能。希望本文對電子工程師在設計中使用ADS8382有所幫助。你在實際應用中是否遇到過類似ADC的使用問題呢?歡迎在評論區分享你的經驗和見解。

-

adc

+關注

關注

100文章

7511瀏覽量

555919 -

模數轉換器

+關注

關注

26文章

4013瀏覽量

130100 -

數字轉換器

+關注

關注

0文章

347瀏覽量

28761 -

逐次逼近寄存器

+關注

關注

0文章

38瀏覽量

8264

發布評論請先 登錄

ADS8382 pdf datasheet

18位1.25MSPS偽雙極全差分輸入微功耗模數轉換器ADS884的詳細概述

LTC2337-18:18位,500ksps,±10.24V真雙極全差分輸入ADC,帶100dB SNR數據表

LTC2336-18:18位,250ksps,±10.24V真雙極全差分輸入ADC,帶100dB SNR數據表

LTC2338-18:18位,1Msps,±10.24V真雙極全差分輸入ADC,帶100dB SNR數據表

LTC2326-18:18位、250ksps、±10.24V真雙極、偽差分輸入ADC,帶95dB SNR數據表

LTC2327-18:18位、500ksps、±10.24V真雙極、偽差分輸入ADC,帶95dB SNR數據表

LTC2328-18:18位、1Msps、±10.24V真雙極、偽差分輸入ADC,帶95dB SNR數據表

ADS921x具有全差分ADC輸入驅動器的雙路同步采樣18位10MSPS SAR ADC數據表

深入剖析ADS8382:18位、600-kHz全差分偽雙極性輸入ADC

深入剖析ADS8382:18位、600-kHz全差分偽雙極性輸入ADC

評論