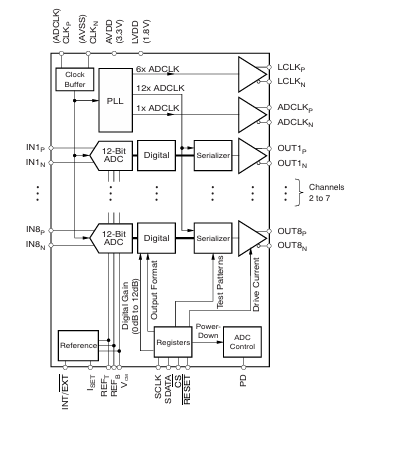

在當今高速發展的電子技術領域,模擬到數字的轉換是許多系統中的關鍵環節。德州儀器(TI)的ADS5277作為一款8通道、10位、65MSPS的模數轉換器(ADC),憑借其出色的性能和豐富的特性,在便攜式超聲系統、磁帶驅動器和測試設備等應用中表現卓越。本文將深入剖析ADS5277的特性、電氣參數、工作原理以及使用中的注意事項,為電子工程師在設計中提供全面的參考。

文件下載:ads5277.pdf

特性亮點

集成PLL與數據序列化

ADS5277集成了鎖相環(PLL),將輸入的ADC采樣時鐘乘以12倍。這個高頻時鐘用于數據序列化和傳輸過程。每個內部ADC的10位輸出被序列化為12位字,其中2個最低有效位(LSBs)為零,其余10位對應ADC的輸出。這種格式確保了接口與家族中的12位部件兼容。除了八個數據輸出外,還傳輸位時鐘和字時鐘,位時鐘速度是采樣時鐘的6倍,字時鐘速度與采樣時鐘相同。

高性能與低功耗

ADS5277具有65MSPS的最大采樣率和10位分辨率,無缺失碼。內部參考模式下總功耗為911mW,外部參考模式下為845mW,采用CMOS技術,同時具備采樣保持功能。在5MHz中頻下,信噪比(SNR)達到61.7dBFS,數字/模擬電源為3.3V,采用序列化LVDS輸出,有效減少了接口線數量和封裝尺寸。

靈活的參考選擇

該ADC提供內部參考,也可選擇外部參考。內部參考模式可實現最佳性能,同時支持集成幀和位模式,LVDS時鐘輸出電流可選擇加倍,有四種LVDS電流模式,引腳和格式與家族其他產品兼容。

電氣參數

絕對最大額定值

了解ADS5277的絕對最大額定值對于確保設備的安全運行至關重要。模擬電源電壓范圍(AVDD)為 -0.3V至 +3.8V,輸出驅動器電源電壓范圍(LVDD)同樣為 -0.3V至 +3.8V,各引腳的電壓范圍也有明確限制。工作自由空氣溫度范圍為 -40°C至 +85°C,結溫為 +105°C,存儲溫度范圍為 -65°C至 +150°C。

推薦工作條件

在推薦工作條件下,模擬電源電壓(AVDD)和輸出驅動器電源電壓(LVDD)為3.0V至3.6V,外部參考模式下的參考電壓也有相應的范圍要求。ADCLK輸入采樣率為20MSPS至65MSPS,時鐘占空比為45%至55%。

直流精度與功率要求

直流精度方面,ADS5277無缺失碼,差分非線性(DNL)和積分非線性(INL)在5MHz輸入頻率下分別為 -0.5LSB至 +0.5LSB和 -1.0LSB至 +1.0LSB。偏移誤差在 -0.75%FS至 +0.75%FS之間。功率要求方面,內部參考模式下模擬部分(AVDD)功耗為718mW,輸出驅動器(LVDD)為193mW,總功耗為911mW;外部參考模式下總功耗為845mW。

交流特性

交流特性中,無雜散動態范圍(SFDR)在不同輸入頻率下表現出色,如在5MHz輸入頻率下達到85dBc。二階諧波失真(HD2)和三階諧波失真(HD3)也有良好的指標,信噪比(SNR)在5MHz輸入頻率下為61.7dBFS。

工作原理

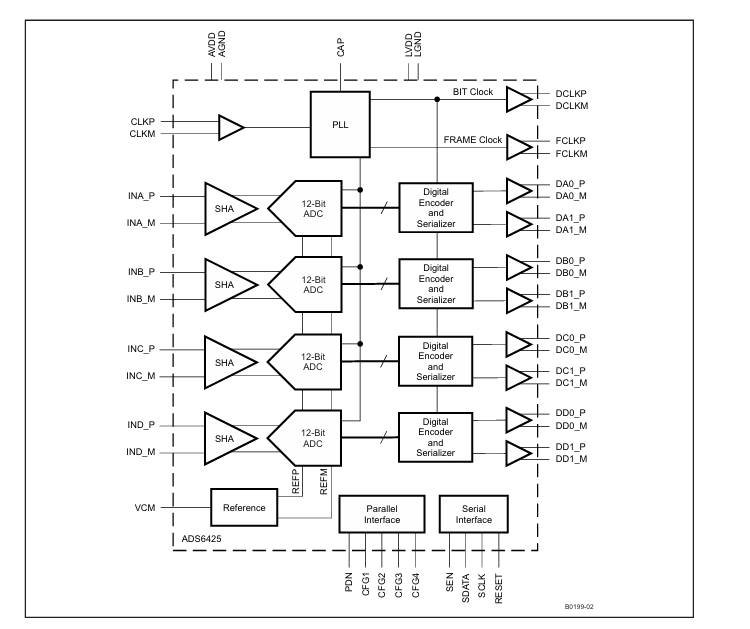

整體架構

ADS5277由高性能采樣保持電路和10位ADC組成。輸入的采樣時鐘通過精心匹配的時鐘緩沖樹為八個通道生成采樣時鐘,PLL將輸入時鐘乘以12倍,為序列化器提供所需的高頻時鐘。ADC采用流水線轉換器架構,確保了良好的差分線性度和無缺失碼。

數據序列化與傳輸

ADC的輸出經過序列化器,將10位數據和2個填充位序列化為12位字,并以LSB優先的方式傳輸。序列化器還生成1倍和6倍時鐘,與數據保持完美同步。LVDS緩沖器用于外部數據傳輸,減少了輸出引腳數量,降低了功耗和數字噪聲對模擬電路的影響。

參考電路設計

參考電路設計方面,內部參考模式下,REF_T和REF_B的標稱值分別為1.95V和0.95V,VCM為1.45V。外部參考模式下,需確保外部參考電壓的共模電壓與VCM匹配在50mV以內。所有內部偏置電流通過I_SET引腳的外部電阻設置,推薦使用56.2kΩ電阻。

時鐘與LVDS緩沖器

八個通道使用單個ADCLK輸入,時鐘樹網絡確保各通道的孔徑延遲和抖動一致。PLL生成50%占空比的時鐘和12倍時鐘,用于ADC采樣和數據序列化。LVDS緩沖器有四個電流設置,輸出阻抗高,必要時可使用100Ω終端電阻減少反射影響。

使用注意事項

噪聲耦合與電源隔離

高速混合信號容易受到噪聲耦合的影響,ADS5277通過明確劃分模擬和數字域,使用多個引腳驅動電源和地,以及在板上使用地平面和大去耦電容,減少了數字到模擬部分的噪聲耦合。建議使用單獨的電源驅動AVDD和LVDD,以及單獨的地平面。

電源管理與復位

ADS5277具有電源管理功能,PD引腳可使設備進入電源關斷模式,單個通道也可通過編程寄存器選擇性地關斷電源。時鐘停止監測電路可在ADCLK停止時降低功耗。在電源穩定后,需要給設備一個有效的RESET脈沖,確保內部寄存器復位到默認值。

PCB布局

ADS5277采用PowerPAD熱增強封裝,PCB布局時需參考相關技術文檔,確保熱效率的優化。同時,對于高速LVDS輸出的接口設計,可參考TI的應用報告。

總結

ADS5277作為一款高性能的8通道ADC,在采樣率、分辨率、功耗和接口等方面都具有出色的表現。其豐富的特性和靈活的配置使其適用于多種應用場景。電子工程師在設計中應充分了解其特性和電氣參數,注意噪聲耦合、電源管理和PCB布局等問題,以確保系統的穩定運行和性能優化。希望本文能為工程師在使用ADS5277進行設計時提供有價值的參考。

你在使用ADS5277的過程中遇到過哪些問題?或者你對其他類似的ADC產品有什么疑問?歡迎在評論區留言討論。

-

驅動器

+關注

關注

54文章

9093瀏覽量

155885 -

電源電壓

+關注

關注

3文章

1260瀏覽量

26425 -

模數轉換器

+關注

關注

26文章

4020瀏覽量

130163 -

輸出電流

+關注

關注

0文章

821瀏覽量

18028

發布評論請先 登錄

ADS5277高性能、CMOS、65MSPS、8通道模數轉換器(ADC)數據表

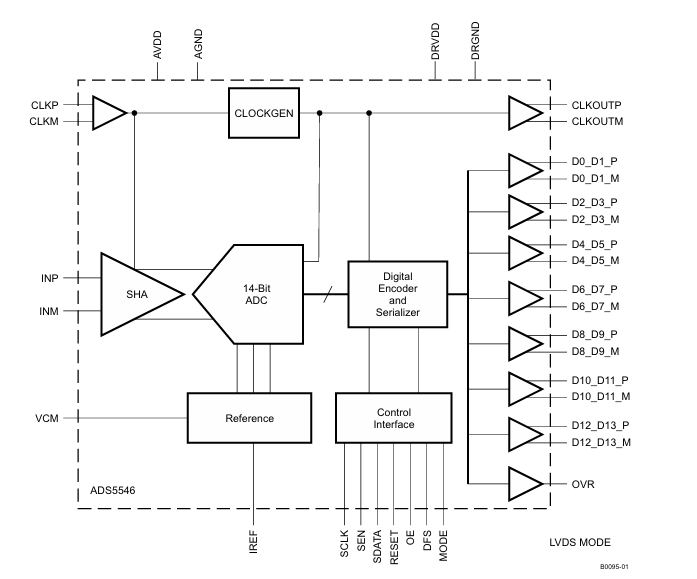

深入剖析ADS5546:高性能14位ADC的卓越之選

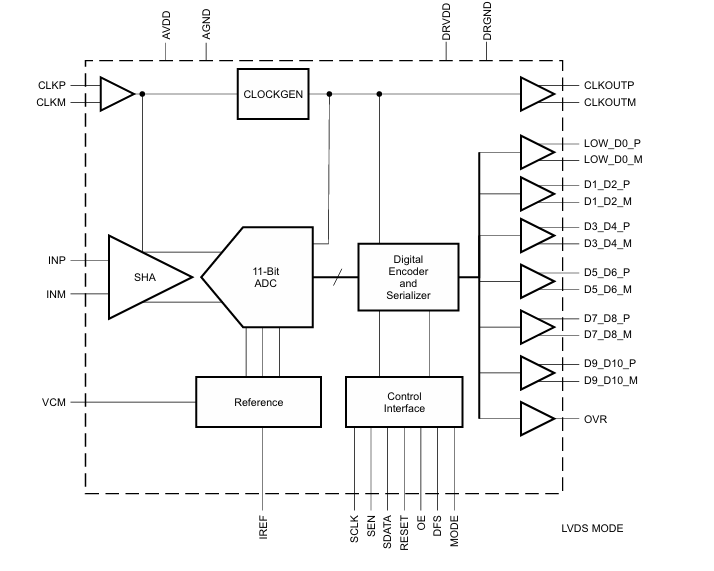

深入解析ADS8364:高性能6通道同步采樣ADC的卓越之選

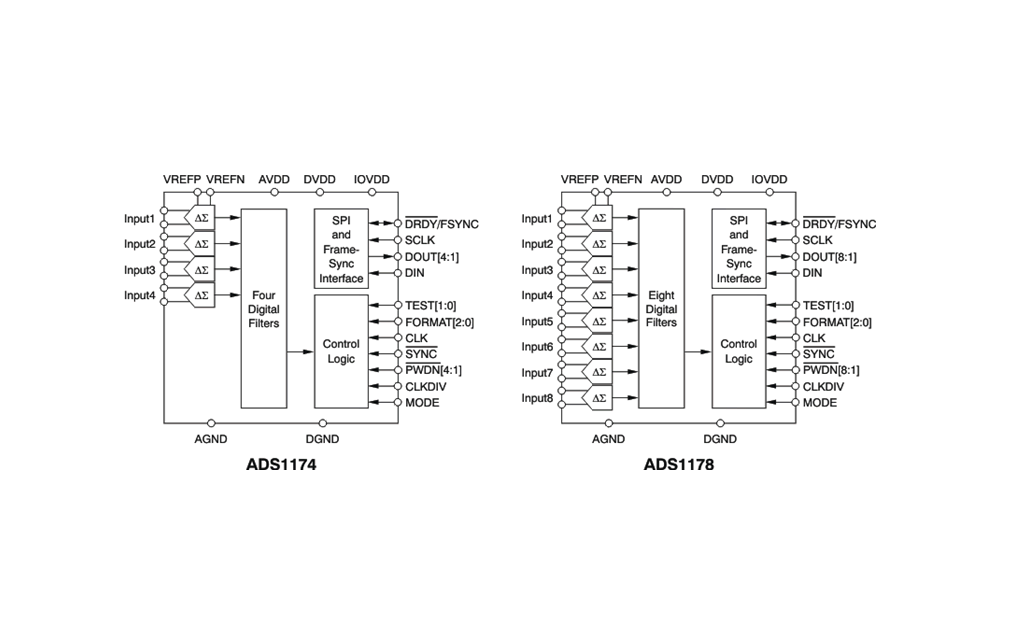

深入解析ADS7852:高性能12位8通道ADC的卓越之選

深入解析ADS5277:高性能8通道ADC的卓越之選

深入解析ADS5277:高性能8通道ADC的卓越之選

評論