在電子工程師的設計領域中,A/D轉換器一直是至關重要的組件。今天,我們將深入探討TI公司的ADC14L020這款14位、20 MSPS的A/D轉換器,為大家詳細解析它的特性、參數、應用以及設計過程中需要注意的關鍵要點。

文件下載:adc14l020.pdf

一、產品概述

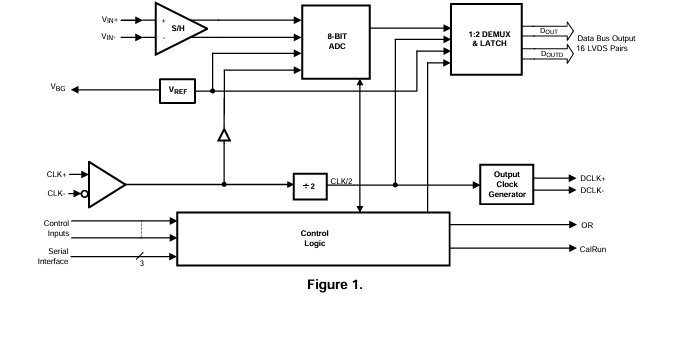

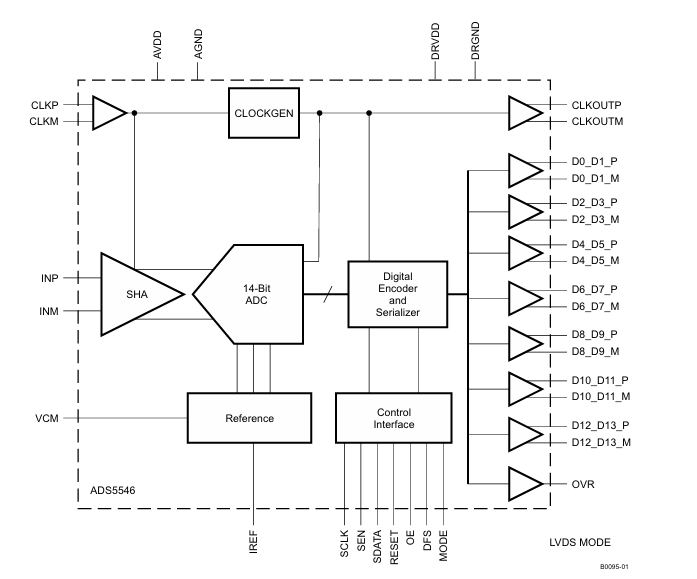

ADC14L020是一款低功耗的單芯片CMOS模擬 - 數字轉換器,能夠以每秒20兆采樣 (MSPS) 的速率將模擬輸入信號轉換為14位數字字。它采用了差分流水線架構,并配備數字誤差校正和片上采樣保持電路,在降低功耗的同時,還能提供出色的動態性能和150 MHz的全功率帶寬。這款轉換器僅需單一的 +3.3V電源供電,在奈奎斯特頻率下可實現12.0的有效位數,在20 MSPS的采樣率下功耗僅為150 mW,并且具備掉電模式,可將功耗降低至15 mW。

二、產品特性

(一)電源與內部結構

- 單一電源供電:僅需 +3.3V電源,簡化了電源設計。

- 內部采樣保持:片上集成采樣保持電路,減少了外部元件的使用。

-

內部參考輸出:參考輸出電壓范圍為2.4V至3.6V,兼容多種應用。

(二)性能優勢

- 低功耗:正常工作模式下功耗為150 mW,掉電模式下僅為15 mW。

- 高分辨率:分辨率達到14位,無丟失碼。

- 優秀的動態性能:SNR($f{IN}=10 MHz$)典型值為74 dB,SFDR($f{IN}=10 MHz$)典型值為93 dB。

三、關鍵參數

(一)靜態參數

| 參數 | 典型值 | 極限值 | 單位 |

|---|---|---|---|

| 分辨率 | 14 | Bits (min) | |

| 積分非線性 (INL) | ±1.4 | ±3.8 | LSB (max) |

| 差分非線性 (DNL) | ±0.5 | ±1.0 | LSB (max) |

| 正增益誤差 (PGE) | ±0.3 | - | %FS (max) |

| 負增益誤差 (NGE) | ±0.3 | - | %FS (max) |

| 增益誤差溫度系數 (TC GE) | - | - | ppm/°C |

| 偏移誤差 (VoFF) | 0.85 | - | %FS (max) |

| 偏移誤差溫度系數 (TC VoFF) | - | - | ppm/°C |

(二)動態參數

| 參數 | 條件 | 典型值 | 極限值 | 單位 |

|---|---|---|---|---|

| 全功率帶寬 (FPBW) | 0dBFS輸入,輸出 -3 dB | 150 | - | MHz |

| 信噪比 (SNR) | $f_{IN}=1 MHz$ | 74 | - | dBc |

| $f_{IN}=10 MHz$ | 74 | 72.3 | dBc | |

| 無雜散動態范圍 (SFDR) | $f_{IN}=1 MHz$ | 93 | - | dBc |

| $f_{IN}=10 MHz$ | 93 | 81 | dBc |

四、應用領域

ADC14L020憑借其出色的性能,廣泛應用于以下領域:

五、設計要點

(一)電源設計

- 電源旁路:電源引腳需要用10 μF電容和0.1 μF陶瓷芯片電容進行旁路,且靠近每個電源引腳。優先選擇無引線芯片電容,因為它們的串聯電感較低。

-

電源噪聲:模擬電源引腳的噪聲應保持在100 mVP - P以下,以確保轉換器的性能。

(二)輸入設計

- 參考輸入:VREF引腳可選擇內部參考或提供外部參考。使用外部參考時,VREF引腳需用0.1 μF電容旁路至地。

-

模擬輸入:采用差分輸入時,ADC14L020性能最佳。單端輸入不推薦,但在必要時,可將一個模擬輸入連接到驅動輸入的直流中點電壓。輸入信號的峰值不應超過2.6V,共模輸入電壓$V_{CM}$應在0.5V至2.0V范圍內。

(三)時鐘設計

- 時鐘信號:CLK信號應使用穩定、低抖動的時鐘源驅動,上升和下降時間應小于2 ns。時鐘線應盡可能短,避免與其他信號線交叉。

- 時鐘終止:時鐘線應在源端以其特性阻抗進行端接,確保整個線路的時鐘線阻抗恒定。

-

時鐘占空比:ADC14L020具有占空比穩定器,可在20%至80%的時鐘占空比范圍內保持性能。

(四)輸出設計

- 輸出負載:輸出負載電容應控制在15 pF/pin以內,以避免$t_{OD}$增加,影響數據鎖存。

- 輸出緩沖:可使用緩沖器(如74ACQ541)連接在ADC輸出和其他電路之間,減少輸出負載電流。

-

輸出電阻:在數字輸出端靠近ADC引腳處插入約33Ω的串聯電阻,可隔離輸出與線路和其他電路電容,限制輸出電流。

(五)布局與接地

- 分區設計:電路板應保持模擬和數字區域分開,ADC14L020置于兩者之間,以減少干擾。

- 接地隔離:數據輸出的接地返回(DR GND)不應與ADC14L020的其他接地引腳在靠近的位置連接到系統接地。

- 信號隔離:模擬電路和數字電路應分開布局,時鐘線應盡可能短,避免與其他信號線交叉。

六、常見應用誤區及解決方法

(一)輸入電壓超出范圍

輸入電壓不應超過電源軌100 mV,否則可能導致故障或不穩定運行。可在有問題的數字輸入信號源附近串聯一個47Ω至100Ω的電阻來解決。

(二)驅動高電容數字數據總線

高電容負載會導致動態性能下降和$t_{OD}$增加。可通過適當的旁路、保持模擬和數字區域分開、緩沖數字數據輸出以及在數字輸出端添加串聯電阻來解決。

(三)使用不合適的放大器驅動模擬輸入

輸入電容會隨時鐘相位變化,需要使用能夠應對動態負載的放大器。如放大器出現過沖、振鈴或不穩定現象,可在放大器輸出端添加小串聯電阻,并在模擬輸入端添加電容來改善性能。

(四)參考引腳超出范圍

使用外部參考時,$V_{REF}$應在0.8V至1.2V范圍內,否則可能導致性能下降。

(五)時鐘源問題

時鐘源的抖動、過長的時鐘信號走線或其他信號耦合到時鐘信號走線,會導致采樣間隔變化,降低SNR和SINAD性能。應使用低抖動的時鐘源,縮短時鐘線長度,并避免與其他信號耦合。

七、總結

ADC14L020作為一款高性能的A/D轉換器,在低功耗、高分辨率和優秀的動態性能方面表現出色。然而,在設計過程中,我們需要注意電源、輸入、時鐘、輸出、布局和接地等多個方面的要點,避免常見的應用誤區。只有這樣,才能充分發揮ADC14L020的性能,為我們的設計帶來更可靠、更高效的解決方案。希望本文能為電子工程師在使用ADC14L020進行設計時提供有價值的參考。

你在設計過程中是否遇到過類似A/D轉換器的其他問題呢?歡迎在評論區分享你的經驗和見解。

-

MSPS

+關注

關注

0文章

574瀏覽量

28945 -

輸出電壓

+關注

關注

2文章

2048瀏覽量

41106 -

A/D轉換器

+關注

關注

1文章

177瀏覽量

11779 -

數字轉換器

+關注

關注

0文章

347瀏覽量

28761 -

輸入信號

+關注

關注

0文章

559瀏覽量

13179

發布評論請先 登錄

ADC14L020數據轉換器,Vrm引腳在連接滑動變阻器后,電壓無法調節怎么解決?

ADC14L020,pdf datasheet (14-Bi

深入剖析ADC08500:高性能8位500 MSPS A/D轉換器的設計與應用

剖析ADC12L080:12位高速A/D轉換器的卓越性能與應用指南

深入解析ADC12020:12位、20 MSPS A/D轉換器的卓越性能與應用指南

深入剖析ADC14L020:14位、20 MSPS A/D轉換器的卓越性能與設計要點

深入剖析ADC14L020:14位、20 MSPS A/D轉換器的卓越性能與設計要點

評論