引言

在當今的電子技術領域,模擬 - 數字轉換器(ADC)扮演著至關重要的角色。它們是連接現實世界模擬信號與數字系統的橋梁,廣泛應用于通信、雷達、測試測量等眾多領域。TI公司的ADC11C125就是一款高性能的11位A/D轉換器,它以其卓越的性能和豐富的特性,為工程師們提供了一個強大的工具。今天,我們就來深入剖析這款ADC11C125,了解它的技術特點、應用場景以及設計要點。

文件下載:adc11c125.pdf

一、產品概述

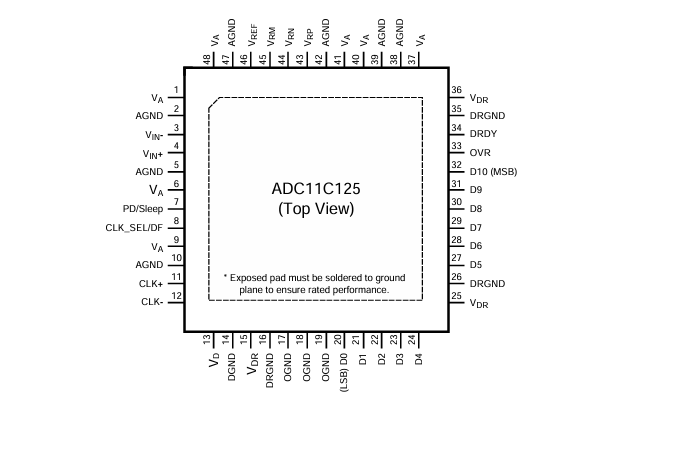

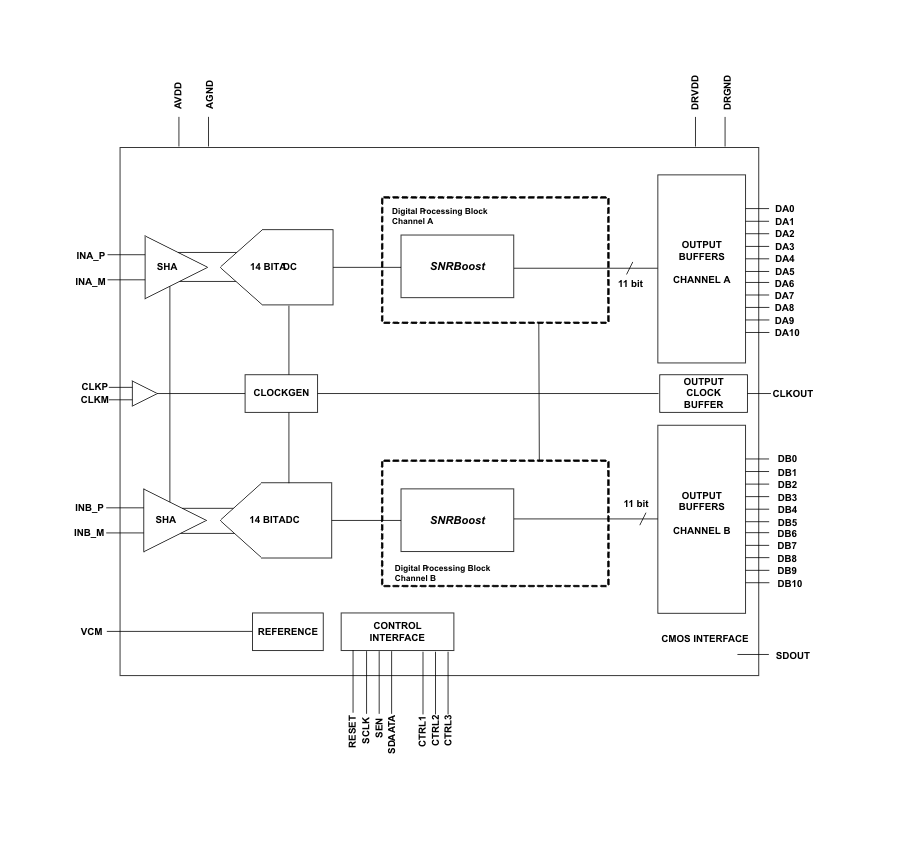

ADC11C125是一款高性能的CMOS模擬 - 數字轉換器,能夠以高達125兆樣本每秒(MSPS)的速率將模擬輸入信號轉換為11位數字字。它采用了差分流水線架構,結合數字誤差校正和片上采樣保持電路,在降低功耗和外部組件數量的同時,提供了出色的動態性能。其獨特的采樣保持級實現了1.1 GHz的全功率帶寬,使其適用于多種高頻應用場景。

(一)主要特性

- 高帶寬:全功率帶寬達到1.1 GHz,能夠處理高頻輸入信號。

- 低功耗:典型功耗為608 mW,并且支持掉電和睡眠模式,進一步降低功耗。

- 內部參考:具備內部精密1.0V參考,也可使用外部參考。

- 靈活的時鐘模式:支持單端或差分時鐘模式,以及時鐘占空比穩定器。

- 多種輸出格式:提供偏移二進制或2的補碼輸出數據格式。

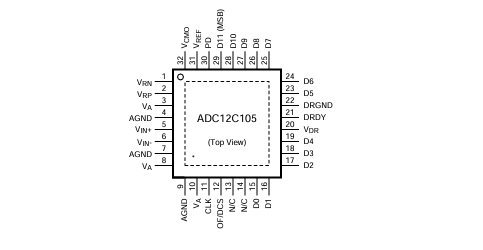

- 引腳兼容:與ADC14155、ADC12C170、ADC11C170引腳兼容。

- 小型封裝:采用48引腳WQFN封裝(7x7x0.8mm,0.5mm引腳間距)。

(二)應用領域

- 高IF采樣接收器:用于處理高頻中頻信號的采樣。

- 無線基站接收器:提高基站接收信號的處理能力。

- 功率放大器線性化:優化功率放大器的性能。

- 多載波、多模式接收器:適應復雜的通信環境。

- 測試和測量設備:提供高精度的信號采集。

- 通信儀器:保障通信系統的穩定運行。

- 雷達系統:實現雷達信號的準確處理。

二、關鍵規格參數

(一)基本參數

- 分辨率:11位

- 轉換速率:125 MSPS

- 信噪比(SNR):在$f_{IN}=70 MHz$時,典型值為65.5 dBFS

- 無雜散動態范圍(SFDR):在$f_{IN}=70 MHz$時,典型值為88.2 dBFS

- 有效位數(ENOB):在$f_{IN}=70 MHz$時,典型值為10.5位

- 全功率帶寬:典型值為1.1 GHz

- 功耗:典型值為608 mW

(二)靜態特性

| 參數 | 條件 | 典型值 | 極限值 | 單位 |

|---|---|---|---|---|

| 分辨率(無缺失碼) | - | 11位(最小) | - | - |

| 積分非線性(INL) | 滿量程輸入 | ±0.25 |

-0.83 LSB(最小) 0.83 LSB(最大) |

LSB |

| 差分非線性(DNL) | 滿量程輸入 | ±0.20 | -0.55 LSB(最小) | LSB |

| 正增益誤差(PGE) | - | +1.1 |

-1.8 %FS(最小) 4.0 %FS(最大) |

%FS |

| 負增益誤差(NGE) | - | -0.77 |

-3.7 %FS(最小) 2.2 %FS(最大) |

%FS |

| 增益誤差溫度系數(TC GE) | -40°C ≤$T_{A}$ ≤ +85°C | TBD | - | ppm/°C |

| 偏移誤差(VOFF) | $V{IN+} = V{IN-}$ | -0.11 |

-1.03 %FS(最小) 0.78 %FS(最大) |

%FS |

| 偏移誤差溫度系數(TC VOFF) | -40°C ≤$T_{A}$ ≤ +85°C | TBD | - | ppm/°C |

| 欠量程輸出碼 | - | 0 | 0 | - |

| 過量程輸出碼 | - | 2047 | 2047 | - |

(三)動態特性

| 參數 | 條件 | 典型值 | 極限值 | 單位 |

|---|---|---|---|---|

| 全功率帶寬(FPBW) | -1 dBFS輸入,-3dB轉角 | 1.1 | - | GHz |

| 信噪比(SNR) | $f_{IN}=10 MHz$ | 65.7 | 64.5 | dBFS |

| $f_{IN}=70 MHz$ | 65.5 | - | dBFS | |

| $f_{IN}=146 MHz$ | 65.4 | - | dBFS | |

| $f_{IN}=220 MHz$ | 64.9 | - | dBFS | |

| $f_{IN}=398 MHz$ | 64.5 | - | dBFS | |

| 無雜散動態范圍(SFDR) | $f_{IN}=10 MHz$ | 87.1 | 76.0 | dBFS |

| $f_{IN}=146 MHz$ | 83.4 | - | dBFS | |

| $f_{IN}=220 MHz$ | 84.9 | - | dBFS | |

| $f_{IN}=398 MHz$ | 75.7 | - | dBFS | |

| 有效位數(ENOB) | $f_{IN}=70 MHz$ | - | 10.4 | 位 |

| $f_{IN}=146 MHz$ | - | 10.4 | 位 | |

| $f_{IN}=220 MHz$ | - | 10.4 | 位 | |

| $f_{IN}=10 MHz$ | 10.6 | - | 位 | |

| $f_{IN}=398 MHz$ | 10.3 | - | 位 | |

| 總諧波失真(THD) | $f_{IN}=10 MHz$ | -83.3 | - | dBFS |

| $f_{IN}=70 MHz$ | -85.7 | - | dBFS | |

| $f_{IN}=146 MHz$ | -79.5 | -76.4 | dBFS | |

| $f_{IN}=220 MHz$ | -81.8 | - | dBFS | |

| $f_{IN}=398 MHz$ | -74.1 | - | dBFS | |

| 二次諧波失真(H2) | $f_{IN}=10 MHz$ | -97.7 | - | dBFS |

| $f_{IN}=146 MHz$ | -83.4 | - | dBFS | |

| $f_{IN}=220 MHz$ | -98.0 | - | dBFS | |

| $f_{IN}=398 MHz$ | -82.2 | - | dBFS | |

| 三次諧波失真(H3) | $f_{IN}=10 MHz$ | -88.2 | - | dBFS |

| $f_{IN}=70 MHz$ | -90.8 | - | dBFS | |

| $f_{IN}=146 MHz$ | -85.8 | - | dBFS | |

| $f_{IN}=220 MHz$ | -84.9 | - | dBFS | |

| $f_{IN}=398 MHz$ | -75.7 | - | dBFS |

三、功能描述

(一)工作原理

ADC11C125采用差分流水線架構,結合數字誤差校正和片上采樣保持電路。在采樣階段,模擬輸入信號通過NMOS開關連接到采樣電容,電容跟蹤輸入信號的變化。當時鐘從高電平變為低電平時,進入保持階段,模擬輸入與采樣電容斷開,采樣電容上的電壓被保持并送入ADC核心進行轉換。轉換結果以11位數字字的形式輸出,輸出格式可以是偏移二進制或2的補碼。

(二)時鐘與數據輸出

時鐘信號控制采樣過程,模擬輸入在時鐘的下降沿被采集。用戶可以通過CLK_SEL/DF引腳選擇單端或差分時鐘模式,以及輸出數據格式。數字輸出是CMOS兼容信號,由同步數據就緒輸出信號(DRDY)進行時鐘控制,數據在DRDY信號的下降沿輸出,并延遲7個時鐘周期。數據應在DRDY信號的上升沿進行捕獲。

(三)功率管理

通過PD/Sleep引腳可以選擇掉電或睡眠模式。當PD/Sleep引腳為高電平時,除電壓參考電路外的所有電路都被禁用,功耗降至5 mW。當PD/Sleep引腳偏置為$V_{A} / 2$時,芯片進入睡眠模式,除電壓參考電路及其片上緩沖器外的所有電路都被禁用,功耗降至50 mW。正常操作時,PD/Sleep引腳應連接到模擬地(AGND)。

四、應用設計要點

(一)模擬輸入

- 信號輸入:ADC11C125有一對差分模擬輸入引腳$V{IN}+$和$V{IN}-$,輸入信號應滿足一定的幅度和相位要求。建議使用源阻抗小于100Ω的信號源驅動模擬輸入,并匹配差分輸入的源阻抗,以提高偶次諧波性能。

- 采樣保持電路:模擬輸入引腳的電容在采樣和保持階段會發生變化,采樣階段約為9 pF,保持階段約為6 pF。在設計時需要考慮這種電容變化對信號的影響,確保采樣電容能夠在時鐘信號變低之前穩定充電,以避免影響SFDR性能。

- 單端轉差分轉換:對于單端輸入信號,可以使用變壓器或差分放大器進行轉換。變壓器適用于高頻輸入信號,但低頻性能較差;差分放大器適用于低頻應用,需要能夠快速從采樣保持操作引起的充電毛刺中恢復。

- 輸入共模電壓:輸入共模電壓$V{CM}$應在1.4V至1.6V之間,建議使用$V{RM}$(引腳45)作為輸入共模電壓,以確保模擬信號的峰值不超過地或2.6V。

(二)參考引腳

ADC11C125可以使用內部1.0V參考或外部參考,外部參考電壓范圍為0.9V至1.1V。$V_{REF}$引腳應始終通過一個0.1 μF電容旁路到地。較低的參考電壓會降低ADC的信噪比,而高于1.1V的參考電壓可能會在滿量程輸入時降低THD,特別是在較高輸入頻率下。所有與參考電壓和模擬輸入信號相關的接地應在一個安靜的單點連接到接地平面,以減少接地路徑中的噪聲電流影響。

(三)時鐘輸入

- 時鐘模式選擇:通過CLK_SEL/DF引腳可以選擇單端或差分時鐘模式,以及輸出數據格式。在差分時鐘模式下,兩個時鐘信號應相差180°且幅度相同;在單端時鐘模式下,時鐘信號應連接到CLK+輸入,CLK - 輸入應連接到AGND。

- 時鐘信號質量:為了獲得最佳的噪聲性能,時鐘輸入應使用穩定、低抖動的時鐘信號,并且具有較短的過渡區域。可以通過高速緩沖門對低抖動正弦時鐘源進行處理來實現。時鐘線應盡可能短,避免與其他信號線路交叉。

- 時鐘線終端匹配:時鐘線應在其源端進行特性阻抗終端匹配,以保持時鐘線阻抗的恒定。如果時鐘源驅動多個設備,每個驅動引腳應通過串聯RC到地進行交流終端匹配,以減少反射和干擾。

- 時鐘占空比:ADC11C125具有占空比穩定器,能夠在30%至70%的時鐘占空比范圍內保持性能穩定。

(四)數字輸出

- 輸出信號:ADC11C125的數字輸出包括11個數據輸出位(D0 - D10)、數據就緒信號(DRDY)、過范圍指示(OVR)和三個輸出接地引腳(OGND)。數據應在DRDY信號的上升沿進行捕獲和鎖存。

- 負載電容:驅動高電容總線時需要特別小心,因為輸出驅動器需要為每個轉換充電的電容越大,瞬時數字電流就越大,可能會導致片上接地噪聲并耦合到模擬電路中,降低動態性能。應確保輸出電容不超過指定的5 pF/引腳,以避免影響$t_{OD}$和動態性能。

- 噪聲抑制:為了減少輸出開關引起的噪聲,應盡量減少數字輸出的負載電流。可以使用可編程邏輯器件(PLD)進行電平轉換,將ADC輸出數據從1.8V轉換為3.3V。每個輸出引腳應只連接一個負載,并在數字輸出端插入約22Ω的串聯電阻,以限制輸出電流。

(五)電源供應

- 電源旁路:每個電源引腳應通過一個0.1 μF電容和一個0.01 μF陶瓷芯片電容進行旁路,優先選擇無鉛芯片電容,以降低串聯電感。

- 電源噪聲:ADC11C125對電源噪聲敏感,模擬電源引腳的噪聲應保持在100 mVP - P以下。在電源開啟和關閉過程中,要特別注意避免引腳電壓超過電源電壓。

- 輸出驅動器電源:$V{DR}$引腳為輸出驅動器提供電源,電壓范圍為1.6V至2.0V。較低的$V{DR}$電壓可以降低功耗和噪聲耦合,但會增加$t_{OD}$。如果需要將ADC11C125的數字輸出信號與非1.8V CMOS設備接口,可能需要使用電平轉換器。

(六)布局和接地

- 分區布局:將電路板分為模擬和數字區域,ADC11C125應位于這兩個區域之間。所有模擬電路應放置在模擬區域,所有數字電路和動態I/O線應放置在數字區域。

- 接地處理:數據輸出的接地返回(DRGND)應避免與ADC11C125的其他接地引腳在近距離連接到系統地,以防止輸出電流的高瞬變對轉換過程產生噪聲影響。所有與參考電路和輸入信號鏈連接到地的組件應通過短走線連接在一起,并在一個安靜的單點進入接地平面。

- 信號布線:模擬和數字線路應盡量避免交叉,時鐘線應盡可能短,并與所有其他線路隔離,包括其他數字線路。電感和變壓器應避免并排放置,以防止磁耦合。模擬輸入應與噪聲信號跡線隔離,外部組件應連接到接地平面的干凈點。

五、動態性能優化

為了實現最佳的動態性能,驅動CLK輸入的時鐘源必須具有尖銳的過渡區域和無抖動。可以使用緩沖器將ADC時鐘與任何數字電路隔離,如時鐘樹所示。時鐘樹中使用的門必須能夠在比實際使用頻率高得多的頻率下工作,以防止引入額外的抖動。與差分時鐘相比,單端驅動輸入可以獲得更好的性能。

六、總結

ADC11C125是一款功能強大、性能卓越的11位A/D轉換器,適用于多種高頻、高性能應用場景。在設計應用時,需要充分考慮其模擬輸入、參考引腳、時鐘輸入、數字輸出、電源供應、布局和接地等方面的要求,以確保其能夠發揮最佳性能。通過合理的設計和優化,ADC11C125可以為工程師們提供一個可靠的解決方案,滿足各種復雜應用的需求。

希望本文能夠對廣大電子工程師在使用ADC11C125進行設計時有所幫助。如果你在實際應用中遇到任何問題,歡迎在評論區留言討論。讓我們一起探索電子技術的無限可能!

-

CMOS

+關注

關注

58文章

6221瀏覽量

243193 -

帶寬

+關注

關注

3文章

1048瀏覽量

43513 -

A/D轉換器

+關注

關注

1文章

217瀏覽量

11911 -

數字轉換器

+關注

關注

0文章

348瀏覽量

28837 -

輸入信號

+關注

關注

0文章

559瀏覽量

13204

發布評論請先 登錄

ADC11C125,pdf datasheet (11-Bi

ADC11C170CISQ 11位模數帶寬A/D轉換器的規格參數

ADS5517高性能11位、200 MSPS A/D轉換器數據表

ADS5510高性能、11位、125 MSPS模數轉換器(ADC)數據表

深度剖析ADC11C125:高性能11位A/D轉換器的技術與應用

深度剖析ADC11C125:高性能11位A/D轉換器的技術與應用

評論