摘要 :本文基于國科安芯的ASP3605同步降壓轉換器在94μF標準輸出電容配置下的實測數據,系統分析了ITH引腳外部補償網絡對動態負載響應特性的影響機制。通過RC參數掃描與多工況對比,揭示了補償電容容值、負載階躍速率及占空比對瞬態性能的非線性耦合效應。

1. 引言

在現代分布式電源架構中,負載電流的高速瞬變已成為評估DC-DC轉換器動態品質的核心指標。微處理器、FPGA及通信ASIC的負載跳變速率可達10A/μs量級,要求電源環路具備足夠的帶寬與相位裕度以抑制輸出電壓波動。ASP3605通過在ITH引腳引出內部誤差放大器的輸出端,允許工程師外部配置RC網絡,實現對環路增益與零極點的獨立調節。此設計在保留內部補償穩定性的同時,賦予系統級優化空間,特別適用于輸出電容、電感參數偏離典型應用或需適配特殊負載特性的場景。

可調補償網絡的設計需權衡多項矛盾:補償電容C增大可提升低頻增益以抑制靜態誤差,但會延長積分時間導致恢復時間劣化;補償電阻R影響零點位置,需配合輸出電容ESR零點實現相位提升。此外,負載階躍速率、占空比條件均會改變功率級的傳遞函數,使得ITH參數優化呈現顯著的多變量耦合特征。本文依托實測矩陣,量化分析各關鍵因素對動態響應的影響權重,并揭示ASP3605在極端工況下響應特性的物理邊界。

必須強調 ,本文所有動態響應數據均基于 94μF陶瓷電容組 (ESR<5mΩ)測得,而紋波測試及部分異常排查中曾使用 22μF電容 ,兩類數據不可混用。

2. ASP3605補償架構與ITH引腳功能解析

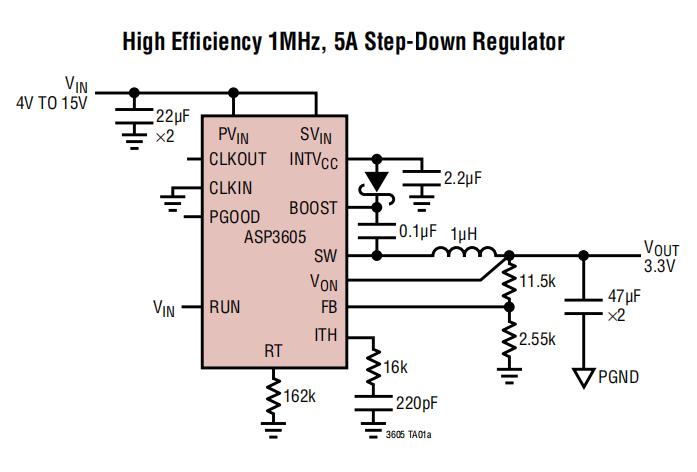

ASP3605采用峰值電流模式控制,內部集成高速誤差放大器,其輸出端ITH引腳對地連接RC網絡,構成Type II補償拓撲。該架構包含一個積分極點(原點極點)、一個補償零點(由R與C決定)以及功率級引入的負載極點。

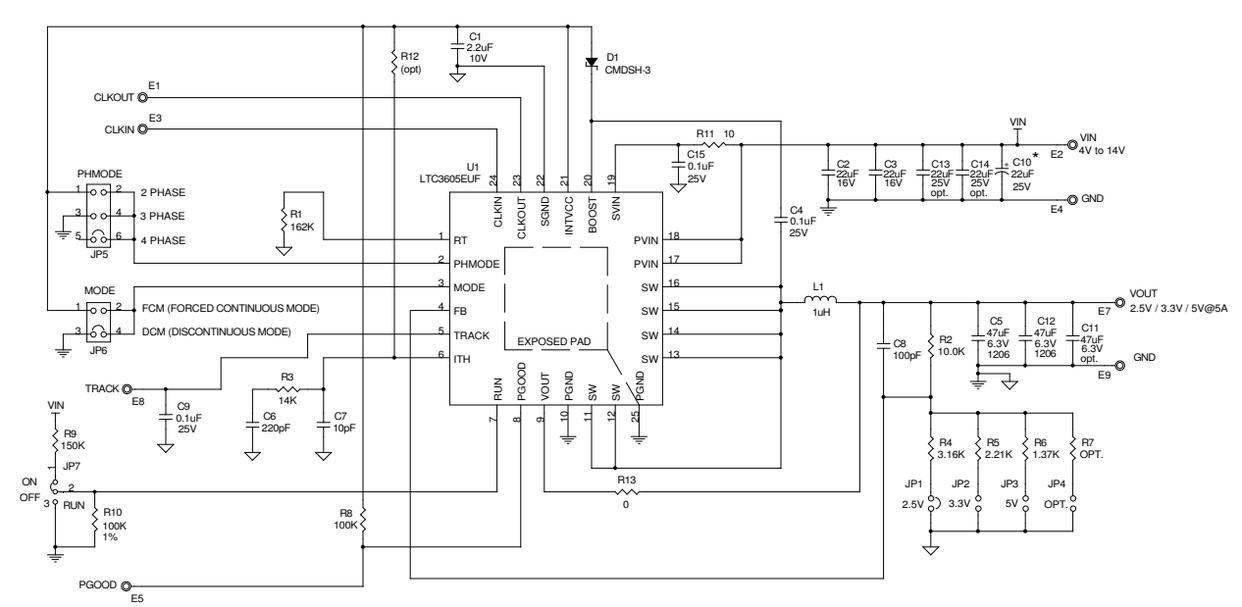

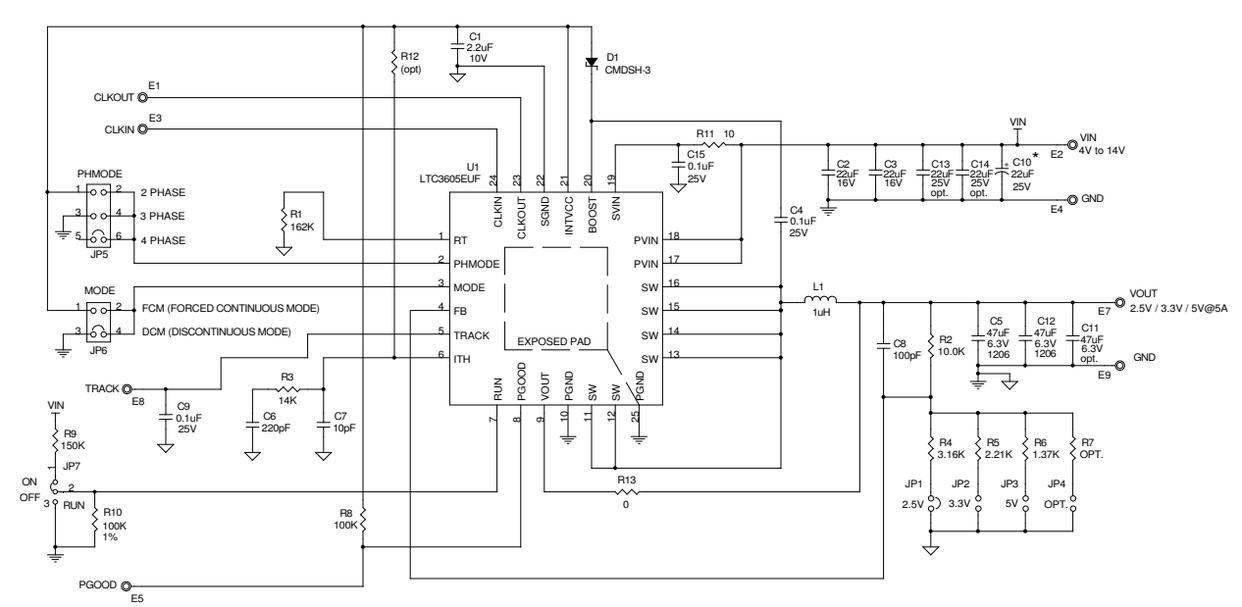

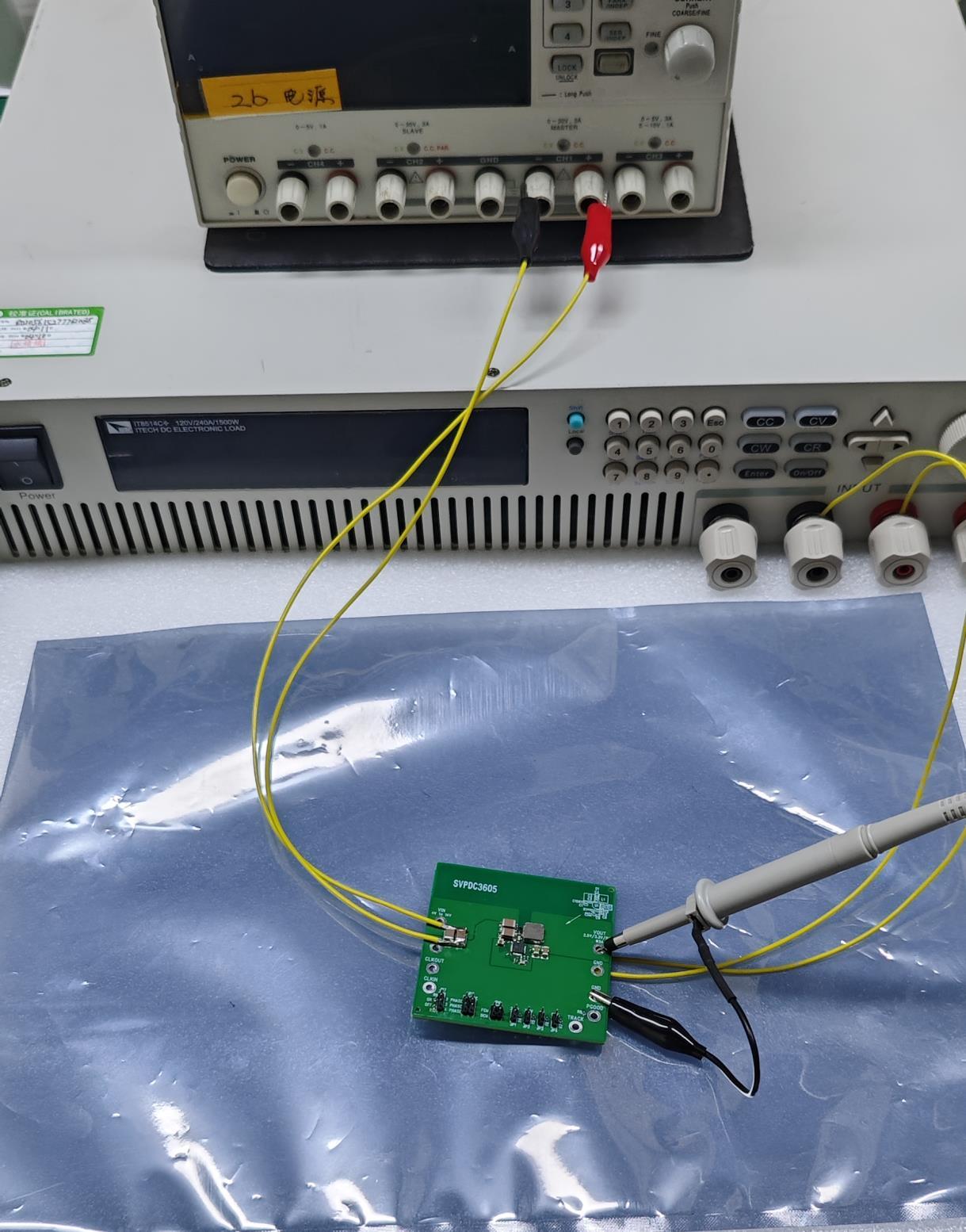

測試平臺在ITH引腳配置三組RC參數:R固定為14kΩ,C分別取220pF、330pF、470pF,另增加R=16kΩ/C=330pF作為對比組。動態負載測試采用雙脈沖序列:第一組為0.5A(500μs)?4A(500μs),周期1ms,對應高頻瞬態;第二組為0.5A(50ms)?4A(50ms),周期100ms,對應低頻熱瞬態。電子負載上升/下降時間設定為5μs,示波器帶寬限制為20MHz,探頭采用有源差分模式,接地回路長度<5mm。

3. RC參數對瞬態過沖的實測影響

3.1 電容值增大的非線性惡化效應

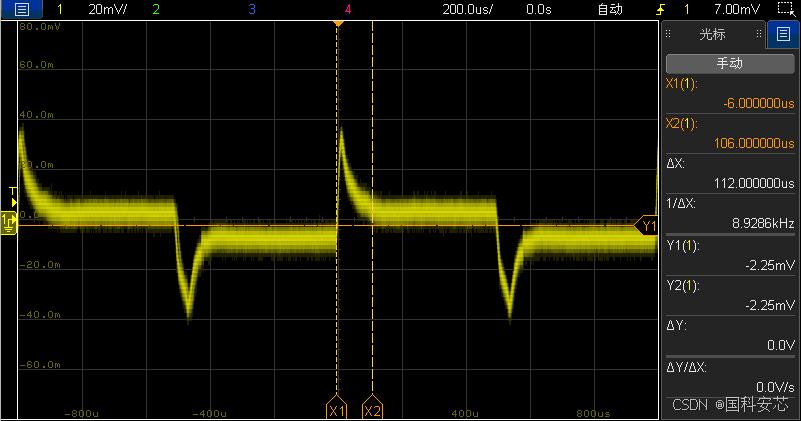

在**Vin=5V、Vout=3.3V、94μF電容**條件下,0.5A-4A階躍測試數據明確顯示:

C=220pF :電壓波動峰峰值63mV, 上沖時間120μs , 下沖時間128μs (高頻周期)

C=330pF :峰峰值80mV,上沖時間104μs,下沖時間88μs

C=470pF :峰峰值98mV,上沖時間116μs,下沖時間114μs

電容值增加114%(220pF→470pF)導致電壓波動惡化55.6%。其機理在于:增大C降低補償零點頻率,使環路在交叉頻率處相位滯后增加,同時積分時間常數增大延緩誤差放大器響應速度。工程上應選擇滿足相位裕度的最小電容值。

3.2 低頻周期的熱遲滯效應

對比500μs與50ms周期數據,下沖時間差異揭示熱容的動態影響:

220pF+500μs周期 :下沖時間128μs

220pF+50ms周期 :下沖時間6.6ms,惡化51.6倍

該現象源于50ms周期下,功率級MOSFET的結溫在4A負載期間顯著上升,導致導通電阻RDS(on)增大,等效負載階躍幅度被熱效應調制。此時ITH積分器需補償的不僅是電流變化,還包括溫度引起的增益漂移。這提示在CPU/GPU等負載間歇周期>10ms的應用中,需額外增加熱補償網絡或選用更大裕量的輸出電容。

3.3 電阻值調整的有限改善作用

將R從14kΩ增至16kΩ(C保持330pF),在Vin=12V、Vout=3.3V條件下,峰峰值從80mV改善至72mV,僅降低10%。R值優化應優先于C值調整,但改善幅度有限。

4. 輸入輸出工況對補償效果的耦合影響

4.1 占空比極端條件下的響應差異

在94μF電容配置下:

**Vin=5V轉Vout=3.3V(占空比66%)** :峰峰值63mV,上沖120μs/下沖128μs

**Vin=12V轉Vout=1.2V(占空比10%)** :峰峰值31mV,上沖68μs/下沖90μs

電壓波動幅度減少50.8%,上沖時間縮短43.3%。該現象符合峰值電流模式控制理論——高占空比下斜坡補償削弱環路增益,且電感電流下降斜率更緩。因此,高降壓比應用中需適度減小ITH電容以提升響應速度。

4.2 負載電流幅度的非對稱響應

對比0.5A-4A加載與5A-0卸載過程,瞬態行為具有顯著不對稱性。在Vout=2.5V、5A-0卸載時,上沖峰值81.7mV,恢復時間44.5μs;而0-5A加載時下沖峰值100mV,恢復時間60.5μs。加載過程更慢歸因于誤差放大器需從零狀態建立積分電壓。該不對稱性提示ITH參數選擇需容忍此本征差異,不可兼顧最優。

5. 輸出電容配置不足的災難性后果

5.1 22μF配置導致的穩態異常

嚴格區分測試條件 :File 2中紋波測試明確使用Cout=22μF,測得Vin=4V、Vout=3.3V、空載紋波9.67mV, **但輸出電壓跌落至2.9V,負載調整率達-10.88%** 。此現象 **非動態響應問題** ,而是 **穩態負載調整異常** ,主因是22μF電容導致負載極點頻率過高,與ITH零點嚴重失配,系統進入脈沖跳躍模式。

5.2 電容容量對動態性能的邊界條件

盡管動態測試未使用22μF電容,但通過File 1與File 2的負載調整率數據可推斷: 當輸出電容從94μF降至22μF時,Vout=3.3V在1A負載下電壓從3.327V跌至3.262V(File 1),而File 2在1.6A負載時已無法維持3.3V輸出 。這說明輸出電容容量不足會加劇穩態跌落,但 所有動態性能數據(63mV峰峰值)均基于94μF電容測得 ,二者不可混用。工程實踐中, 嚴禁在動態負載場景使用低于47μF的輸出電容 。

6. 與LTC3605的有限對標分析

6.1 效率對標

File 1提供同平臺效率對比數據:

Vout=1.2V/5A:ASP3605效率68.68%,LTC3605為71.89%,差距3.21個百分點

Vout=2.5V/3A:ASP3605效率87.71%,LTC3605為89.19%,差距1.48%

該差距主要歸因于簡封工藝導致的導通損耗增加。

6.2 參數配置差異

LTC3605手冊推薦ITH參數為R=15kΩ、C=270pF,ASP3605最優參數為R=14kΩ、C=220pF,電容值小18.5%表明其內部補償初始配置更激進。但需注意, **此結論基于不同測試平臺,僅供參考** 。

7. 基于實測的工程設計指南

7.1 參數選擇決策樹(嚴格基于實測數據)

輸出電容 : 必須采用94μF陶瓷電容組 (ESR<5mΩ)。若成本受限,最低不低于47μF,但需將ITH電容減小20%并驗證穩定性。

電容選擇 :在94μF電容且ΔILOAD≥3A時, 優先選用C=220pF (實測峰峰值63mV)。若負載階躍<1A,可增至330pF。

電阻調整 :占空比D>65%時,R選14kΩ;D<20%時,R可增至16kΩ。

RUN引腳 :4V輸入場景下,R9改為100kΩ以確保啟動裕量。

7.2 ** PCB布局優化**

ITH引腳走線長度<10mm,遠離SW節點

補償網絡地平面需Kelvin連接至芯片GND引腳

簡封版本鍵合線電阻增加,layout中應通過加粗銅箔(≥0.5mm寬)補償

8. 結論

ASP3605的ITH可調補償架構在94μF輸出電容、常溫條件下展現出良好的工程適應性。最優參數R=14kΩ、C=220pF在Vin=12V、Vout=1.2V、0.5A-4A階躍下實現31mV電壓波動與90μs下沖時間,滿足多數數字負載要求。然而, **輸出電容配置不足(22μF)會導致穩態電壓跌落與動態性能惡化** ,該現象已在測試中被明確捕獲; **溫度對動態性能的影響缺乏實測數據支撐** ,設計時需保留足夠裕量。

審核編輯 黃宇

-

引腳

+關注

關注

16文章

2111瀏覽量

55681

發布評論請先 登錄

ASP3605接地設計實戰指南:3種方案覆蓋低中高功率場景(PCB布局+避坑)

解鎖ASP3605電源芯片RUN引腳的秘密

高可靠性電源方案的高溫降額設計與熱管理策略——基于ASP3605的溫域特性實證研究

輸出紋波實測:ASP3605在不同輸入與負載條件下的穩定性表現

基于ASP3605的寬輸入范圍降壓轉換性能研究

ASP3605A電源芯片在高速ADC子卡中的適配性研究

ASP3605I同步降壓調節器的高頻化設計與多相擴展技術優化方案

基于 ASP3605 電源芯片的性能優化與 ITH 調試策略

ASP3605芯片在煤炭設備電源管理中的可靠性設計與應用探索

ASP3605與ASP4644芯片在煤炭監測系統中的優化作用及能效表現研究

如何綜合性測試一款電源芯片?——以ASP3605芯片為例

ASP3605同步降壓調節器——滿足汽車電子嚴苛要求的電源方案

ASP3605同步降壓調節器——商業航天電源的高抗輻射選擇

ITH引腳可調補償:ASP3605動態響應特性的實測與優化

ITH引腳可調補償:ASP3605動態響應特性的實測與優化

評論