VSP5610/11/12是高速、高性能的16位模數轉換器(ADC),擁有四個獨立采樣電路通道,用于多輸出電荷耦合器件(CCD)和互補金屬氧化物半導體(CMOS)線傳感器。傳感器的像素數據通過采樣/保持(SH)或相關雙采樣器(CDS)電路采樣,然后由ADC轉換為數字數據。數據輸出可在低電壓差分信令(LVDS)或CMOS模式下選擇。

*附件:vsp5610.pdf

VSP5610/11/12 包含可編程增益,以支持亮度引起的像素級曲折。集成的數字轉模擬轉換器(DAC)可用于調整模擬輸入信號的偏移電平。此外,這些設備集成了定時發生器(TG)用于傳感器工作控制。

VSP5610/11/12 的磁芯電壓為1.65V至1.95V,I/O電壓為3.0V至3.6V。鐵芯電壓由內置低壓衰減器(LDO)提供。

特性

- 四通道CCD/CMOS信號:可選擇2通道、3通道和4通道

- 電源:僅3.3 V,類型

(內置LDO,3.3 V至1.8 V) - 最大轉化率:

- VSP5610:35 MSPS

- VSP5611:50 MSPS

- VSP5612:70 MSPS

- 16位分辨率

- CDS/SH 可選擇

- 最大輸入信號范圍:2.0 V

- 模擬與數字混合增益:

- 模擬增益:0.5 V/V 到 3.5 V/V,每

3/64 V/V 步進 - 數字增益:1 V/V到2 V/V,每

1/256 V/V步進

- 模擬增益:0.5 V/V 到 3.5 V/V,每

- 偏移校正DAC:±250 mV,8位

- 標準LVDS/CMOS可選輸出:

- LVDS:數據通道:2通道,3通道時鐘通道:1通道8位/7位串行器可選

- CMOS:4位×4,8位×2位

- 定時發生器:

- 快速傳輸時鐘:八個信號

- 慢傳時鐘:六個信號

- 時序調整分辨率:t

MCLK/48 - 輸入鉗位/輸入參考電平 內部/外部可選

- 參考DAC:0.5 V,1.1 V,1.5 V,2 V

- SPI?:三線串行

- GPIO:四端口

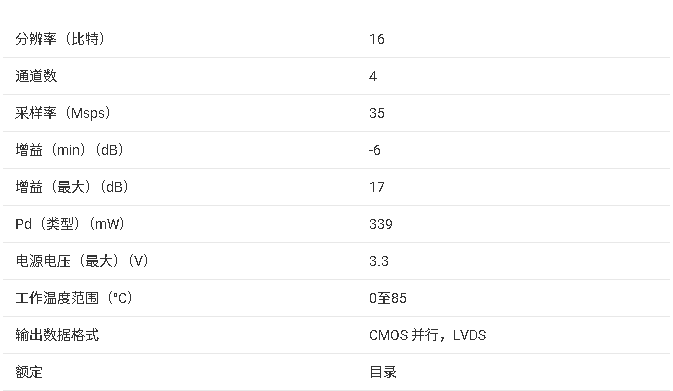

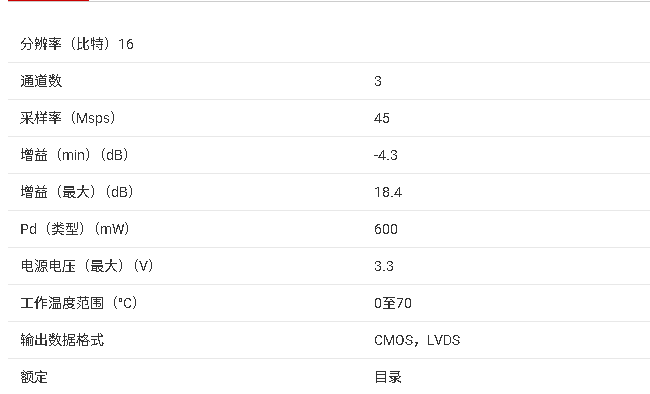

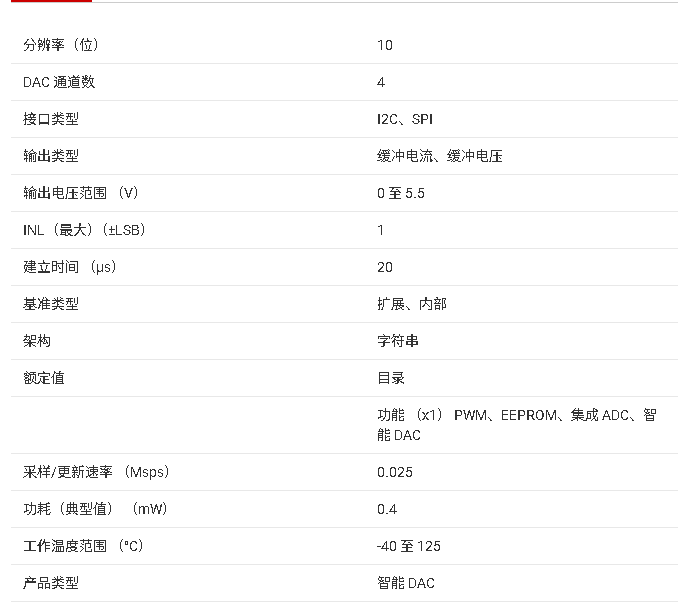

參數

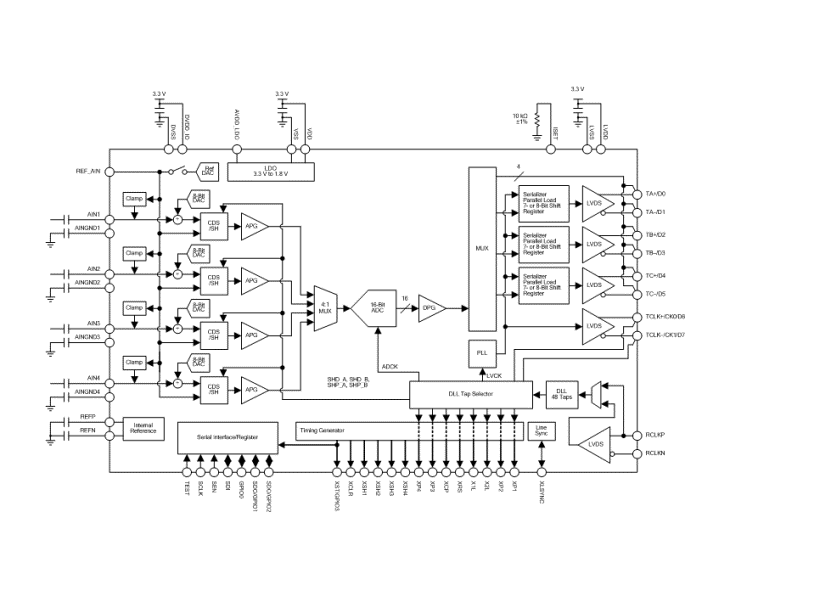

方框圖

VSP5610/11/12 是德州儀器(TI)推出的高性能多通道模擬前端芯片系列,核心優勢為 16 位高分辨率、2~4 通道靈活配置、集成采樣保持 / 相關雙采樣(SH/CDS)、可編程增益與時序發生器,支持 LVDS/CMOS 雙輸出模式,是復印機、傳真機、掃描儀等辦公自動化設備中 CCD/CMOS 線傳感器信號采集的專用解決方案。

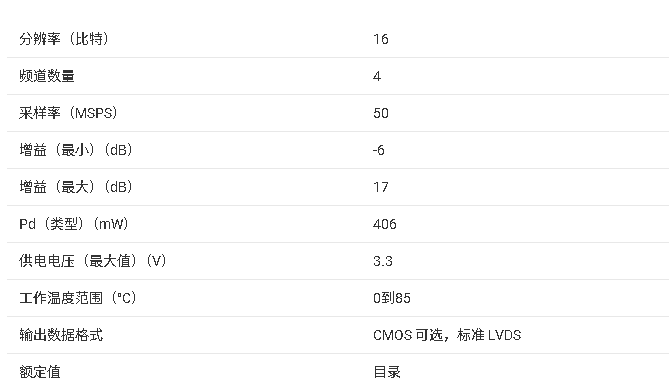

一、核心產品參數

1. 基礎性能指標

- 分辨率與轉換率 :16 位分辨率(無失碼),三型號核心差異為最大轉換率 ——VSP5610(35 MSPS)、VSP5611(50 MSPS)、VSP5612(70 MSPS),單通道最高速率分別達 11.66/16.66/23.33 MHz。

- 靜態精度 :微分非線性(DNL)±0.5 LSB,積分非線性(INL)±2 LSB;總絕對增益誤差 ±10%,信號完整性優異。

- 信號調理能力 :模擬增益 0.5

3.5 V/V(63 級步進),數字增益 1.02.0 V/V(255 級步進);8 位偏移校正 DAC(±250 mV 范圍),適配不同傳感器信號幅度。 - 動態性能 :信噪比(SNR)最高 76 dB,通道串擾≤±15 LSB,輸入等效噪聲低至 0.91 nV/rtHz,弱信號采集能力強。

2. 環境與封裝

- 工作溫度:0°C~85°C,適配辦公設備常規工作環境;

- 封裝形式:56 引腳 QFN(RSH 封裝),帶裸露熱焊盤,RoHS 兼容,MSL 等級 3(260°C 回流焊 168 小時);

- 功耗表現:VSP5612 LVDS 輸出模式功耗 542 mW,待機模式僅 15 mW,功耗與性能均衡;

- 供電電壓:單 3.3 V 供電,內置 LDO 將核心電壓轉換為 1.8 V,簡化供電設計。

二、關鍵功能特性

1. 采樣與信號調理

- 采樣模式:支持 CDS(相關雙采樣)與 SH(采樣保持)模式,CDS 可抑制 CCD 復位噪聲,SH 適配 CMOS/CCD 傳感器,通道獨立配置。

- 輸入鉗位:支持像素鉗位、行鉗位、無鉗位三種模式,鉗位電平可選擇固定 2.2 V、內部 DAC 輸出(0.5/1.1/1.5/2.0 V)或外部輸入,適配不同傳感器偏置需求。

- 參考與偏移校正:內置參考 DAC(輸出精度 ±10%),8 位偏移 DAC 可校正輸入信號直流偏移,溫度漂移 ±2%,穩定性強。

2. 輸出與控制

- 輸出接口:支持 LVDS(2

3 通道數據 + 1 通道時鐘)與 CMOS(4 位 ×4/8 位 ×2)雙模式,LVDS 差分輸出電壓 300400 mV,抗干擾能力強。 - 時序發生器(TG):集成 8 路快速傳輸時鐘、6 路慢速傳輸時鐘,時序調整分辨率 tMCLK/48,可直接驅動傳感器工作,無需外部時序芯片。

- 串行接口:3 線 SPI 控制,支持寄存器讀寫配置;4 路 GPIO,擴展靈活。

三、產品差異與選型

| 型號 | 最大轉換率 | 單通道最高速率 | 典型功耗(LVDS 模式) | 核心適配場景 |

|---|---|---|---|---|

| VSP5610 | 35 MSPS | 11.66 MHz | 339 mW | 低速率掃描儀、入門級復印機 |

| VSP5611 | 50 MSPS | 16.66 MHz | 426 mW | 中速辦公設備、傳真機 |

| VSP5612 | 70 MSPS | 23.33 MHz | 542 mW | 高速掃描儀、高端復印機 |

四、應用與設計要點

1. 典型應用場景

- 辦公自動化:復印機、傳真機、平板掃描儀的線陣 CCD/CMOS 傳感器信號采集;

- 工業檢測:低速率工業條碼掃描、小型圖像采集模塊。

2. 硬件設計建議

- 外部元件 :VDD/DVDD_IO/LVDD 引腳需就近并聯 0.1 μF 去耦電容;ISET 引腳外接 10 kΩ±1% 電阻,穩定內部參考電壓。

- 信號布線:模擬輸入(AINx)與地(AINGNDx)差分布線,減少串擾;LVDS 輸出線對長度匹配,降低信號失真。

- 通道配置:根據傳感器通道數選擇 2/3/4 通道模式,通過 AIN_CH_SEL 寄存器配置;CDS 模式適配 CCD,SH 模式適配 CMOS,按需切換。

3. 軟件與配置

- 增益選擇:弱信號場景選高模擬增益(如 3.5 V/V),避免數字增益引入噪聲;強信號場景選低增益,防止信號飽和。

- 時序配置:通過內部寄存器設置 TG 時鐘參數,同步傳感器的行周期與像素周期;CLPDM 周期配置在虛擬像素或光學黑像素區間,提升鉗位穩定性。

五、產品優勢與適配性

- 核心優勢:高度集成 SH/CDS、增益調節、時序發生器,減少外部元件;支持 LVDS/CMOS 雙輸出,適配不同后端處理芯片;單電源供電,簡化系統設計。

- 選型建議:根據設備掃描速率需求選擇型號 —— 低速設備選 VSP5610,中高速設備選 VSP5611/12;需長距離傳輸選 LVDS 輸出,短距離低成本場景選 CMOS 輸出。

-

CMOS

+關注

關注

58文章

6126瀏覽量

241432 -

adc

+關注

關注

100文章

7199瀏覽量

553454 -

模數轉換器

+關注

關注

26文章

3779瀏覽量

129650 -

耦合器件

+關注

關注

0文章

23瀏覽量

10440

發布評論請先 登錄

在做CCD的模擬信號采集硬件電路的設計?

基于lm9822的3通道42位彩色掃描儀前端模擬

用于成像信號的四通道模擬前端VSP7500和VSP7502的詳細資料概述

VSP5610/VSP5611/VSP5612 16位 4通道CCD/CMOS傳感器模擬前端數據表

Texas Instruments AFE159x 4通道24位模擬前端(AFE)數據手冊

類比半導體的模擬前端AFE型號有哪些

VSP5621 16 位 4 通道 CCD/CMOS 傳感器模擬前端技術文檔總結

LM98722 3 通道 16 位 45MSPS 模擬前端(AFE)產品手冊總結

VSP5610/11/12 4 通道 16 位 CCD/CMOS 傳感器模擬前端(AFE)總結

VSP5610/11/12 4 通道 16 位 CCD/CMOS 傳感器模擬前端(AFE)總結

評論