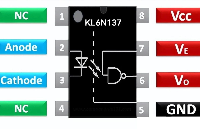

芯片中的 “腳位” 通常稱為引腳(Pin),是芯片與外部電路、設備連接的橋梁,其核心作用是實現芯片內部電路與外部電路之間的信號傳輸、電源供給、接地等功能。不同類型的引腳根據設計用途,功能各有不同,常見分類及作用如下:

| 引腳大類 | 細分類型 | 常見標識(含變體) | 詳細作用描述 | 典型應用場景(含芯片例子) |

|---|---|---|---|---|

| 一、供電與接地 | 主電源引腳 | VCC、VDD、VDD33(3.3V)、VDD5(5V) | 為芯片核心數字電路 / 邏輯單元提供工作電壓,是芯片運行的基礎能源。 | STM32F103 的 VDD 引腳(3.3V 供電核心 CPU);ATmega328P 的 VCC 引腳(5V 供電單片機)。 |

| 模擬電源引腳 | AVDD、VAA、VREF_IN | 為內部模擬電路(ADC、運放、基準源)提供低噪聲電壓,避免數字電源干擾。 | HT5943(ADC 芯片)的 AVDD 引腳(3.3V 供電模擬轉換電路);LM358 運放的 VCC(雙電源時為正模擬電源)。 | |

| I/O 接口電源引腳 | VDD_IO、VCC_IO | 單獨為芯片的 I/O 接口電路供電,匹配外部電路電壓(如 3.3V 與 5V 兼容)。 | FPGA(如 XC7K325T)的 VDD_IO 引腳(可配置為 3.3V/2.5V,匹配外部接口電壓)。 | |

| 數字地引腳 | GND、DGND、VSS | 數字電路的 0 電位參考點,形成數字信號電流回路,穩定邏輯電平。 | 74HC00(邏輯門芯片)的 GND 引腳;STM32 的 DGND(與模擬地 AGND 需單點連接)。 | |

| 模擬地引腳 | AGND、GND_A | 模擬電路的獨立接地,與數字地隔離(如通過 0 歐電阻或磁珠),減少數字噪聲干擾。 | ADC0809 的 AGND 引腳;LM358 運放的 GND(雙電源時為負模擬地)。 | |

| 功率地引腳 | PGND、GND_P | 為大電流模塊(如功率管、電機驅動)提供低阻抗接地路徑,通常與散熱片連接。 | LM2596(DC-DC 轉換器)的 PGND 引腳(大電流回路接地);L298N(電機驅動芯片)的 PGND(驅動電機電流回流)。 | |

| 二、數字 I/O | 通用 GPIO 引腳 | PA0、P1.2、GPIO_0、IO1 | 可通過軟件配置為輸入或輸出,靈活實現通用控制(讀按鍵 / 驅 LED)或復用功能。 | ATmega328P 的 PD2 引腳(可作 GPIO 輸入讀按鍵,也可復用為 INT0 中斷);ESP32 的 GPIO4(驅 LED 輸出)。 |

| 專用數字輸入引腳 | IN0、DI、SYS_EN(系統使能輸入) | 僅用于接收外部數字信號(高 / 低電平),控制芯片功能開啟 / 模式切換。 | 74HC138(譯碼器)的 A/B/C 引腳(輸入地址信號);TC4427(MOS 驅動)的 IN 引腳(輸入控制信號)。 | |

| 專用數字輸出引腳 | OUT0、DO、LED_DRV | 僅輸出數字信號(高 / 低電平),驅動外部負載(如 LED、繼電器)。 | 74HC595(移位寄存器)的 Q0-Q7 引腳(輸出并行數據);NE555 的 OUT 引腳(輸出方波信號)。 | |

| 三、模擬 I/O | ADC 輸入引腳 | AIN0、ADC_IN1、CH0 | 接收外部模擬電壓信號(如傳感器輸出),送入內部 ADC 轉換為數字量。 | STM32F103 的 PA0(ADC1_IN0,接溫度傳感器 LM35 輸出);ADS1115 的 A0-A3(4 路模擬輸入)。 |

| DAC 輸出引腳 | DAC_OUT、AOUT、V_OUT | 將內部數字量轉換為模擬電壓信號,輸出連續變化的模擬量。 | HT5010 的 IOUT1/IOUT2(電流輸出,需外接運放轉為電壓);STM32 的 DAC_OUT1(直接輸出 0-3.3V 電壓)。 | |

| 模擬差分輸入引腳 | AIN+/-、DIFF_IN+/- | 接收差分模擬信號(兩個反相電壓),通過差值計算抑制共模干擾(如電源噪聲)。 | 儀表放大器 AD8221 的 IN+/- 引腳(接橋式傳感器,抑制長線傳輸噪聲)。 | |

| 四、控制功能 | 復位引腳 | RESET、RST、NRST(低電平有效) | 接收復位信號(通常低電平 / 高電平有效),強制芯片回到初始狀態(寄存器清零等)。 | STM32 的 NRST 引腳(低電平觸發復位);51 單片機的 RST 引腳(高電平復位)。 |

| 片選引腳 | CS、SS、CS#(低電平有效)、CE | 多芯片共用總線時,通過該信號選中當前芯片(未選中時芯片不響應總線操作)。 | W25Q128(SPI Flash)的 CS# 引腳(低電平選中,高電平休眠);74HC573(鎖存器)的 LE(鎖存使能)。 | |

| 模式選擇引腳 | MODE0/1、CFG0/1、SEL0/1 | 通過外部電平組合(如 00/01/10/11)設置芯片工作模式(速率、精度等)。 | ADF4351(鎖相環芯片)的 MUXOUT 引腳(通過 MODE0/1 配置輸出模式);CH340(USB 轉串口)的 MODE 引腳(選擇串口波特率)。 | |

| 五、時鐘與定時 | 晶振輸入 / 輸出引腳 | XTAL1、XTAL2、OSC_IN、OSC_OUT | 連接外部晶振(如 8MHz),與內部振蕩器組成時鐘源,為芯片提供時序基準。 | 51 單片機的 XTAL1/XTAL2(接 11.0592MHz 晶振,用于 UART 波特率);STM32 的 OSC_IN/OSC_OUT(接 8MHz 晶振)。 |

| 外部時鐘輸入引腳 | CLK_IN、EXT_CLK | 接收外部時鐘信號(如方波、正弦波),作為芯片內部時序同步源。 | FPGA 的 CLK_IN 引腳(接 100MHz 差分時鐘源);74HC161(計數器)的 CLK 引腳(輸入計數時鐘)。 | |

| 定時器門控引腳 | GATE | 控制定時器 / 計數器的啟動 / 暫停(高電平有效時,僅時鐘信號有效)。 | 8253(定時器芯片)的 GATE 引腳(控制計數器是否響應 CLK 信號)。 | |

| 六、通信接口 | UART 引腳 | TXD(發送)、RXD(接收)、UART_TX | 異步串行通信,全雙工傳輸數據(無需時鐘同步),用于短距離低速通信。 | ESP8266 的 TXD/RXD(與 PC 串口通信);GPS 模塊的 TXD(輸出定位數據到單片機 RXD)。 |

| I2C 引腳 | SDA(數據線)、SCL(時鐘線) | 同步串行通信,半雙工,支持多主多從(通過地址區分),適合低速短距離。 | SHT30(溫濕度傳感器)的 SDA/SCL(與 STM32 的 I2C 接口通信);EEPROM(AT24C02)的 SDA/SCL。 | |

| SPI 引腳 | MOSI(主出從入)、MISO(主入從出)、SCK(時鐘)、CS(片選) | 同步串行通信,全雙工,高速(可達幾十 Mbps),適合短距離(如板內芯片通信)。 | W25Q128(SPI Flash)的 MOSI/MISO/SCK/CS(與 MCU 通信存儲程序);OLED 屏幕的 SPI 接口引腳。 | |

| CAN 總線引腳 | CAN_H、CAN_L、RX、TX | 差分信號傳輸,抗干擾強,適合工業環境長距離通信(如汽車電子)。 | MCP2551(CAN 收發器)的 CAN_H/CAN_L(連接 CAN 總線);STM32 的 CAN_TX/CAN_RX(接收發器)。 | |

| 七、控制與中斷 | 復位輸出引腳 | RESET_OUT、RST_OUT | 輸出復位信號,用于復位外部設備(如為下級芯片提供復位信號)。 | LN709(電源監控芯片)的 RESET_OUT 引腳(當 VCC 低于閾值時,輸出低電平復位單片機)。 |

| 中斷請求引腳 | INT、IRQ、INT0/1 | 當芯片內部發生事件(如數據就緒、錯誤)時,輸出電平信號(低 / 高有效)通知外部處理器。 | ADXL345(加速度傳感器)的 INT1 引腳(檢測到運動時輸出低電平中斷);UART 芯片的 RX_INT(接收數據就緒中斷)。 | |

| 使能引腳 | EN、CE、OE(輸出使能) | 控制芯片功能模塊開啟 / 關閉(高電平有效時模塊工作),用于低功耗管理。 | LM1117(LDO)的 EN 引腳(高電平使能輸出 3.3V);射頻模塊(如 CC1101)的 TX_EN(高電平使能發射)。 | |

| 八、調試與配置 | JTAG 調試引腳 | TCK(時鐘)、TMS(模式選擇)、TDI(數據入)、TDO(數據出) | 用于芯片程序下載、在線調試、邊界掃描測試(生產測試)。 | STM32 的 JTAG 接口(TCK/TMS/TDI/TDO,通過調試器下載程序);FPGA 的 JTAG 引腳(配置芯片邏輯)。 |

| 啟動模式選擇引腳 | BOOT0、BOOT1、MODE | 通過外部電平組合設置芯片啟動方式(如從 Flash/ROM/SRAM 啟動)。 | STM32 的 BOOT0 引腳(高電平時從系統存儲器啟動,用于程序升級);51 單片機的 EA(接高電平從內部 ROM 啟動)。 | |

| 九、特殊功能 | 基準電壓引腳 | VREF、VREF_OUT、REF | 提供高精度、高穩定度參考電壓(如 2.048V/4.096V),作為 ADC/DAC 的轉換基準。 | REF3025 的 VREF_OUT 引腳(輸出 2.5V 基準電壓給 ADC);STM32 的 VREF+(外部基準輸入,提升 ADC 精度)。 |

| 散熱引腳(熱焊盤) | EPAD、Thermal Pad、HEAT | 芯片底部的大面積金屬焊盤,直接焊接到 PCB 接地平面,增強散熱(尤其是大功率芯片)。 | TPS5430(DC-DC 轉換器)的 EPAD 引腳;STM32H743 的 Thermal Pad(通過 PCB 銅皮導出 CPU 熱量)。 | |

| 射頻天線引腳 | ANT、RF_IN/OUT、TX/RX | 連接天線,收發無線射頻信號(如 2.4G、藍牙、WiFi)。 | AT2401(2.4G 無線模塊)的 ANT 引腳(接 PCB 天線);ESP8266 的 RF_IN/OUT(接外置天線)。 |

關鍵說明:

標識變體:同一功能可能有多種標識(如 “地” 可標識為 GND、VSS、DGND),需結合芯片數據手冊確認(例如 VSS 在 CMOS 芯片中通常為地,在部分芯片中可能表示負電源)。

引腳復用:多數 MCU/FPGA 的 GPIO 引腳可復用為專用功能(如 STM32 的 PA2 可復用為 UART_TX),需通過寄存器配置。

電平有效性:控制引腳(如 RESET、CS)可能為 “低電平有效”(標識加 “#”,如 CS#),需注意外部電路設計(如通過上拉電阻默認無效)。

實際使用時,務必參考具體芯片的數據手冊(Datasheet)中的 “引腳定義表(Pinout)”,以確保電路連接正確。

審核編輯 黃宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片

+關注

關注

463文章

54007瀏覽量

465946 -

引腳

+關注

關注

16文章

2111瀏覽量

55682

發布評論請先 登錄

相關推薦

熱點推薦

NXP MC33889系統基礎芯片:功能特性與應用解析

NXP MC33889系統基礎芯片:功能特性與應用解析 引言 在汽車電子系統設計中,系統基礎芯片(SBC)扮演著至關重要的角色,它能夠集成多種功能,為微控制器(MCU)系統提供高效、可靠的電源管理

貼片電阻的標法與誤差解析

貼片電阻作為電子電路的核心元件,其表面微小的標識和復雜的參數體系常讓工程師感到困惑。本文將從 標法規則 和 誤差特性 兩個維度,系統解析貼片電阻的標識方法與誤差分類,為電路設計提供實用參考。 一

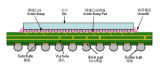

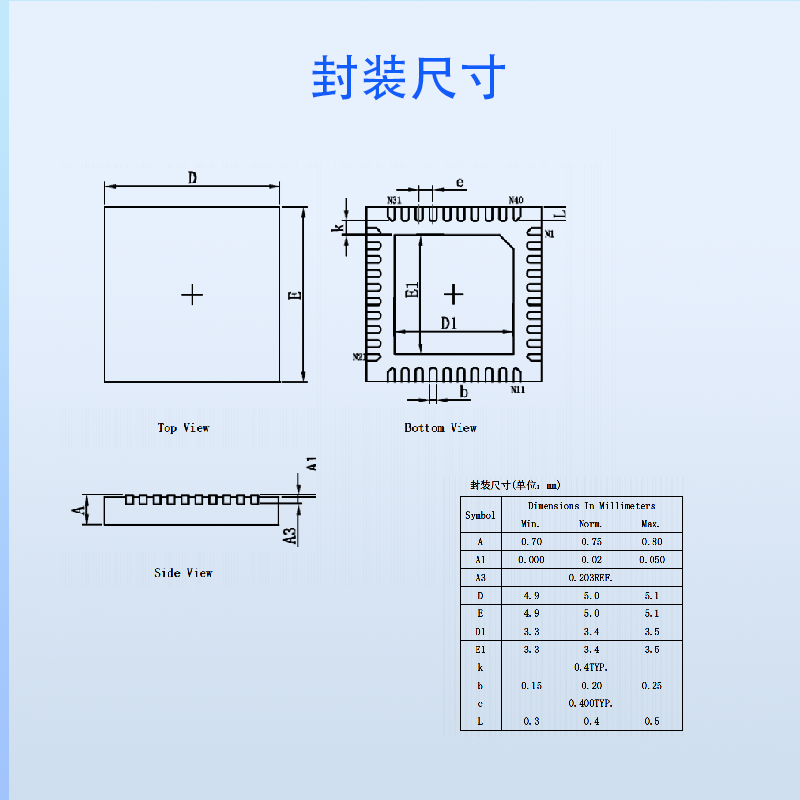

解析LGA與BGA芯片封裝技術的區別

在當今電子設備追求輕薄短小的趨勢下,芯片封裝技術的重要性日益凸顯。作為兩種主流的封裝方式,LGA和BGA各有特點,而新興的激光錫球焊接技術正在為封裝工藝帶來革命性的變化。本文將深入解析LGA與BGA的區別,并探討激光錫球焊接技術如何提升

國巨貼片電容的電壓標識有哪些常見錯誤?

國巨貼片電容的電壓標識在識別和使用過程中可能存在一些常見錯誤,這些錯誤可能源于標識本身的模糊性、不同系列產品的差異、對標識規則的誤解,或使用環境的影響。以下是具體分析: 一、標識模糊或

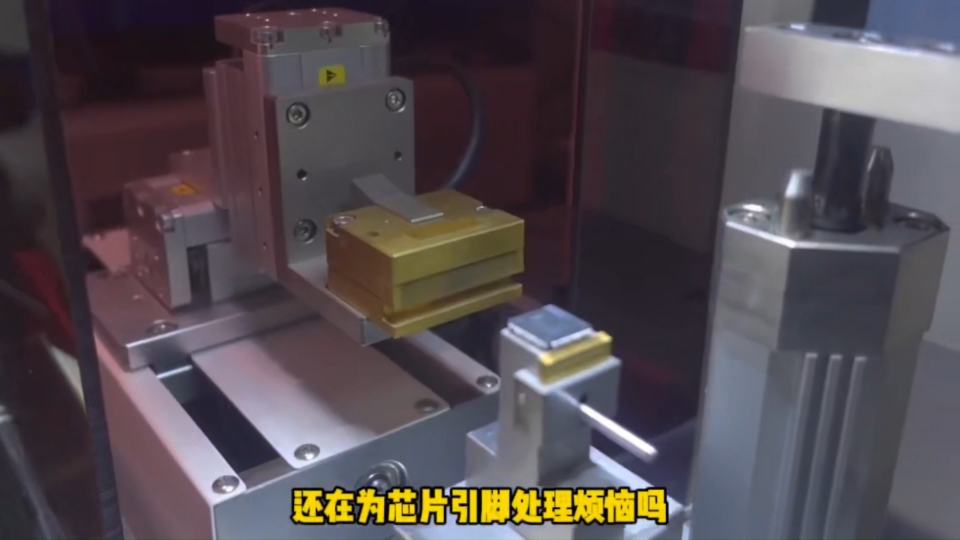

芯片引腳成型設備與芯片引腳整形設備的區別

在電子制造領域,芯片引腳成型設備和芯片引腳整形設備是兩種重要的工具,它們在功能和應用場景上存在顯著區別。了解這些區別有助于企業選擇合適的設備,提高生產效率和產品質量。

發表于 07-19 11:07

AT6850芯片技術解析

? ? ? ?AT6850作為一款高度集成的SOC單芯片,通過融合射頻前端、數字基帶及電源管理模塊,實現了從天線輸入到位置輸出的全鏈路信號處理。其多模衛星信號處理引擎可同時解析北斗二號/三號(B1I

TMS熱收縮標識套管規格含義

TMS熱收縮標識套管是一種專門針對電纜電線標識設計的熱縮套管,選用阻燃性聚烯烴材料制作而成,具有柔軟和薄壁管的特性。這種套管有利直接在標簽印字機上打印,打印效果持久清晰。TMS熱收縮標識套管的收縮

發表于 05-14 09:44

國巨電阻的標識解讀

國巨電阻的標識體系科學嚴謹,通過特定代碼組合可快速解析阻值、精度、封裝等關鍵參數。以下從標識結構、阻值表示、精度與封裝說明三方面進行詳細解讀: 一、標識結構

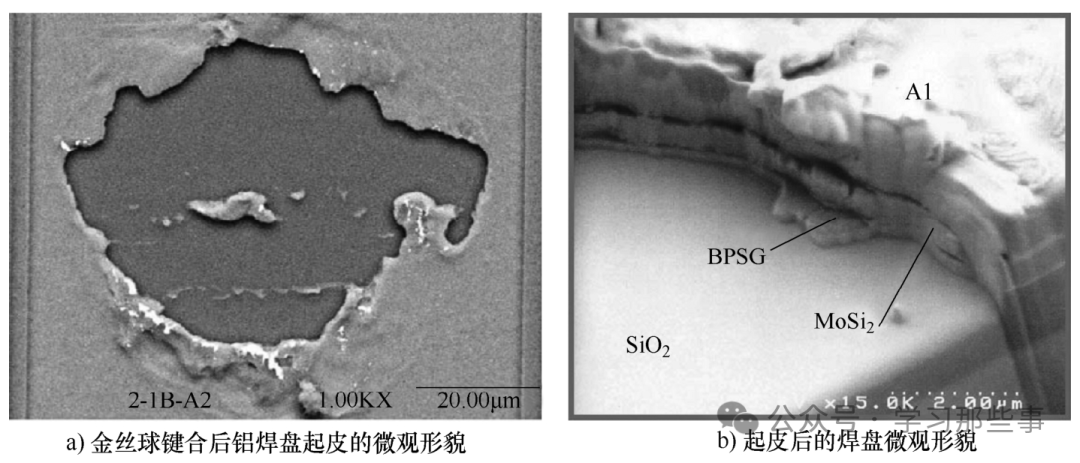

芯片焊盤起皮的成因解析

本文深入解析了焊盤起皮的成因、機制及其與工藝參數之間的關系,結合微觀形貌圖和仿真分析,系統探討了劈刀狀態、超聲參數、滑移行為等關鍵因素的影響,并提出了優化建議,為提高芯片封裝質量和可靠性提供了重要參考。

貼片電容“103”標識的電容量解析

在電子元件領域,貼片電容憑借其小型化、高精度特性廣泛應用于各類電路中。其表面常標注的“103”等數字編碼,實則為電容容量的簡化標識方法。通過特定規則換算,可準確解讀其實際電容量。 編碼規則解析 貼片

芯知識|WT588系列語音芯片BUSY引腳功能解析與設計指南

引腳的設計處理直接影響著系統交互的可靠性和功能拓展性。本文將從電路原理、應用場景、設計策略三個維度,深入解析BUSY引腳的技術特性及其工程實踐要點。一、BUSY引腳

芯片引腳標識和應用解析

芯片引腳標識和應用解析

評論