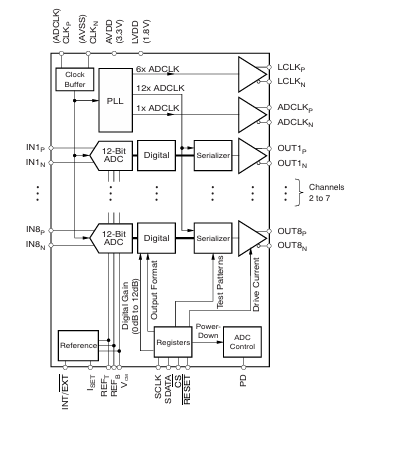

采用CMOS工藝技術和創新電路技術,ADS5292為低 功率80MSPS 8通道ADC。低功耗、高信噪比、低SFR和穩定過載 恢復允許用戶設計高性能系統。

ADS5292擁有一個數字處理模塊,集成了多種常用的數字處理模塊 用于提升系統性能的功能。它內置了一個數字濾波模塊 消極濾波器(具有低通、高通和帶通特性)。削減率為 也可以編程(按2、按4或按8)。這使得它在窄帶應用中非常有用,其中 濾波器可以方便地用于提升信噪比和敲擊諧波,同時 降低輸出數據率。該設備包含一個平均模式,可實現兩個通道(甚至兩個通道) 四個信道)可以被平均以提升信噪比。

*附件:ads5292.pdf

串行LVDS輸出減少接口線數,并支持最高系統 集成。每個通道ADC的數字數據可以通過一根或兩根LVDS線輸出 輸出線路取決于ADC采樣率。這種兩線接口有助于保存串行數據 低速率,使得即使在高采樣率下也能使用低成本的FPGA接收器。一個獨特的 功能是可編程映射模塊,允許輸入通道間靈活映射 以及LVDS輸出引腳。這大大減少了LVDS輸出路由的復雜性,并且可以 通過減少PCB層數,可能導致系統板更便宜。

該設備集成了一個內部的參考,經過修剪以精確匹配各設備。 最佳性能預計通過內部參考模式實現。該裝置可以是 也有外部推薦的驅動力。

該設備提供12毫米×12毫米80針QFP版本。其工作溫度范圍為–40°C至85°C。ADS5292完全是針腳對針的,寄存器與ADS5294兼容。

特性

- 最大采樣率:80 MSPS/12位

- 高信噪比

- 70 dBFS 信噪比,頻率為 5 MHz/80 MSPS

- 在5 MHz/80 MSPS和十倍振制濾波器 = 2時,信噪比為71.5 dBFS

- 85 dBc SFDR,頻率為5 MHz/80 MSPS

- 低功耗

- 48 mW/CH,50 MSPS

- 54毫瓦/CH,65 MSPS

- 66 mW/CH,80 MSPS(每信道2根LVDS線)

- 數字處理模塊

- 可編程FIR消減濾波器及過采樣以最小化

諧波干擾 - 可編程IIR高通濾波器以最小化直流偏移

- 可編程數字增益:0 dB 至 12 dB

- 2-或4-=通道平均

- 可編程FIR消減濾波器及過采樣以最小化

- 靈活串行LVDS輸出:

- 每個通道有一根或兩根LVDS輸出線,具體取決于ADC

采樣率 - ADC輸入通道與LVDS輸出

引腳之間的可編程映射簡化了電路板設計 - 驗證

FPGA/接收器數據捕獲的多種測試模式

- 每個通道有一根或兩根LVDS輸出線,具體取決于ADC

- 內部與外部參考

- 1.8伏低功耗工作

- 低頻噪聲抑制

- 在1個時鐘周期內從6 dB超載中恢復

- 封裝:12毫米×12毫米80針QFP

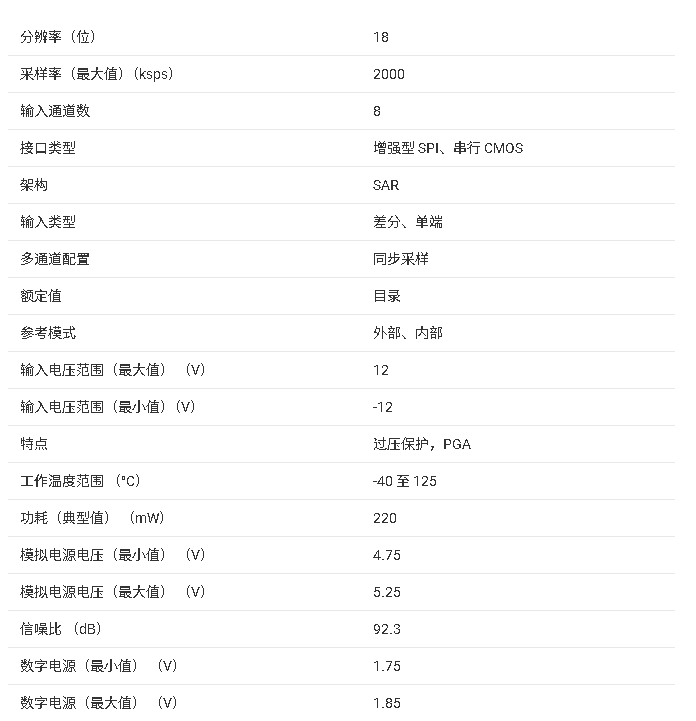

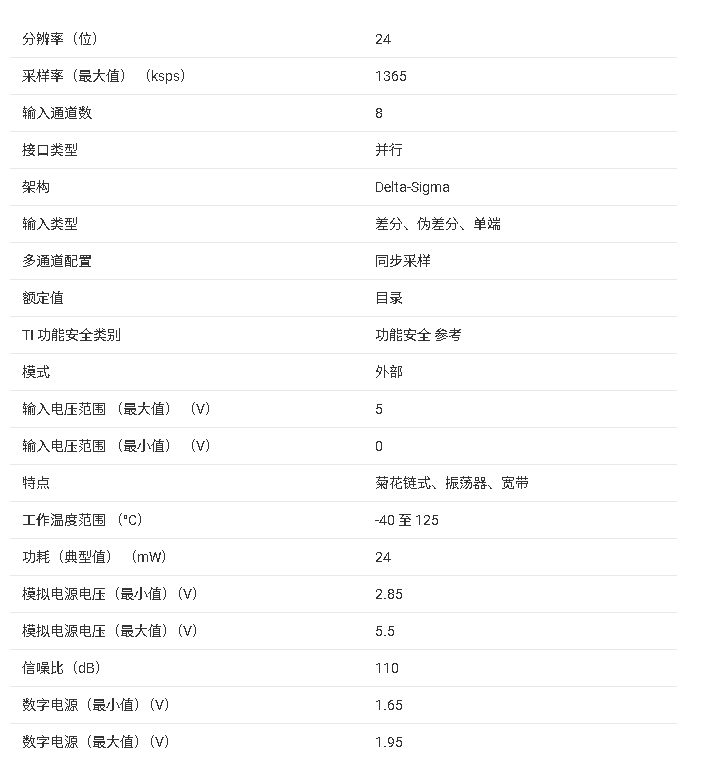

參數

ADS5292 是德州儀器(TI)推出的低功耗八通道 12 位高速模數轉換器(ADC),最高采樣率達 80 MSPS,集成豐富數字處理功能,適配超聲成像、多通道數據采集、通信設備等場景,以高動態性能、靈活輸出接口和低功耗為核心優勢。

一、芯片基礎信息與核心特性

1. 基礎規格

- 文檔與型號 :文檔編號 SLAS788B,2011 年 11 月發布、2012 年 7 月修訂,與 ADS5294 引腳和寄存器完全兼容。

- 供電與溫度 :模擬電源(AVDD)和數字電源(LVDD)均為 1.7V-1.9V(典型 1.8V);工作溫度 - 40°C 至 85°C,存儲溫度 - 55°C 至 150°C。

- 封裝形式 :12mm×12mm 80 引腳 QFP 封裝(帶熱焊盤),結到環境熱阻 30.8°C/W,熱焊盤需焊接至 PCB 接地平面以保障散熱。

2. 核心性能指標

- 動態性能 :80 MSPS 采樣率下,5 MHz 輸入信號的 SNR 典型值 70 dBFS,SFDR 達 85 dBc,THD 低至 81.5 dBc;開啟 2 倍抽取濾波后 SNR 提升至 71.5 dBFS,IMD3 典型值 82 dBc。

- 精度指標 :DNL±0.8 LSB,INL±1 LSB,無失碼;通道間串擾低至 85 dB(近通道)、90 dB(遠通道),6 dB 過載恢復時間僅 1 個時鐘周期。

- 輸入特性 :差分輸入范圍 2 Vpp,共模電壓 0.95V±0.05V;模擬輸入帶寬 550 MHz,支持高頻信號欠采樣;輸入電阻 2 kΩ,輸入電容 2.2 pF。

- 功耗優化 :50 MSPS 時每通道功耗 48 mW,80 MSPS(2 線 LVDS 模式)時每通道 66 mW;支持完全掉電(功耗 50 mW)和部分掉電(功耗 175 mW)模式,喚醒時間分別為 100 μs 和 5 μs。

二、關鍵功能模塊與工作原理

1. 核心功能模塊

- 多通道架構 :集成 8 個獨立 12 位 ADC 通道,支持同步采樣,通道間孔徑延遲偏差 ±175 ps,確保多通道一致性。

- 數字處理模塊 :

- 可編程抽取濾波器:支持 2/4/8 倍抽取,內置低通 / 高通 / 帶通濾波器,可加載自定義系數,降低輸出數據率并提升信噪比。

- 數字增益控制:每通道獨立配置 0 dB-12 dB 增益,適配小信號輸入場景。

- 通道平均功能:支持 2/4 通道數據平均,進一步優化 SNR。

- 高通 IIR 濾波器:可編程截止頻率,抑制 DC 偏移和低頻噪聲。

- 輸出接口 :支持 LVDS 1 線 / 2 線輸出模式,1 線模式最高數據率 960 Mbps,2 線模式 480 Mbps;支持通道與輸出引腳可編程映射,簡化 PCB 布線。

- 輔助功能 :內置多種測試模式(斜坡、PRBS、自定義固定碼等),支持外部 / 內部參考電壓切換,外部參考可通過 REFT/REFB 引腳或 VCM 引腳接入。

2. 工作原理

- 模擬信號經 8 個通道同步采樣后,進入數字處理模塊,可選擇抽取濾波、增益調整、通道平均等處理;處理后的數據通過 LVDS 接口序列化輸出,支持 12 位 / 14 位 / 16 位輸出分辨率切換。

- 采樣時鐘支持單端(CMOS)或差分(LVPECL/LVDS)輸入,采樣觸發沿為時鐘上升沿,數據 latency 為 11 個時鐘周期(1 線模式)或 15 個時鐘周期(2 線模式)。

三、應用場景與設計建議

1. 典型應用

- 超聲成像 :多通道同步采樣適配超聲探頭,低噪聲和高頻帶寬滿足成像分辨率需求。

- 通信設備 :支持中頻信號欠采樣,數字濾波功能簡化射頻前端設計。

- 多通道數據采集 :8 通道同步特性適配工業檢測、醫療設備等多信號采集場景。

2. 設計注意事項

- 電源與接地 :模擬地與數字地共地,各電源引腳就近并聯 0.1 μF 去耦電容;熱焊盤需通過過孔連接至 PCB 接地平面,保障散熱。

- 時鐘設計 :推薦使用低抖動差分時鐘(輸入幅度 0.2 Vpp-1.6 Vpp),時鐘占空比 35%-65%;高頻場景(>30 MHz)優先采用差分時鐘以提升 SNR。

- 輸入匹配 :模擬輸入建議串聯 5 Ω-15 Ω 電阻抑制寄生振蕩,輸入信號需差分驅動以提升抗干擾能力和偶數次諧波抑制。

- ESD 防護 :芯片 ESD 額定值為人體放電模型(HBM)2000 V、帶電器件模型(CDM)500 V,操作和存儲時需采取防靜電措施。

四、關鍵配置與操作要點

1. 核心功能配置

- 數字處理配置 :通過寄存器選擇抽取率(2/4/8)、濾波器類型(低通 / 高通 / 帶通)、通道平均模式(2/4 通道);每通道獨立開啟低中頻噪聲抑制(LFNS)和高通濾波器。

- 接口配置 :選擇 LVDS 1 線 / 2 線模式,配置數據格式(2 補碼 / 偏移二進制)、位序(MSB/LSB 優先);通過映射寄存器自定義輸入通道與輸出引腳的對應關系。

- 電源管理 :支持全局掉電、部分掉電和單通道掉電,PDN 引腳可配置為部分 / 完全掉電控制端,適配不同功耗需求場景。

2. 典型操作流程

- 上電序列 :同時為 AVDD 和 LVDD 供電,通過 RESET 引腳輸入≥50 ns 高脈沖復位芯片,默認進入 12 位、1 線 LVDS 輸出模式。

- SPI 配置 :通過 SPI 接口(CSZ/SCLK/SDATA)讀寫寄存器,配置數字處理功能和接口參數;SPI 支持 24 位傳輸格式(8 位地址 + 16 位數據),最高時鐘頻率 15 MHz。

- 同步操作 :SYNC 引腳可同步多芯片或多通道的濾波和測試模式,確保數據輸出時序一致性。

-

濾波器

+關注

關注

162文章

8412瀏覽量

185728 -

adc

+關注

關注

100文章

7511瀏覽量

556007 -

可編程

+關注

關注

2文章

1325瀏覽量

41490 -

數字處理

+關注

關注

0文章

30瀏覽量

15144

發布評論請先 登錄

MAX1436B 八通道、12位模數轉換器(ADC)

DACx0508八通道16/14/12位SPI電壓輸出DAC數據表

?ADS9813 18位 2MSPS 8通道同步采樣ADC技術文檔總結

深度解析ADS5281:高性能八通道ADC的卓越之選

ADS5292 八通道 12 位高速 ADC 技術文檔總結

ADS5292 八通道 12 位高速 ADC 技術文檔總結

評論