該ADC08DL502是一款雙通道、低功耗、高性能CMOS模數(shù)轉(zhuǎn)換器。 該ADC08DL502以高達(dá) 500 MSPS 的采樣率將信號數(shù)字化至 8 位分辨率。消費 該器件在 1.2 V 單電源的解復(fù)用模式下以 500 MSPS 的典型功率為 1.9 W,因此 確保在整個工作溫度范圍內(nèi)沒有缺失代碼。獨特的折疊和 插補(bǔ)架構(gòu)、全差分比較器設(shè)計、創(chuàng)新設(shè)計 內(nèi)部采樣保持放大器和校準(zhǔn)方案可實現(xiàn)所有 超出奈奎斯特的動態(tài)參數(shù),產(chǎn)生 7.5 的有效位數(shù) (ENOB),125 MHz 輸入信號和 500 MHz 采樣率,同時提供 10^?18^法典 錯誤率 (CER)

*附件:adc08dl502.pdf

該轉(zhuǎn)換器在掉電模式下通常消耗 3.3 mW,并提供 無鉛 144 引腳 LQFP,可在改進(jìn)的工業(yè) (-40°C ≤ T 一個 ≤ +70°C)溫度范圍。

特性

- 單路+1.9V ±0.1V工作電壓

- 占空比校正采樣時鐘

主要技術(shù)參數(shù)

- 分辨率:8位

- 最大轉(zhuǎn)換率:500 MSPS

- 代碼錯誤率:10 ^?18^ (典型值)

- ENOB @ 125 MHz 輸入:7.5 位(典型值)

- DNL:±0.15 LSB(典型值)

- 功耗

- 在 1:2 解復(fù)用器輸出下運行:1.25W(典型值)

- 掉電模式:3.3 mW(典型值)

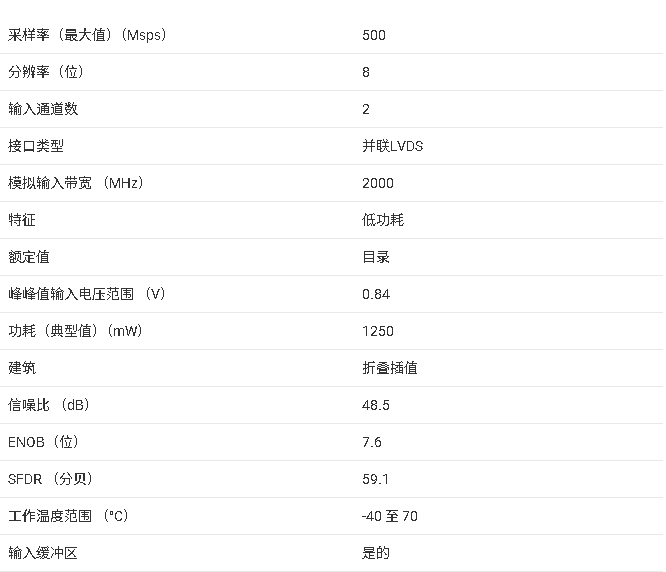

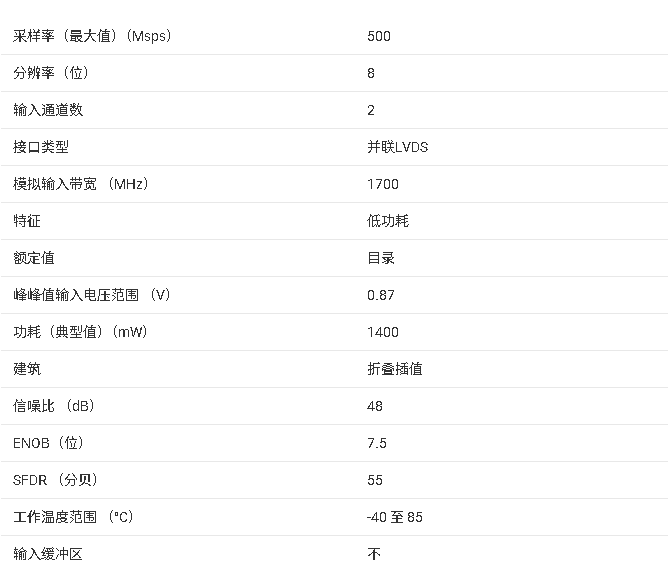

參數(shù)

方框圖

一、產(chǎn)品概述

ADC08DL502 是德州儀器(TI)推出的高速、低功耗雙路模數(shù)轉(zhuǎn)換器(ADC),核心優(yōu)勢為 500 MSPS 超高采樣率、雙路同步采樣與優(yōu)異的動態(tài)性能,專為衛(wèi)星調(diào)制解調(diào)器、數(shù)字示波器、直接射頻下變頻通信系統(tǒng)、測試儀器等高速信號采集場景設(shè)計。器件采用 8 位分辨率折疊插值架構(gòu),集成校準(zhǔn)功能與 LVDS 輸出接口,文檔版本為 SNAS582B,發(fā)布于 2012 年 3 月,2013 年 3 月修訂,采用 144 引腳 LQFP 封裝,工作溫度范圍 - 40°C 至 70°C。

二、核心參數(shù)與性能特性

1. 基礎(chǔ)規(guī)格

- ADC 性能 :8 位分辨率,無丟失碼;INL±0.3 LSB(典型)、±0.9 LSB(最大),DNL±0.15 LSB(典型)、±0.75 LSB(最大);零偏誤差 - 0.45 LSB(典型),滿量程誤差 ±25 mV(最大);碼錯誤率(C.E.R.)典型值 10?1?。

- 動態(tài)性能 :125 MHz 輸入時 ENOB 達(dá) 7.5 位、SNR 47.8 dB、SFDR 58.5 dB;248 MHz 輸入時 ENOB 7.6 位、SNR 48.5 dB、SFDR 59.1 dB;全功率帶寬 2 GHz,增益平坦度 ±0.8 dB(直流至 248 MHz);三階互調(diào)失真(IMD3)71.4 dBFS,總諧波失真(THD)-54.2 dB。

- 接口特性 :雙路差分模擬輸入(VINI±、VINQ±),支持交流 / 直流耦合;32 路 LVDS 數(shù)據(jù)輸出(4 組 8 位總線),輸出格式為偏移二進(jìn)制;支持 1:2 解復(fù)用模式(降低輸出數(shù)據(jù)率)與 DDR/SDR 時鐘模式;串行接口(SCLK/SDATA/SCS)用于擴(kuò)展控制模式。

2. 供電與功耗

- 供電范圍 :模擬電源(VA)與數(shù)字驅(qū)動電源(VDR)均為 1.8 V-2.0 V,標(biāo)稱 1.9 V 單電源供電。

- 功耗表現(xiàn) :1:2 解復(fù)用模式下典型功耗 1.25 W,掉電模式僅 3.3 mW;模擬電源電流典型值 494 mA,數(shù)字驅(qū)動電源電流典型值 168 mA,適配高速低功耗場景。

3. 封裝與環(huán)境適應(yīng)性

- 封裝類型 :144 引腳 LQFP 封裝,結(jié)到環(huán)境熱阻 43.6 °C/W,結(jié)到殼熱阻 12.5 °C/W,封裝尺寸適配中等規(guī)模 PCB 布局。

- 可靠性 :ESD 防護(hù)(HBM 2500 V、MM 250 V、CDM 1000 V);存儲溫度范圍 - 65°C 至 150°C,最大結(jié)溫 145°C,滿足工業(yè)級可靠性要求。

4. 關(guān)鍵功能特性

- 高速專用功能 :雙路同步采樣,支持多器件同步(通過 DCLK_RST 信號);內(nèi)置校準(zhǔn)電路,可上電自動校準(zhǔn)或手動觸發(fā)校準(zhǔn),校準(zhǔn)后優(yōu)化 INL、DNL 與增益誤差;輸入時鐘占空比校正(20%-80% 容錯),降低時鐘源要求。

- 系統(tǒng)集成特性 :支持測試模式輸出,便于系統(tǒng)調(diào)試;擴(kuò)展控制模式下可通過寄存器調(diào)整輸入滿量程范圍(560 mVPP-840 mVPP)與通道偏移(±45 mV);Out Of Range(OR)信號指示輸入超量程。

三、工作模式與功能原理

1. 核心架構(gòu)

采用 “差分采樣保持電路→折疊插值 ADC→校準(zhǔn)電路→解復(fù)用器→LVDS 輸出緩沖” 架構(gòu),雙路獨立 ADC 支持同步采樣;內(nèi)置 1.26 V 帶隙基準(zhǔn)源(VBG),提供穩(wěn)定參考;通過校準(zhǔn) trim 輸入差分終端電阻與器件參數(shù),確保高動態(tài)性能。

2. 主要工作模式

| 模式 | 核心配置 | 關(guān)鍵參數(shù) | 適用場景 |

|---|---|---|---|

| 正常采樣模式 | 500 MSPS 采樣率,雙路同步工作 | 1:2 解復(fù)用輸出,數(shù)據(jù)率 250 MSPS / 總線 | 高速雙路信號采集 |

| 非解復(fù)用模式 | 采樣率≤500 MSPS,單路輸出總線 | DDR 模式,數(shù)據(jù)率與采樣率一致 | 高速單路信號采集 |

| 掉電模式 | PD 引腳高電平,器件整體斷電 | 功耗 3.3 mW,輸出高阻 | 低功耗待機(jī)場景 |

| 單通道模式 | PDQ 引腳高電平,僅 “Q” 通道斷電 | “I” 通道正常工作,保留雙路架構(gòu) | 單路信號采集,節(jié)省功耗 |

3. 關(guān)鍵功能細(xì)節(jié)

- 校準(zhǔn)功能 :上電自動校準(zhǔn)或通過 CAL 引腳手動觸發(fā),校準(zhǔn)周期典型值 1.4×10?時鐘周期,校準(zhǔn)期間優(yōu)化線性度與動態(tài)性能;支持電阻微調(diào)禁用(RTD),確保 DCLK 持續(xù)輸出。

- 時鐘與同步 :差分時鐘輸入(CLK±),支持 200 MHz-500 MHz 采樣率;DCLK 輸出用于數(shù)據(jù)鎖存,支持 0°/90° 相位調(diào)整;多器件可通過 DCLK_RST 信號同步,確保多通道一致性。

- 擴(kuò)展控制 :通過串行接口訪問 9 個寄存器,可配置輸入滿量程、通道偏移、采樣時鐘相位、LVDS 輸出幅度等參數(shù),適配復(fù)雜系統(tǒng)需求。

四、應(yīng)用場景與設(shè)計建議

1. 典型應(yīng)用領(lǐng)域

- 衛(wèi)星通信(調(diào)制解調(diào)器)、數(shù)字示波器、射頻下變頻系統(tǒng)、高速數(shù)據(jù)采集卡、測試測量儀器、雷達(dá)信號處理。

2. 設(shè)計關(guān)鍵要點

- 電源設(shè)計 :VA 與 VDR 引腳需分別供電,每路電源就近并聯(lián) 0.1 μF 陶瓷電容與 33 μF 鉭電容濾波;電源間建議串聯(lián)鐵氧體磁珠隔離,避免數(shù)字噪聲耦合至模擬部分。

- 輸入與接地 :模擬輸入采用差分驅(qū)動,交流耦合時 VCMO 引腳接地,直流耦合時輸入共模電壓需匹配 VCMO 輸出(1.26 V 典型值);PCB 采用單點接地平面,模擬區(qū)與數(shù)字區(qū)嚴(yán)格分區(qū),避免高頻噪聲耦合。

- 時鐘設(shè)計 :時鐘輸入需交流耦合,差分阻抗匹配 100 Ω;時鐘源需低抖動(建議 rms 抖動≤0.4 ps),避免動態(tài)性能退化;長距離時鐘線需做阻抗匹配與屏蔽。

- 布線與防護(hù) :LVDS 輸出線采用 100 Ω 差分阻抗匹配,減少反射;模擬輸入線遠(yuǎn)離數(shù)字信號線與時鐘線,避免串?dāng)_;未使用的模擬通道交流耦合時接交流地,直流耦合時接 VCMO。

-

CMOS

+關(guān)注

關(guān)注

58文章

6221瀏覽量

243142 -

MSPS

+關(guān)注

關(guān)注

0文章

574瀏覽量

29011 -

分辨率

+關(guān)注

關(guān)注

2文章

1128瀏覽量

43382 -

單電源

+關(guān)注

關(guān)注

0文章

251瀏覽量

25802 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4054瀏覽量

130204

發(fā)布評論請先 登錄

對信號進(jìn)行濾波,然后再輸入到模數(shù)轉(zhuǎn)換器ADC08DL502,為什么信號存在一個大周期T?

MAX815TESA+ 原廠現(xiàn)貨***

LTC2380IDE-24#PBF 現(xiàn)貨

ADC08DL500的詳細(xì)英文數(shù)據(jù)手冊詳細(xì)概述(免費下載)

ADC08D500 CMOS模數(shù)轉(zhuǎn)換器的資料詳細(xì)概述

THS12082低功耗、12位、8 MSPS模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC08D502雙通道、低功耗、高性能CMOS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADC08DL500雙通道、低功耗、高性能CMOS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADC08L060低功耗、8位、單芯片模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

THS10082低功耗、10位、8 msps模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

DAC3174雙路14位500MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADC08D502 雙路 8 位 500-MSPS 高性能低功耗模數(shù)轉(zhuǎn)換器技術(shù)規(guī)格與應(yīng)用總結(jié)

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D轉(zhuǎn)換器

ADC08DL502 8 位雙路 500 MSPS 低功耗模數(shù)轉(zhuǎn)換器技術(shù)規(guī)格與應(yīng)用總結(jié)

ADC08DL502 8 位雙路 500 MSPS 低功耗模數(shù)轉(zhuǎn)換器技術(shù)規(guī)格與應(yīng)用總結(jié)

評論