碳化硅SiC MOSFET并聯的技術瓶頸與系統性克服策略:基于基本半導體產品力的深度解析

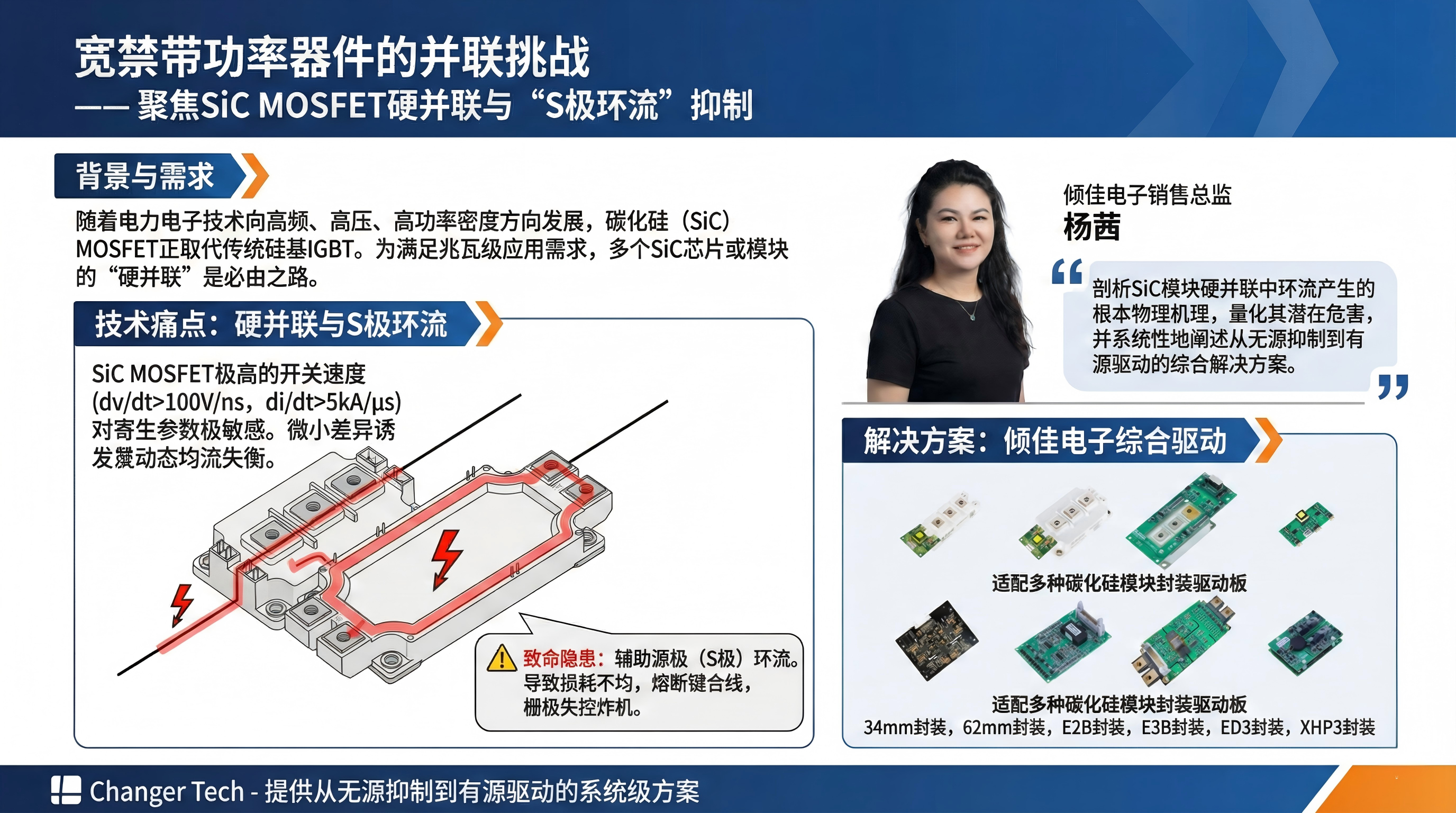

傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半導體器件以及新能源汽車連接器。

?傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

摘要

本文深入探討了碳化硅(SiC)MOSFET在大功率應用中并聯所面臨的四大核心技術挑戰:靜態均流、動態均流(寄生電感)、串擾誤導通(米勒效應)以及系統熱管理。SiC器件的高速開關特性(高dv/dt與di/dt)是導致并聯設計復雜化的根本原因,使其遠超傳統硅基(Si)器件的設計難度。報告論證了SiC并聯是一個必須從芯片物理、器件封裝、電路驅動到系統集成進行多維度協同優化的系統工程。通過對基本半導體(BASIC Semiconductor)的產品組合(包括B3M系列芯片、4引腳TO-247分立器件、Pcore?低電感功率模塊及配套驅動IC)的深度解析,本文展示了其如何通過“芯片-封裝-驅動”一體化的產品力,為實現高可靠性、高功率密度的SiC并聯應用提供系統性解決方案。

第一章:引言:SiC MOSFET并聯——高功率密度的必然與挑戰

1.1 并聯的驅動力:市場需求與物理局限

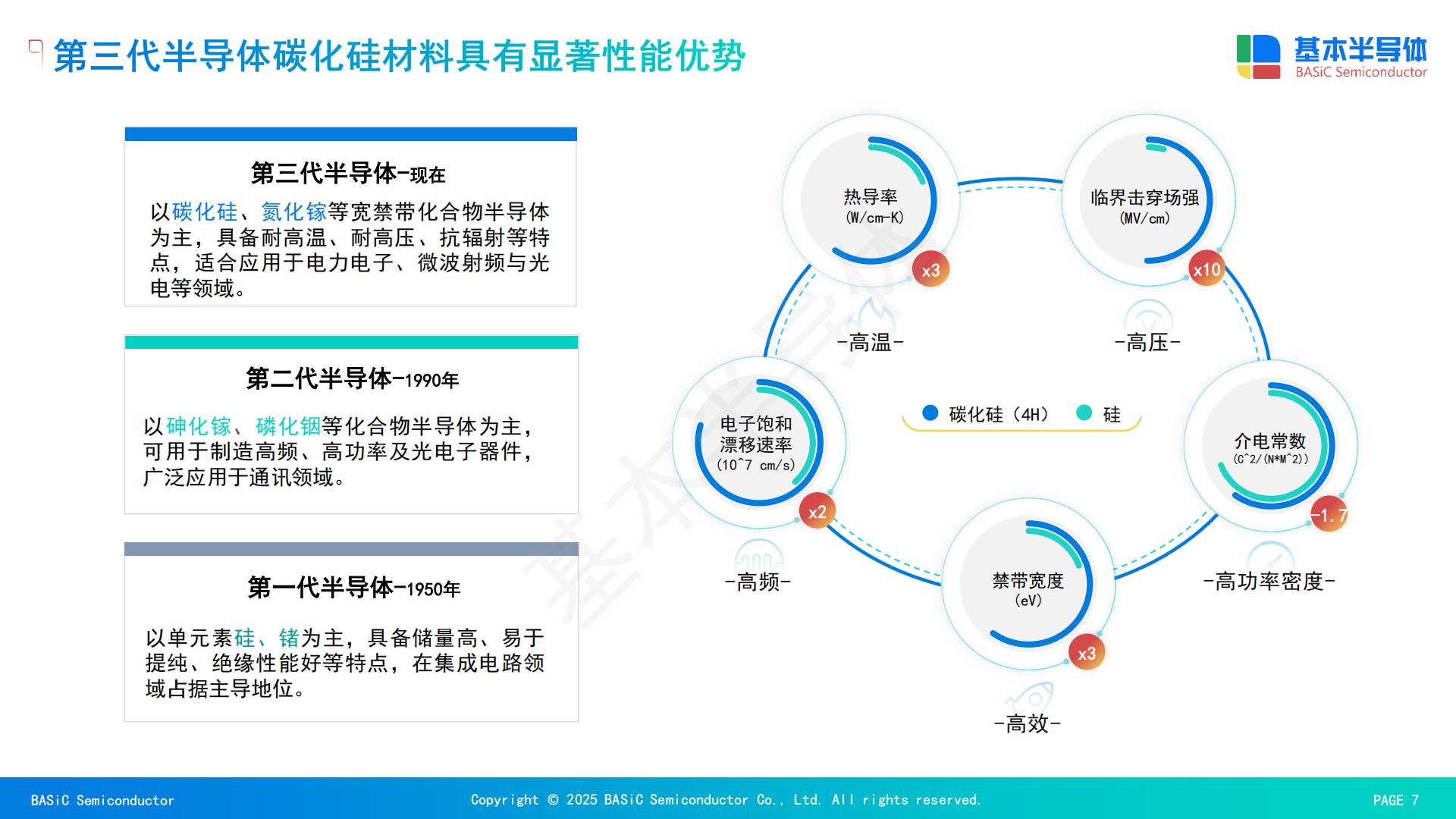

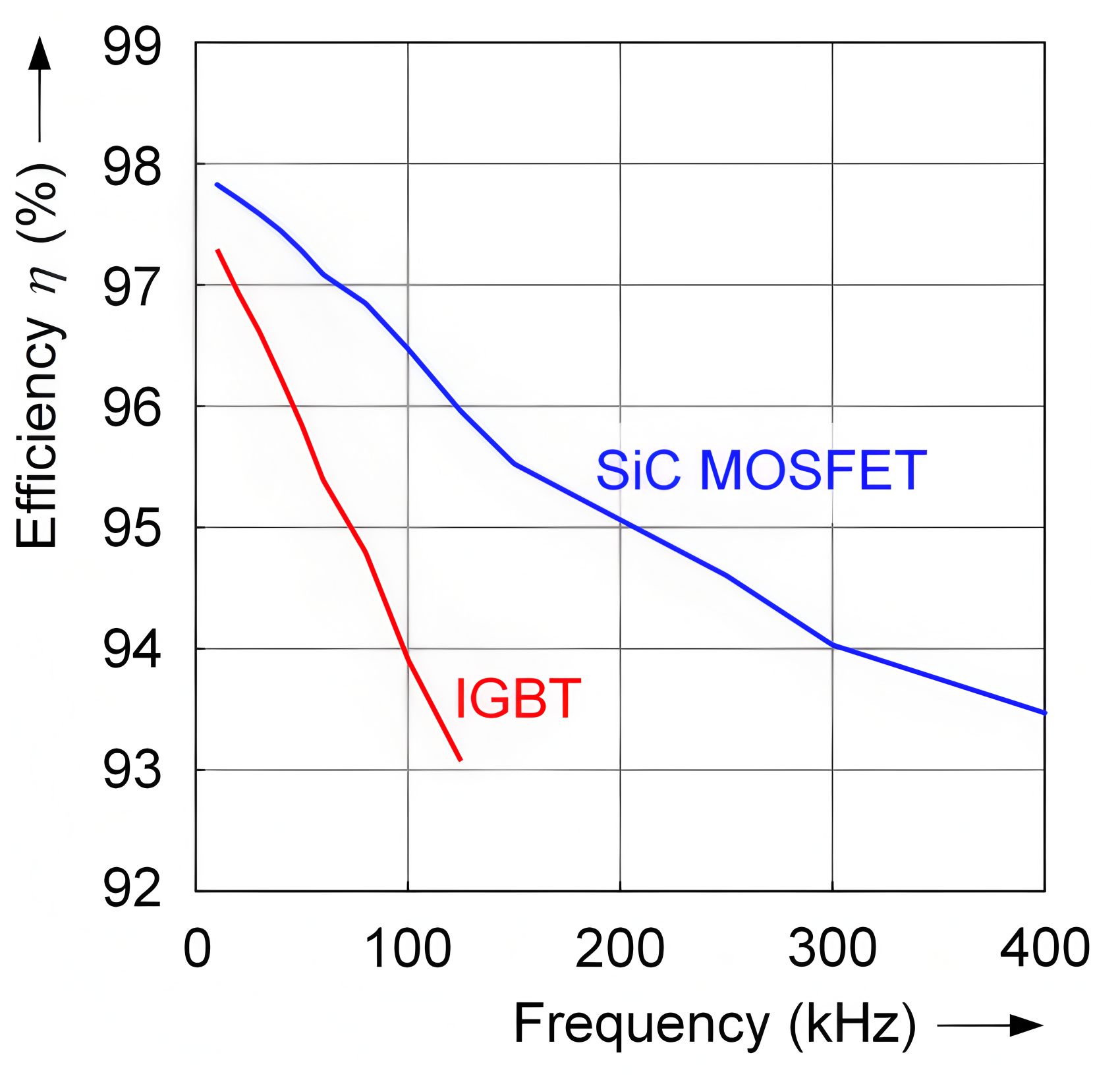

第三代半導體SiC材料憑借其寬禁帶、高臨界擊穿場強和高熱導率的物理優勢,正在重塑電力電子行業 。在新能源汽車(NEV)、光伏儲能和數據中心電源等領域,市場對功率密度和系統效率的需求正呈指數級增長 。特別是新能源汽車主驅逆變器向800V高壓平臺遷移,以及光伏/儲能逆變器(PCS)進入100kW+級別,這對功率器件的電流處理能力提出了前所未有的要求 。

然而,受限于SiC晶錠生長和晶圓制造工藝的成熟度,制造大面積、低缺陷密度的SiC芯片(Die)在經濟和技術上仍具挑戰 。這導致了單個SiC MOSFET Die的額定電流能力(通常在100A量級)遠不能滿足系統動輒數百甚至上千安培的電流需求。

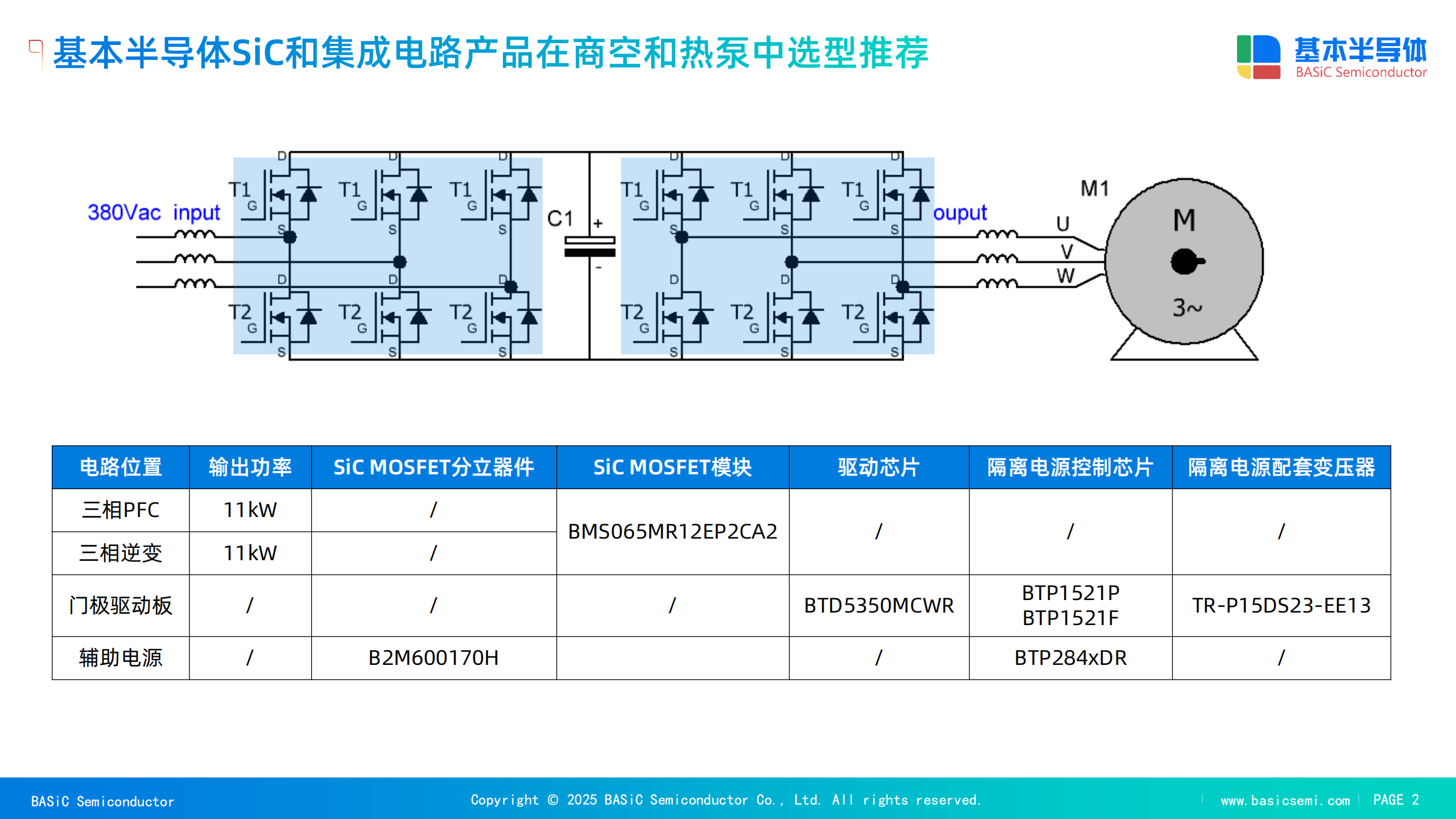

因此,通過多顆SiC MOSFET器件(無論是分立器件還是功率模塊內的裸片)進行并聯,成為實現大電流容量的唯一可行路徑。基本半導體的應用案例明確證實了這一點,例如在其工商業PCS應用中,推薦使用多達4顆分立SiC MOSFET并聯 ;在逆變焊機應用中,也采用了3顆器件并聯的方案 。

1.2 SiC帶來的新挑戰:從“靜態均流”到“動態夢魘”

在傳統的硅基IGBT應用中,并聯相對簡單。IGBT開關速度慢(低di/dt和dv/dt),動態問題(如寄生振蕩、串擾)并不突出,設計者主要關注靜態的均流和散熱。

然而,SiC MOSFET的并聯則極具挑戰。SiC的開關速度比Si快5至10倍 ,其極高的di/dt(> 1 kA/μs)和dv/dt(> 50 V/ns)會與電路中不可避免的寄生參數(納亨級的寄生電感、皮法級的寄生電容)發生劇烈相互作用 。這引發了在Si IGBT時代不曾出現的嚴重動態問題,包括:

寄生振蕩: 寄生電感與器件電容形成LC諧振回路,導致柵極電壓和漏源極電壓產生高頻振蕩,增加損耗并可能導致器件失控 。

串擾誤導通(Crosstalk): 在橋式電路中,一個器件的高dv/dt會通過米勒電容(Crss?)耦合到處于關斷態的互補器件柵極,導致其被錯誤地瞬時導通,引發上下管直通(Shoot-through),這是最危險的失效模式之一 。

成功的SiC MOSFET并聯設計,已不能再依賴傳統“分選配對”的粗放模式。它必須是一個從“芯片物理特性-器件封裝結構-柵極驅動策略-系統熱管理”四位一體的系統性工程。本報告將逐層解構基本半導體的產品力,論證其如何在這四個關鍵層面均提供了針對性的解決方案,從而構成其“并聯友好”的核心競爭力。

第二章:靜態均流挑戰及其參數級解決方案

靜態均流是指在器件完全導通(穩態)時,總電流如何在并聯的各個支路之間實現均勻分配。這主要取決于兩個關鍵的器件參數。

2.1 難點一:導通電阻(RDS(on)?)的正溫度系數(PTC)

機理分析:

并聯支路的總電流(Itotal?)會天然地優先流向導通電阻RDS(on)?最低的支路。如果器件的RDS(on)?具有負溫度系數(NTC),即溫度升高、電阻反而降低,這將觸發一個致命的正反饋:

RDS(on)?最低的器件A承載最大電流。

器件A因大電流而發熱最嚴重,Tj?(結溫)升高。

NTC特性導致其RDS(on)?進一步降低。

器件A吸引更多電流,Tj?繼續飆升,最終導致熱失控(Thermal Runaway)和器件燒毀。

因此,實現靜態均流的首要前提是,器件的RDS(on)?必須具有正溫度系數(PTC)。PTC特性提供了一個天然的“自均流”負反饋機制:承載電流最大的器件發熱最快,其RDS(on)?隨之升高,從而迫使電流流向其他溫度較低、電阻較小的支路,系統自動達到熱電平衡。

基本半導體產品力(PTC特性):

基本半導體的B3M系列SiC MOSFET產品手冊明確證實了其具備強大的PTC特性:

B3M013C120Z (1200V / 13.5mΩ): 在Tj?=25°C時,典型RDS(on)?為13.5 mΩ;當Tj?上升至175°C時,典型RDS(on)?顯著增加至23 mΩ 1。

B3M010C075Z (750V / 10mΩ): 在Tj?=25°C時,典型RDS(on)?為10 mΩ;在Tj?=175°C時,典型RDS(on)?上升至12.5 mΩ 1。

這一特性是實現大規模并聯(如1中48顆器件并聯)的最基本前提。

2.2 難點二:閾值電壓(VGS(th)?)的一致性

機理分析:

VGS(th)?是器件從關斷態進入放大區的臨界點。在并聯應用中,所有器件的柵極通常由同一個驅動信號控制。如果各器件的VGS(th)?參數離散度(偏差)很大,將導致開關動作的“不同步”,進而破壞動態均流:

開通時: VGS(th)?最低的器件將最先導通,并瞬時承載幾乎全部的開通電流。

關斷時: VGS(th)?最高的器件將最后關斷,并瞬時承受全部的關斷應力。

這種不同步會導致開關損耗(Eon? / Eoff?)在并聯器件間嚴重不均,引發局部瞬時過熱和早期失效。

基本半導體產品力(高一致性):

解決VGS(th)?離散度的唯一途徑是在晶圓制造(Fab)階段實現極高的工藝控制水平。

基本半導體在其B3M系列SiC MOSFET的產品介紹中,明確宣稱其具備:“產品一致性更優,VGS(th)? 和 RDS(on)? 偏差非常小,可不進行分選直接進行并聯使用” 。

這是一個極其有力的產品力聲明。它意味著其6英寸碳化硅晶圓制造基地的工藝控制已達到行業領先水平。“可不進行分選”直接為客戶(系統集成商)降低了巨額的測試、分選(Binning)成本和供應鏈管理復雜度。

這一聲明的底氣,也來自于其敢于在應用方案中推薦如4顆分立器件并聯的極端設計 。若無極高一致性作為保障,這種設計在工程上是不可靠且無法實現量產的。

第三章:動態均流挑戰:寄生電感與不對稱布局的抑制

SiC的高速特性(高di/dt)使得電路中納亨(nH)級別的寄生電感成為影響動態均流和系統穩定性的核心障礙。

3.1 難點三:共源電感(Ls?)的負反饋與振蕩

機理分析:

在并聯分立器件(如TO-247)封裝中,驅動回路(Gate-Source)和功率回路(Drain-Source)不可避免地共享一段引腳電感,即共源電感Ls? 7。在SiC的高速開關(高di/dt)期間,這段Ls?上會產生一個反向感應電壓:

VLs?=?Ls??(diD?/dt)

這個VLs?會直接從外部驅動電壓VGG?中扣除,導致器件芯片實際感受到的內部柵源電壓 VGS(internal)?=VGG??VLs? 。

這會產生三個嚴重后果:

開關降速與損耗增加: di/dt越高,負反饋越強,di/dt被抑制,導致開關速度減慢,開關損耗(Eon?, Eoff?)增加。

動態不均: 在不對稱的PCB布局中 5,并聯支路間的Ls?必然不同。Ls?最小的支路開關最快,將承受最大的瞬時di/dt和電流應力,導致嚴重的動態電流不均。

柵極振蕩: Ls?會與器件的輸入電容(Ciss?)形成LC諧振回路,引發柵極高頻振蕩,可能導致器件失控或損壞 。

3.2 解決方案(分立器件):開爾文源極(Kelvin Source)封裝

原理:

為徹底消除Ls?的負反饋,行業引入了4引腳封裝(如TO-247-4)。該封裝增加了一個專用的“開爾文源極”(Kelvin Source)引腳。該引腳僅用于連接驅動芯片的參考地,構成驅動回路;而功率電流則通過原有的“功率源極”(Power Source)引腳回流 。

效果:

驅動回路與功率回路被完全解耦。di/dt產生的感應電壓VLs?只存在于功率回路中,不再影響柵極驅動回路。VGS(internal)?得以保持穩定,從而實現更快的開關速度、更低的開關損耗和更穩定的并聯運行。

基本半導體產品力(4-Pin封裝):

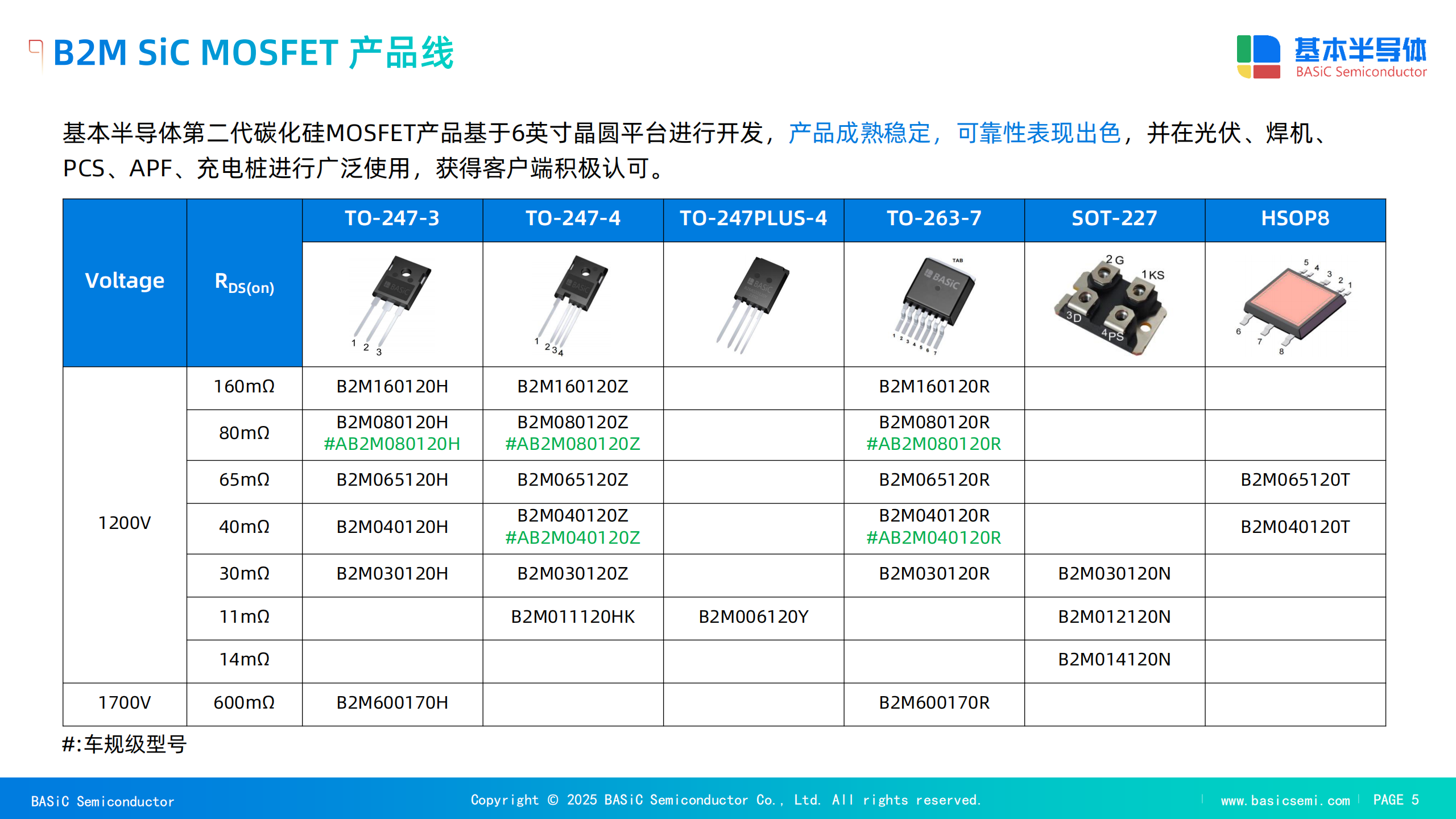

基本半導體深刻理解開爾文源極對SiC應用的重要性,其分立器件產品線廣泛采用了具有開爾文源極的多引腳封裝:

產品系列覆蓋TO-247-4、TO-263-7、T2PAK-7、TOLT、TOLL等 。

其B3M系列的主力產品,如B3M013C120Z 1 和 B3M010C075Z ,均采用TO-247-4封裝,并明確定義Pin 3為“Kelvin Source”。

3.3 解決方案(功率模塊):低雜散電感(Ls?)與對稱化設計

機理分析:

在功率模塊內部,并聯的是裸片(Die)。此時的Ls?主要由封裝內部的雜散電感(如綁定線、DBC/AMB布線、功率端子)決定。不對稱的內部布局(asymmetrical layout)是導致模塊內并聯芯片間均流性能惡化的主因 5。

解決方案:

采用先進封裝技術(如銀燒結、Clip Bond)和優化的端子設計,極力降低總雜散電感。 2. 內部芯片布局和布線追求高度對稱化 8。

基本半導體產品力(先進模塊封裝):

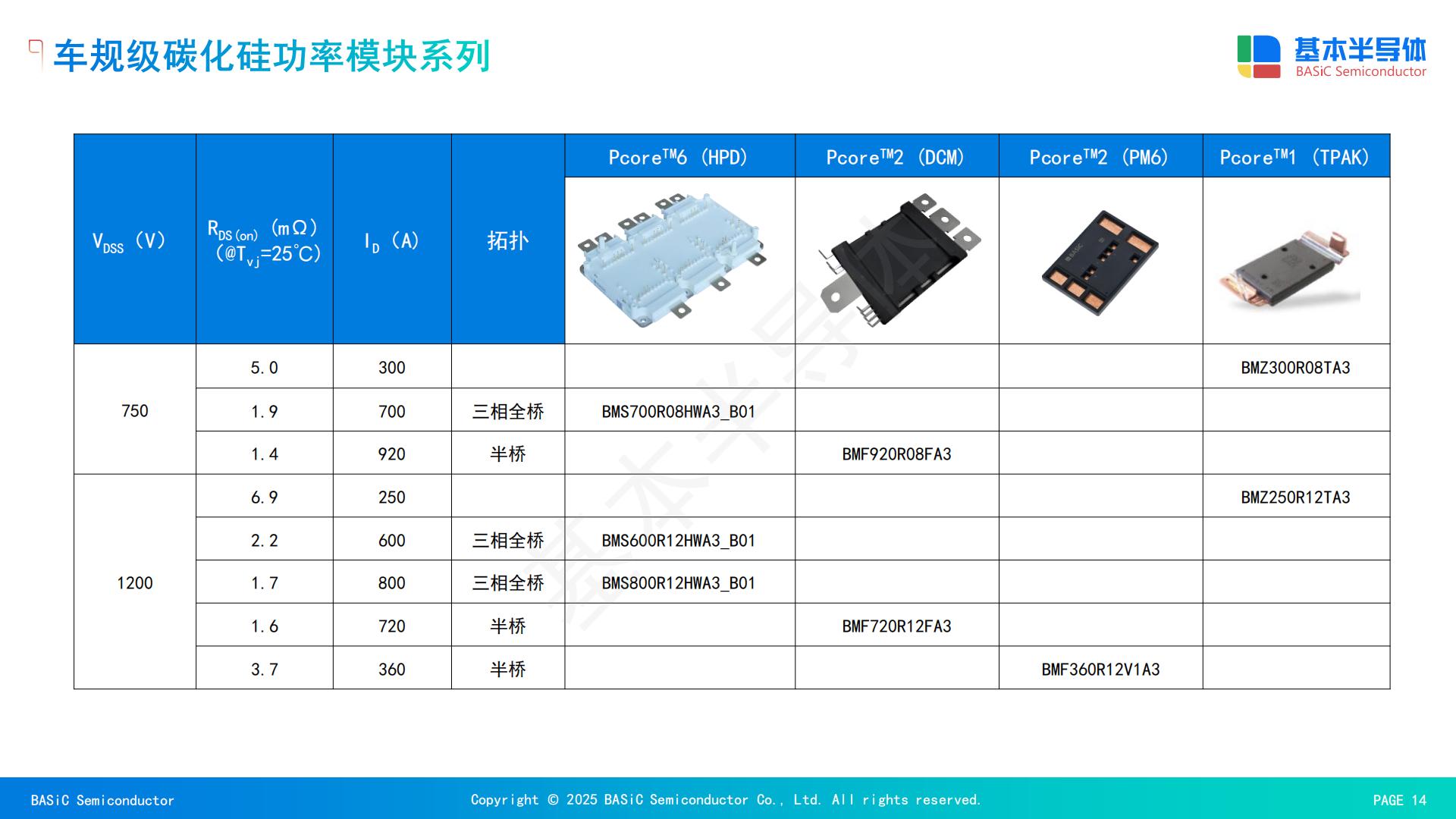

基本半導體在車規級和工業級模塊上均展示了其在低電感封裝方面的強大實力:

車規級PcoreM6 (HPD) 模塊: 采用銀燒結工藝和PinFin散熱基板,實現了 Ls?<8.5 nH 的優異性能 。

車規級Pcore 2 (DCM) 模塊: 采用DTS+TCB和Sintering技術,更是達到了 Ls?<5.5 nH 的行業頂尖水平 。

工業級Pcore?2 62mm模塊: 同樣實現了“低雜散電感設計,14nH及以下” 。

這些5.5 nH至14 nH的雜散電感值,遠低于傳統Si IGBT模塊(通常> 30 nH),極大抑制了di/dt引起的電壓過沖和振蕩,是實現模塊內部多芯片并聯穩定均流的物理基礎。

第四章:關鍵失效模式:串擾(Crosstalk)與誤導通的系統性防范

在所有并聯挑戰中,由高dv/dt引發的串擾誤導通是最為危險的瞬態失效模式。

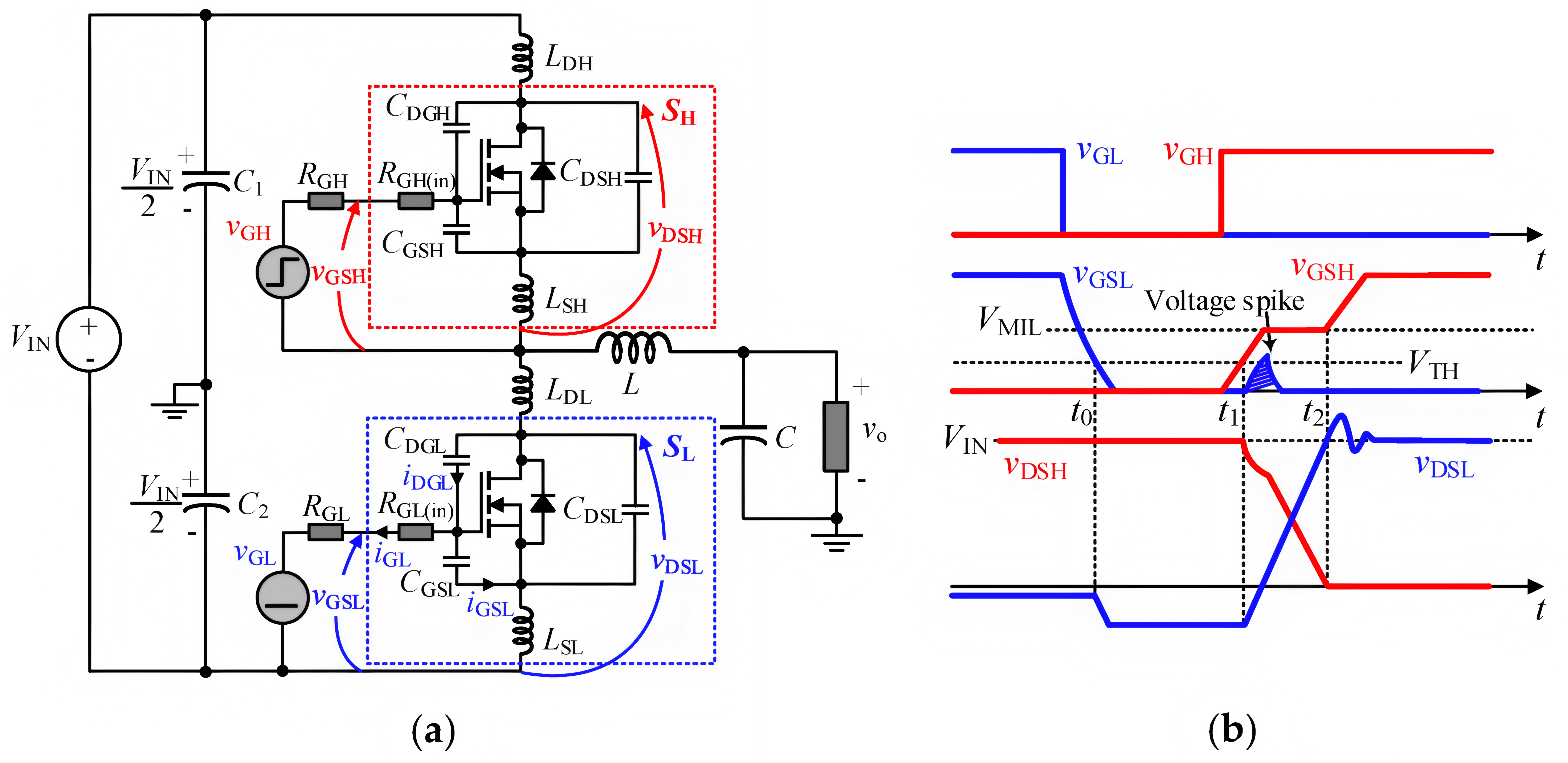

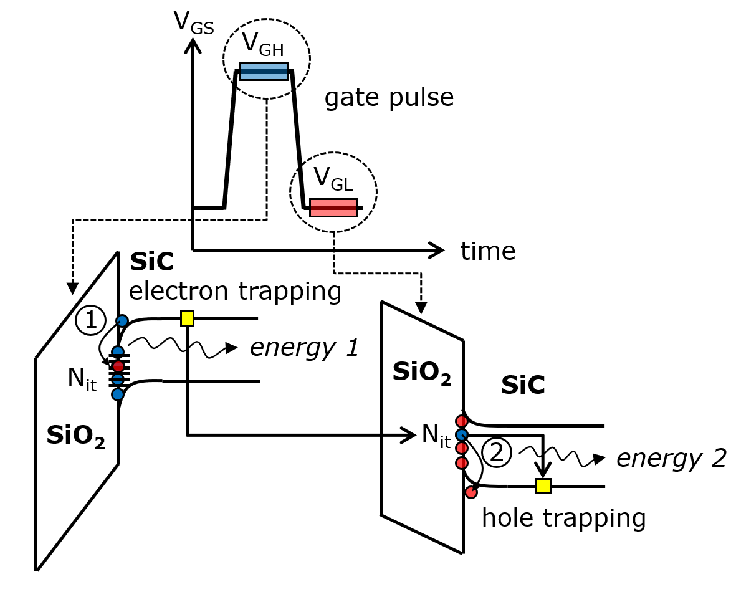

4.1 難點四:高dv/dt引發的米勒效應串擾

機理分析(橋式拓撲):

以半橋配置為例,當下管(S2)處于關斷狀態時,上管(S1)開始導通。S1的導通導致S2的漏源極(Drain-Source)電壓(VDS?)急劇上升,產生極高的dv/dt(例如 > 50 V/ns)。

位移電流: 這個高dv/dt通過S2的米勒電容(Cgd?,在Datasheet中即Crss?)感應出一個位移電流 imiller?=Crss??(dv/dt) 。

誤導通: 該電流imiller?流經S2的柵極驅動回路(主要是關斷電阻RG,off?)。它會在RG,off?上產生一個正向的電壓尖峰 Vspike?≈imiller??RG,off?。

直通失效: 如果 Vspike? 超過了S2的閾值電壓 VGS(th)?,S2將瞬間“誤導通”。此時S1和S2同時導通,形成上下管直通(Shoot-through),產生巨大的短路電流尖峰,輕則增加系統損耗,重則導致模塊炸毀 。

4.2 挑戰的加劇:SiC的物理特性與NTC的VGS(th)?

SiC MOSFET的固有物理特性,使其天然地極易遭受串擾風險,尤其是在高溫工作時:

高dv/dt: SiC的開關速度極快,dv/dt值本身就遠高于Si器件 。

低VGS(th)?: SiC的VGS(th)?典型值(約2-3V)遠低于同規格Si IGBT(約5-6V),導致其抵抗柵極噪聲的裕量(Noise Margin)極低 。

VGS(th)?的負溫度系數(NTC): 這是最關鍵的風險點。基本半導體的Datasheet數據顯示:

B3M013C120Z的VGS(th)?典型值從25°C的2.7V降低到175°C的1.9V 。

B3M010C075Z的VGS(th)?典型值同樣從2.7V降低到1.9V 。

這種NTC特性意味著:器件在滿載、高溫運行時,其閾值電壓最低,抗串擾能力最弱,系統處于最容易發生誤導通的危險狀態。

4.3 解決方案(一):芯片物理層面——優化電容比

原理:

誤導通電壓Vspike?的大小,取決于imiller?電流在柵極回路上的分流。柵極回路上主要有兩個電容:米勒電容Crss?和柵源電容Cgs?(Ciss?≈Cgs?+Crss?)。Vspike?的大小近似于一個由Crss?和Cgs?構成的電容分壓器, Vspike?∝(Crss?/Cgs?) 或 Vspike?∝(Crss?/Ciss?)。

要從根本上降低Vspike?,就必須在芯片設計時降低 Crss?或提高 Ciss?(即Cgs?)。

基本半導體產品力(高 Ciss?/Crss? 比值):

基本半導體在B3M系列芯片設計中,明確地針對抗串擾能力進行了優化:

產品特點中明確宣稱:“提高 Ciss?/Crss? 比值,降低器件在串擾行為下的誤導通風險” 。

這是一個關鍵的設計權衡(Trade-off)。提高Ciss?會增加總柵極電荷QG?,需要更強的驅動,但基本半導體有意做出這種權衡,以換取對并聯應用至關重要的“抗串擾魯棒性”。

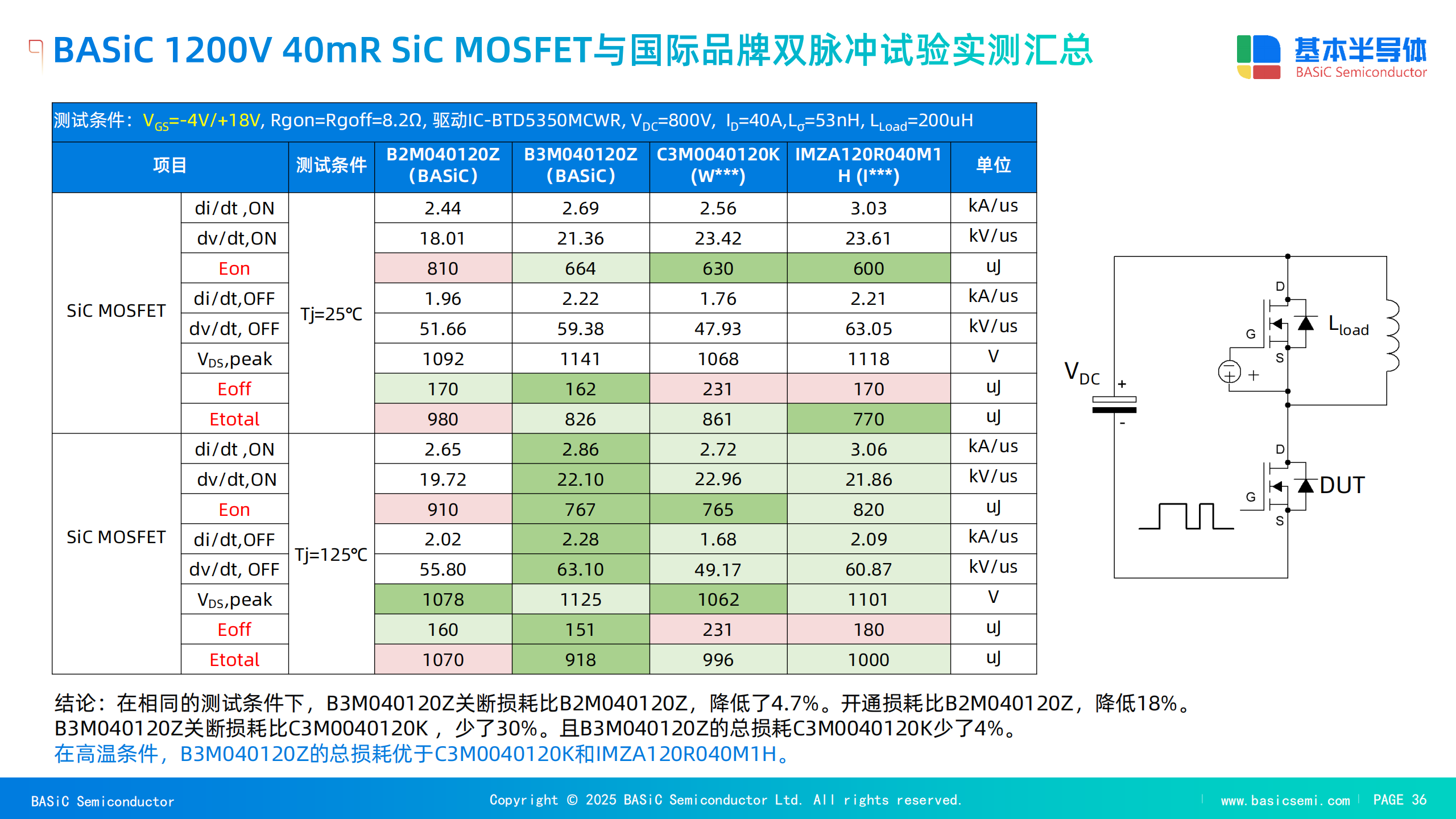

在與競品的對比中可見 1,B3M040120Z的Crss?(6 pF)遠低于Infineon的11 pF和Rohm的27 pF,實現了極為優異的電容比,從芯片物理層面構筑了第一道防線。

4.4 解決方案(二):驅動電路層面——負壓關斷與米勒鉗位

原理1(負壓關斷):

既然Vspike?是正向尖峰,那么在關斷時,不將VGS?鉗位在0V,而是施加一個負偏壓(如-4V或-5V)。這樣,Vspike?必須首先克服這個-5V的“安全裕量”,才能達到+1.9V的VGS(th)?(高溫時),從而極大地提高了抗噪能力。

原理2(主動米勒鉗位):

在關斷期間,當VGS?降低到安全閾值以下時,驅動芯片額外激活一個鉗位三極管(BJT)或小MOSFET,將柵極(Gate)通過一個極低阻抗的路徑(遠小于RG,off?)直接短接到開爾文源極(Kelvin Source)。米勒電流imiller?將從這個低阻抗路徑泄放,無法在RG,off?上累積起足夠的誤導通電壓 。

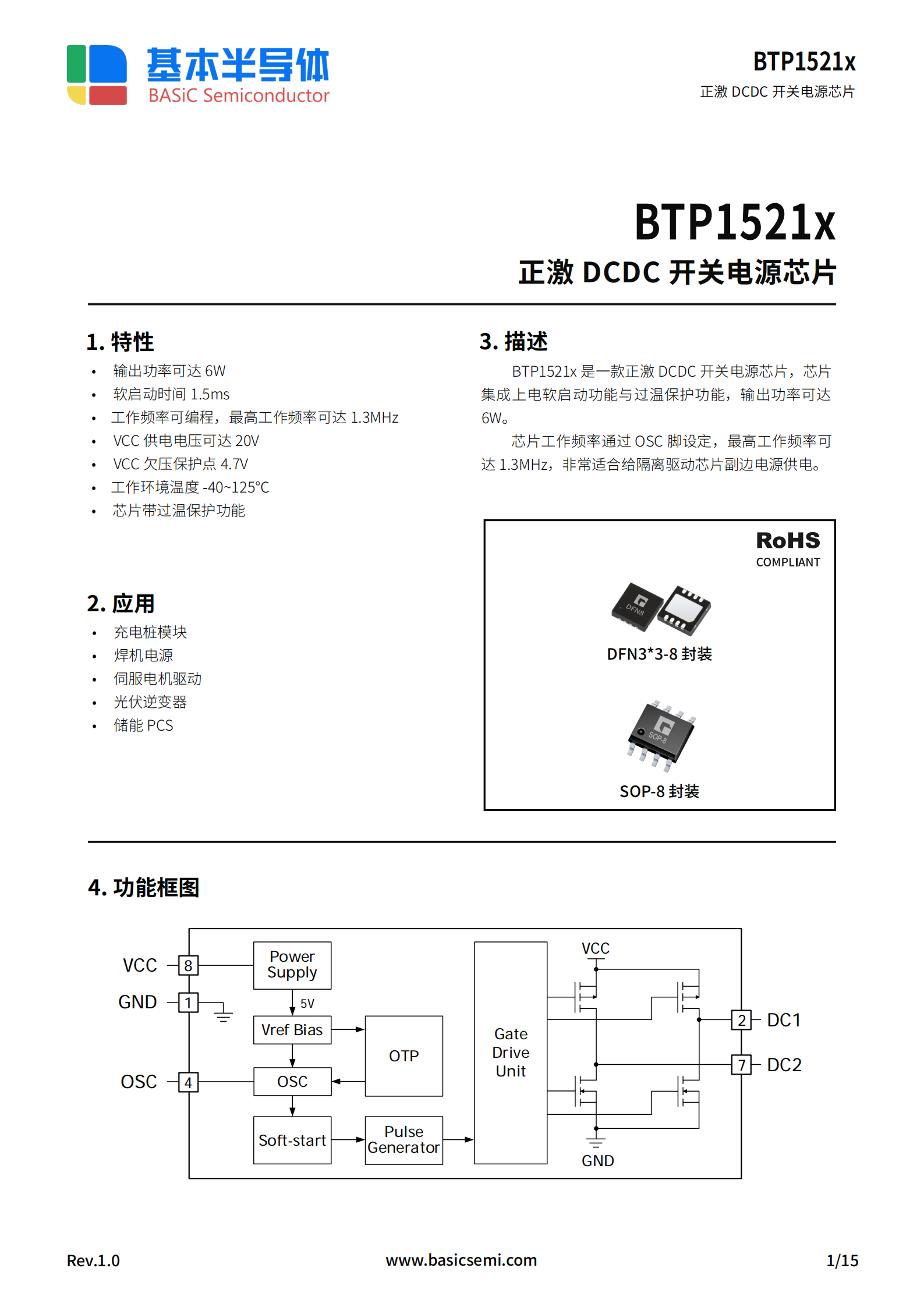

基本半導體產品力(驅動生態):

SiC器件(尤其是并聯應用)必須配備具有負壓關斷和米勒鉗位功能的先進驅動器。基本半導體通過提供配套的驅動芯片和方案,確保了其SiC器件的性能得以實現:

其四大產品系列中,明確包含“功率器件驅動板、驅動芯片、電源管理芯片” 。

提供了BTD系列隔離驅動芯片和BTP系列電源芯片 。

提供“驅動整體解決方案”,包括驅動核、即插即用驅動和成套驅動方案,可覆蓋多并聯應用場景 。

這種“芯片+驅動”的生態系統,確保了客戶在采用其SiC器件時,能夠獲得經過驗證的驅動方案,極大地降低了應用門檻,并保障了系統免受串擾失效的威脅。

第五章:系統集成與熱管理:確保長期并聯可靠性

5.1 難點五:并聯系統的熱耦合與熱失衡

機理分析:

即使并聯的器件參數在25°C時完美一致(得益于1的高一致性),如果封裝的熱阻(Rth(j?c)?)不一致,或者器件到散熱器的安裝熱阻(Rth(c?h)?)不一致,也會導致并聯器件的結溫(Tj?)在運行時產生差異。

影響:

Tj?的不均衡會反過來影響RDS(on)?(PTC特性)和VGS(th)?(NTC特性),再次破壞在第二章和第四章中建立的靜態和動態均流平衡,形成惡性循環 2。

解決方案:

在模塊封裝層面,必須采用高導熱性、高可靠性(抗熱循環、抗彎曲)的封裝材料,確保熱量能被均勻、高效地導出。

5.2 基本半導體產品力(高可靠性封裝)

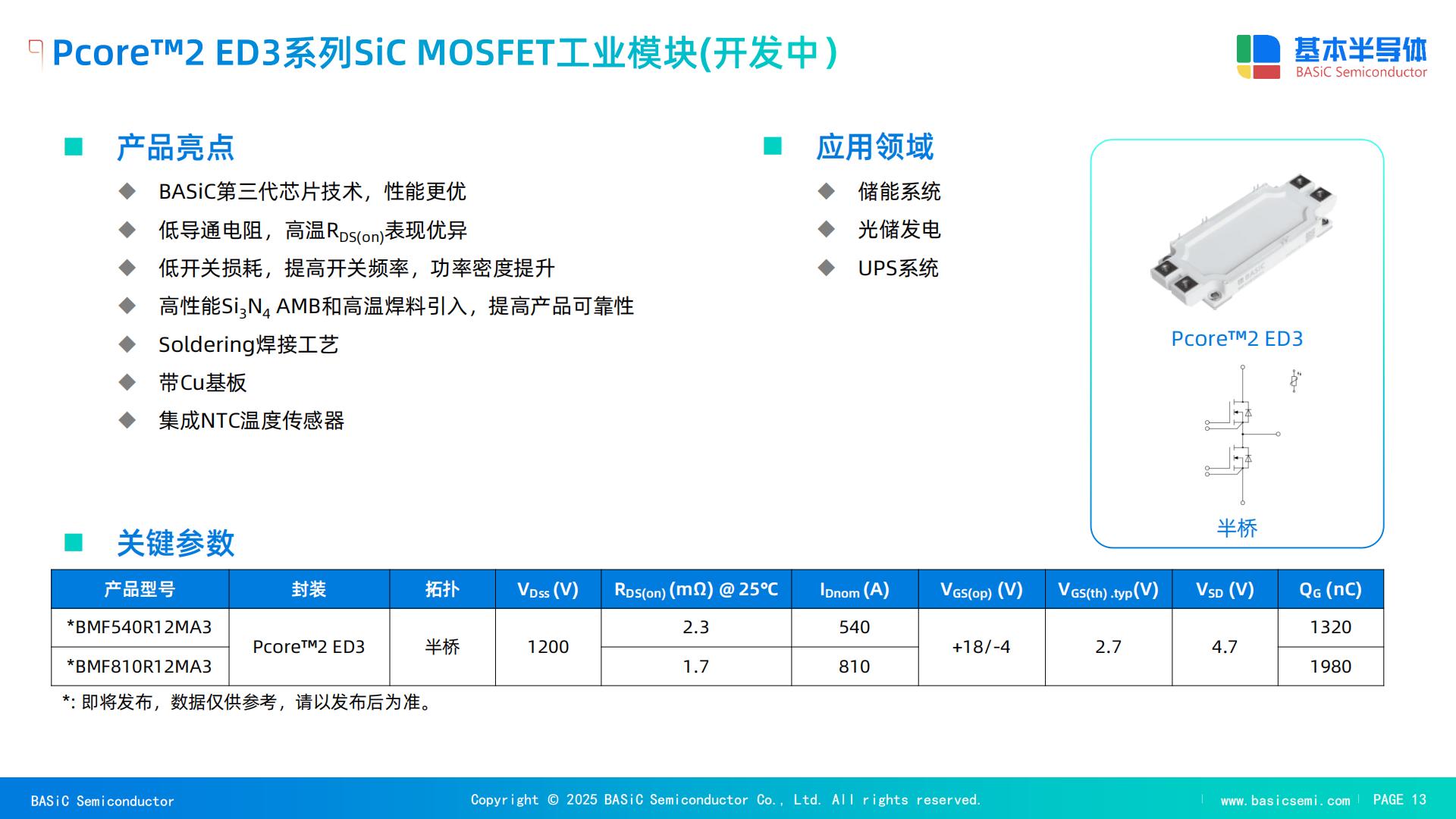

基本半導體的工業級和車規級功率模塊,在封裝材料上進行了重點優化,以確保并聯裸片的長期熱均衡:

核心材料: 模塊產品亮點中反復強調引入了“高性能 Si3?N4? AMB(氮化硅陶瓷基板)和高溫焊料” 。

Si3?N4? 的優勢: 相比傳統的Al2?O3?(氧化鋁)DBC基板, Si3?N4?(氮化硅)AMB具有:

高可靠性: 抗彎強度(Bending Strength)遠高于Al2?O3?和AlN(700 vs 450 N/mm2) 。

低熱失配: 其熱膨脹系數CTE(2.5 ppm/K)與SiC芯片(~4 ppm/K)更為接近,而Al2?O3?則高達6.8 ppm/K 。

分析: 這意味著基本半導體的模塊在經受高低溫循環(TCT)時,基板與芯片之間不易因熱失配而產生應力,不易開裂或分層,可靠性極高。高導熱性和高溫焊料則確保了并聯的每個Die產生的熱量都能高效、均勻地傳遞到散熱器,維持系統熱均衡,從而保障了長期的電氣均流性能。

深圳市傾佳電子有限公司(簡稱“傾佳電子”)是聚焦新能源與電力電子變革的核心推動者:

傾佳電子成立于2018年,總部位于深圳福田區,定位于功率半導體與新能源汽車連接器的專業分銷商,業務聚焦三大方向:

新能源:覆蓋光伏、儲能、充電基礎設施;

交通電動化:服務新能源汽車三電系統(電控、電池、電機)及高壓平臺升級;

數字化轉型:支持AI算力電源、數據中心等新型電力電子應用。

公司以“推動國產SiC替代進口、加速能源低碳轉型”為使命,響應國家“雙碳”政策(碳達峰、碳中和),致力于降低電力電子系統能耗。

需求SiC碳化硅MOSFET單管及功率模塊,配套驅動板及驅動IC,請聯系傾佳電子楊茜微芯(壹叁貳 陸陸陸陸 叁叁壹叁)

第六章:并聯挑戰與基本半導體的系統性對策矩陣

下表總結了SiC MOSFET并聯設計的核心技術挑戰,以及基本半導體如何通過其產品力提供系統性的應對策略。

表1:SiC MOSFET并聯技術難點與基本半導體產品力應對矩陣

| 技術挑戰 (Challenge) | 物理機理 (Mechanism) | 解決方案 (Solution Strategy) | 基本半導體產品力證據 (BASIC Product Strength) | 涉及產品 (Products) |

|---|---|---|---|---|

| 靜態均流 | RDS(on)? NTC特性導致熱失控 | RDS(on)? 呈正溫度系數 (PTC) | Datasheet證實 RDS(on)? 隨 Tj? 升高而顯著增加 | B3M/B2M系列分立器件 |

| 動態均流 (開/關同步性) | VGS(th)? 參數離散度大 | 極高制造工藝一致性 | 產品宣稱“偏差非常小,可不進行分選直接并聯使用” | B3M系列芯片 |

| 動態均流 (開關振蕩) | 共源電感 Ls? 負反饋 | 1. 驅動與功率回路解耦 . 封裝低電感設計 | 1. 采用4-Pin 開爾文源極封裝 1 2. 模塊雜散電感 Ls?<5.5 nH (車規)? | 1. TO-247-4 等分立器件 2. Pcore? 系列功率模塊 |

| 串擾/誤導通 (Crosstalk) | imiller?=Crss??(dv/dt) 且 VGS(th)? 低 (NTC特性) | 1. 優化芯片電容比 2 負壓關斷 . 主動米勒鉗位 | 1. 芯片設計“提高 Ciss?/Crss? 比值” 1 2. & 3. 提供配套的驅動芯片與驅動方案 | 1. B3M系列芯片 2. BTD/BTP 驅動IC |

| 系統熱均衡 | 封裝熱阻不均,熱循環失效 | 高導熱、高可靠性封裝 | 采用“高性能 Si3?N4? AMB和高溫焊料” | Pcore? 工業/車規模塊 |

第七章:結論性評估

SiC MOSFET的并聯挑戰是真實、復雜且多維度的。SiC的高速特性(高dv/dt, di/dt)和固有物理特性(低VGS(th)?及其負溫度系數 )是串擾和振蕩的根源。

成功的并聯策略必須是一個系統工程,涵蓋:

芯片層: 具備PTC特性的RDS(on)?、高度一致的VGS(th)? ,以及抗串擾優化的電容比(高 Ciss?/Crss?) 。

封裝層: 采用開爾文源極(4-Pin)封裝 消除共源電感,或采用低雜散電感(< 10nH)、高可靠性(Si3?N4? AMB)的對稱功率模塊 。

驅動層: 必須配合使用具有負壓關斷和主動米勒鉗位功能的驅動器 。

基本半導體(BASIC Semiconductor)的產品力 不 在于某一項單一指標的領先,而在于其精準預判并系統性地解決了并聯應用中的 所有 關鍵痛點。它通過其B3M系列提供了“并聯友好”的芯片物理特性 ,通過4-Pin分立器件和Pcore?模塊提供了“并聯優化”的封裝 ,并通過配套的驅動IC提供了“并聯必需”的驅動方案1。

這種從芯片設計、晶圓制造、先進封裝到驅動方案的垂直整合能力 ,構成了其在SiC高功率并聯應用市場上的核心產品力。

審核編輯 黃宇

-

功率半導體

+關注

關注

23文章

1463瀏覽量

45195 -

SiC MOSFET

+關注

關注

1文章

153瀏覽量

6795

發布評論請先 登錄

QDPAK封裝SiC碳化硅MOSFET安裝指南

碳化硅(SiC)MOSFET模塊硬并聯中環流產生的根本機理及綜合抑制策略

半導體“碳化硅(SiC) MOSFET柵極驅動”詳解

傾佳電子碳化硅MOSFET高級柵極驅動設計:核心原理與未來趨勢綜合技術評述

基本半導體碳化硅 MOSFET 的 Eoff 特性及其在電力電子領域的應用

國產SiC碳化硅功率半導體企業引領全球市場格局重構

基本半導體碳化硅(SiC)MOSFET低關斷損耗(Eoff)特性的應用優勢

基于國產碳化硅SiC MOSFET的高效熱泵與商用空調系統解決方案

碳化硅何以英飛凌?—— SiC MOSFET性能評價的真相

低劣品質碳化硅MOSFET的濫用將SiC逆變焊機直接推向“早衰”

麥科信光隔離探頭在碳化硅(SiC)MOSFET動態測試中的應用

碳化硅(SiC)MOSFET替代硅基IGBT常見問題Q&A

碳化硅SiC MOSFET并聯的技術瓶頸與系統性克服策略

碳化硅SiC MOSFET并聯的技術瓶頸與系統性克服策略

評論