在嵌入式與服務(wù)器開發(fā)中,PCIe(PCI Express)接口早已成為連接高速外設(shè)的“標(biāo)配”——小到PCIe無線網(wǎng)卡、SSD,大到FPGA加速卡、顯卡,都依賴它實(shí)現(xiàn)高速數(shù)據(jù)傳輸。但不少工程師都會遇到一個(gè)棘手問題:PCIe設(shè)備有時(shí)能正常識別,有時(shí)卻突然“失聯(lián)”,這種概率性識別失敗的故障,比必現(xiàn)故障更難排查,往往卡在硬件設(shè)計(jì)或調(diào)試環(huán)節(jié)浪費(fèi)大量時(shí)間。

今天我們就從PCIe接口的核心原理入手,拆解開發(fā)中的關(guān)鍵注意事項(xiàng),并針對“原理圖一致性”“電感干擾”“串口電流倒灌”這三個(gè)高頻故障點(diǎn),給出具體的排查方案,幫你快速定位問題。

一、先搞懂:PCIe接口為什么能“高速又穩(wěn)定”?

要排查識別失敗問題,首先得明白PCIe的工作邏輯——它的“穩(wěn)定”依賴硬件信號、供電、枚舉流程的協(xié)同,任何一個(gè)環(huán)節(jié)的微小偏差,都可能導(dǎo)致“概率性故障”。

1. PCIe的核心架構(gòu):從“拓?fù)?/span>”到“枚舉”

PCIe采用“點(diǎn)對點(diǎn)串行拓?fù)?/span>”,由根復(fù)合體(Root Comple

x,比如PU內(nèi)的PCIe控制器)、端點(diǎn)設(shè)備(Endpoint,比如PCIe網(wǎng)卡)、交換機(jī)(Switch,擴(kuò)展多設(shè)備)組成,每個(gè)設(shè)備通過“Lane(通道)”傳輸數(shù)據(jù)(常見x1/x4/x8/x16通道,通道數(shù)越多速度越快)。

而設(shè)備能否被識別,關(guān)鍵在于枚舉流程:

1.系統(tǒng)上電后,根復(fù)合體先初始化PCIe總線;

2.根復(fù)合體發(fā)送“枚舉命令”,掃描總線上的端點(diǎn)設(shè)備;C

3.端點(diǎn)設(shè)備收到命令后,返回自身的“配置空間信息”(如設(shè)備ID、廠商ID、接口類型);

4.根復(fù)合體根據(jù)配置信息,為設(shè)備分配總線號、內(nèi)存地址空間,完成識別。

整個(gè)過程對信號時(shí)序和供電穩(wěn)定性要求極高——若信號延遲超標(biāo)、供電電壓波動(dòng),就可能導(dǎo)致枚舉“偶發(fā)超時(shí)”,設(shè)備自然無法識別。

2. PCIe的信號與供電:“差分之美”與“電壓紅線”

?信號特性:PCIe用“差分信號”傳輸數(shù)據(jù)(一對反向的信號線,如TX+/-、RX+/-),這種設(shè)計(jì)能抵消外界干擾,但也對硬件設(shè)計(jì)提出嚴(yán)格要求:

差分對的線長必須匹配(誤差通常要求≤5mm)、阻抗需嚴(yán)格控制(通常為100Ω±10%),若線長不匹配或阻抗突變,會導(dǎo)致信號反射,出現(xiàn)“時(shí)好時(shí)壞”的傳輸問題。

?供電要求:PCIe設(shè)備需要多種穩(wěn)定電壓供電(如12V主供電、3.3V輔助供電、1.8V/1.05V核心供電),且電壓波動(dòng)范圍有明確限制(如12V允許±8%,3.3V允許±5%)。一旦供電電壓跌落或出現(xiàn)尖峰噪聲,設(shè)備可能無法完成初始化,導(dǎo)致識別失敗。

二、開發(fā)避坑:PCIe硬件設(shè)計(jì)的3個(gè)“生死線”

概率性識別失敗,90%的問題出在硬件設(shè)計(jì)階段。在畫原理圖、做PCB時(shí),這三個(gè)關(guān)鍵點(diǎn)必須嚴(yán)格把控,否則后期調(diào)試會陷入“無頭蒼蠅”狀態(tài)。

1.嚴(yán)格遵循“官方參考設(shè)計(jì)”,拒絕“想當(dāng)然修改”

PCIe控制器廠商(如Intel、AMD、Rockchip、Nvidia)會提供詳細(xì)的“PCIe接口參考設(shè)計(jì)”,包括原理圖、PCB布局指南、物料選型建議。很多工程師為了“簡化設(shè)計(jì)”或“適配現(xiàn)有物料”,會私自修改原理圖(比如更換復(fù)位芯片、調(diào)整供電電路),這往往是概率性故障的“埋雷點(diǎn)”。

比如某Rockchip平臺開發(fā)中,工程師將PCIe復(fù)位信號的上拉電阻從4.7kΩ改為10kΩ,導(dǎo)致復(fù)位信號上升沿過緩,系統(tǒng)枚舉時(shí)偶爾檢測不到復(fù)位完成信號,設(shè)備就會“隨機(jī)失聯(lián)”。

核心原則:原理圖中的“復(fù)位電路、供電時(shí)序電路、時(shí)鐘電路、差分信號匹配電阻”,必須1:1對照官方參考設(shè)計(jì),任何修改都需先與廠商FAE確認(rèn)。

2.電感選型與布局:別讓“濾波元件”變成“干擾源”

PCIe供電電路中,通常會用電感實(shí)現(xiàn)“濾波”和“儲能”(比如在12V轉(zhuǎn)3.3V的Buck電路中),但電感若選型不當(dāng)或布局錯(cuò)誤,會成為“信號干擾器”:

?選型錯(cuò)誤:若電感的“寄生電容”“寄生電阻”過大,會在供電線上引入低頻噪聲,干擾PCIe設(shè)備的核心供電;

?布局錯(cuò)誤:若電感靠近PCIe差分信號線(距離<3mm),電感工作時(shí)產(chǎn)生的磁場會耦合到差分信號中,破壞信號完整性,導(dǎo)致傳輸誤碼率升高,枚舉偶爾失敗。

避坑建議:優(yōu)先選用廠商參考設(shè)計(jì)中推薦的電感型號(如TDK的SLF系列、Murata的LQM系列),且電感與PCIe差分信號線的距離需≥5mm,同時(shí)避免電感與差分對平行布局。

3. debug串口:別讓“調(diào)試工具”變成“供電殺手”

很多工程師習(xí)慣在開發(fā)板上預(yù)留debug串口(如UART轉(zhuǎn)USB),方便打印日志調(diào)試,但很少注意:串口接上電腦時(shí),可能會發(fā)生“電流倒灌”,干擾PCIe供電。

原理很簡單:電腦USB口的輸出電壓通常為5V/3.3V,而開發(fā)板上PCIe設(shè)備的輔助供電也是3.3V。若兩者的“地電位”存在差異(比如電腦接地不良,開發(fā)板接外部電源),就會形成“電位差”,導(dǎo)致電流從USB口倒灌到PCIe的3.3V供電回路中——輕則導(dǎo)致PCIe供電電壓被拉低(比如從3.3V跌到3.1V以下),重則燒毀供電芯片,直接讓設(shè)備無法上電。

調(diào)試注意:

?接debug串口前,確認(rèn)電腦與開發(fā)板的“地”是否共地(比如用萬用表測兩者的GND引腳,電位差應(yīng)≤0.1V);

?若需獨(dú)立供電(開發(fā)板用外部電源,電腦單獨(dú)供電),建議在串口的VCC引腳串一個(gè)“二極管”(如SS14),防止電流倒灌。

三、實(shí)戰(zhàn)排查:3個(gè)高頻故障的定位方法

當(dāng)遇到PCIe設(shè)備概率性識別失敗時(shí),不用盲目換設(shè)備、改代碼,按以下步驟排查,能快速鎖定問題。

1.排查“原理圖一致性”:從源頭排除設(shè)計(jì)缺陷

概率性故障若出現(xiàn)在批量生產(chǎn)階段,先優(yōu)先核對原理圖與官方參考設(shè)計(jì)的差異:

?工具輔助:用Altium Designer、Cadence等工具的“原理圖比較功能”,將自己的設(shè)計(jì)與官方參考圖逐頁對比,重點(diǎn)關(guān)注:

?復(fù)位電路:復(fù)位芯片型號、上拉/下拉電阻阻值、復(fù)位延遲參數(shù);

?供電電路:電源芯片型號、電感/電容參數(shù)、電壓反饋電阻阻值;

?差分信號:是否有匹配電阻(通常為50Ω或100Ω)、電阻位置是否在靠近設(shè)備端(官方一般要求匹配電阻靠近端點(diǎn)設(shè)備,減少信號反射)。

?實(shí)物核對:對照BOM表,檢查焊接的物料型號是否與原理圖一致(比如電容容值、電阻阻值是否錯(cuò)焊),避免“原理圖對了,但物料貼錯(cuò)了”的低級錯(cuò)誤。

2.排查“電感干擾”:用示波器看信號“健康度”

若懷疑電感影響信號,可通過“信號測試”驗(yàn)證:

?測差分信號眼圖:用示波器(需支持差分探頭)連接PCIe的TX+/-或RX+/-信號,采集信號眼圖——若眼圖“眼高”不足(低于標(biāo)準(zhǔn)值的80%)、“眼寬”過窄,或存在明顯的噪聲尖峰,說明信號被干擾,需檢查電感布局是否違規(guī),或更換低寄生參數(shù)的電感。

?測供電噪聲:用示波器測PCIe設(shè)備的3.3V輔助供電電壓,若電壓波動(dòng)超過±5%(比如3.3V跌到3.1V以下),或存在頻率在100kHz~1MHz的低頻噪聲,大概率是電感濾波效果差,需更換電感或增加濾波電容(如在供電端并聯(lián)10μF+0.1μF的電容組合)。

3.排查“debug串口電流倒灌”:測供電電位差

若接上debug串口后,PCIe識別失敗概率明顯升高,可按以下步驟驗(yàn)證:

?斷電測試:斷開開發(fā)板外部電源,只接debug串口的USB線,用萬用表測PCIe設(shè)備的3.3V供電引腳——若有電壓(比如測到2.5V),說明存在電流倒灌(USB的3.3V通過串口倒灌到PCIe供電回路)。

?通電測試:接好開發(fā)板外部電源,再接debug串口,用示波器測PCIe的3.3V供電電壓——若接上串口后,電壓出現(xiàn)明顯跌落(如從3.3V跌到3.0V),需在串口VCC引腳串二極管,或改用“只傳數(shù)據(jù)、不供電”的串口線(斷開USB的VCC引腳)。

四、總結(jié):PCIe識別穩(wěn)定的核心——“細(xì)節(jié)不妥協(xié)”

PCIe設(shè)備的概率性識別失敗,看似“偶發(fā)”,實(shí)則是“硬件設(shè)計(jì)細(xì)節(jié)不到位”的必然結(jié)果。總結(jié)下來,關(guān)鍵就三句話:

1.參考設(shè)計(jì)別亂改:原理圖、物料選型嚴(yán)格遵循廠商指南,不輕易“簡化”或“替代”;

2.信號供電要盯緊:差分信號的線長、阻抗,供電的電壓穩(wěn)定性,用工具實(shí)測驗(yàn)證,不憑“感覺”判斷;

3.調(diào)試環(huán)節(jié)防意外:debug串口、外部設(shè)備接入時(shí),先考慮電位差、電流倒灌風(fēng)險(xiǎn),避免“調(diào)試工具變故障源”。

其實(shí)PCIe接口的“穩(wěn)定性”并不可怕,只要在設(shè)計(jì)初期把好“原理圖、選型、布局”三關(guān),調(diào)試時(shí)用工具精準(zhǔn)定位,就能輕松避開概率性故障的坑。你在開發(fā)中還遇到過哪些PCIe識別問題?歡迎在評論區(qū)留言討論!

-

嵌入式

+關(guān)注

關(guān)注

5203文章

20549瀏覽量

335730 -

SSD

+關(guān)注

關(guān)注

21文章

3135瀏覽量

122360 -

PCIe

+關(guān)注

關(guān)注

16文章

1465瀏覽量

88735

發(fā)布評論請先 登錄

請問CYUSB3014批量傳輸失敗是什么原因導(dǎo)致的?

SPI從模式MISO會概率性出現(xiàn)毛刺的原因?

CYW43455同時(shí)多臺設(shè)備測試漫游切換功能,測幾百次有個(gè)別設(shè)備會概率性的斷線,為什么?

OPA548輸出脈沖概率性失真怎么解?

LM49450輸出引腳概率性燒壞的原因?

stm32f407+ksz8863rlli概率性ping不通

INA260讀取通路電流、電壓值,會出現(xiàn)概率性的數(shù)據(jù)異常,是什么原因引起的?

是什么原因導(dǎo)致RK3399板卡概率性CPU和EMMC通訊失敗跑不起來呢

單片機(jī)解密失敗的原因

ESP32-S3模組燒錄又失敗?分享怎么排查原因

點(diǎn)焊型應(yīng)變計(jì)焊接失敗怎么辦?5步排查法+3個(gè)防護(hù)技巧

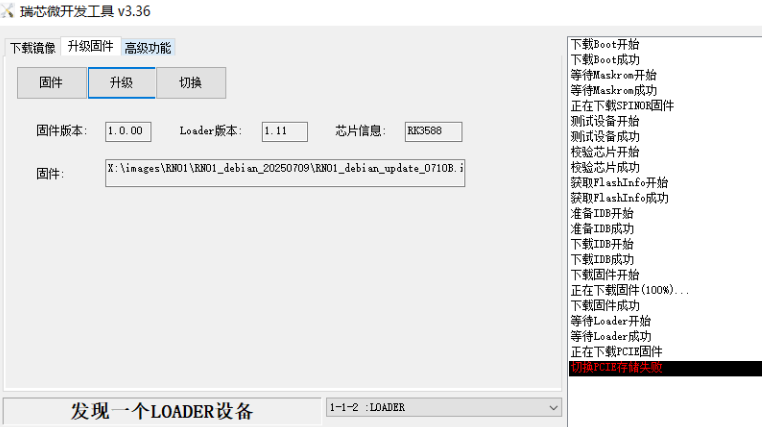

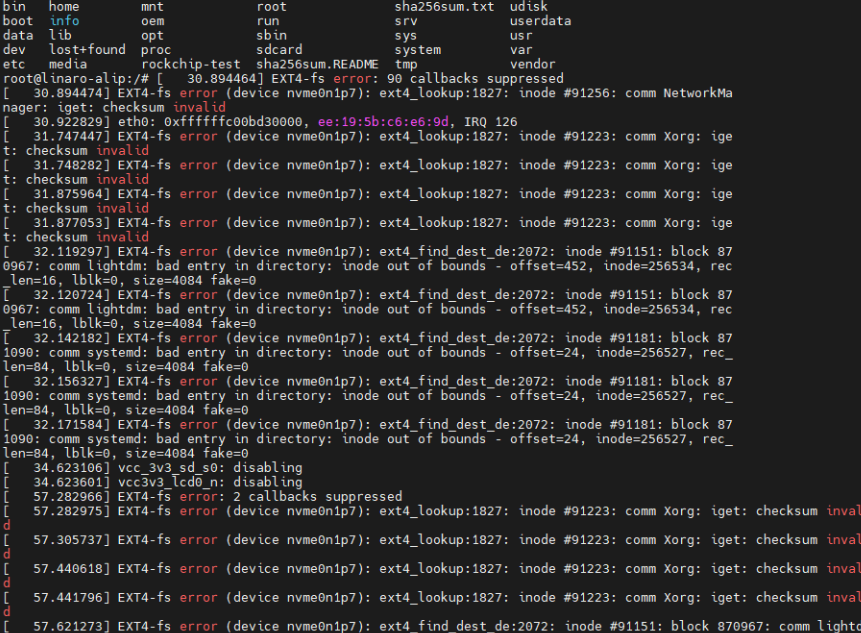

RK3588 PCIe設(shè)備識別失敗?一招避坑“非法Class”陷阱

PCIe設(shè)備與電感:影響設(shè)備識別的關(guān)鍵因素——走訪電感源頭公司有感

PCIe設(shè)備概率性識別失敗?這3個(gè)核心原因與排查思路

PCIe設(shè)備概率性識別失敗?這3個(gè)核心原因與排查思路

評論