最近看好多人因為pcie這個問題困擾,遂再更一版關于pcie調試的文章。

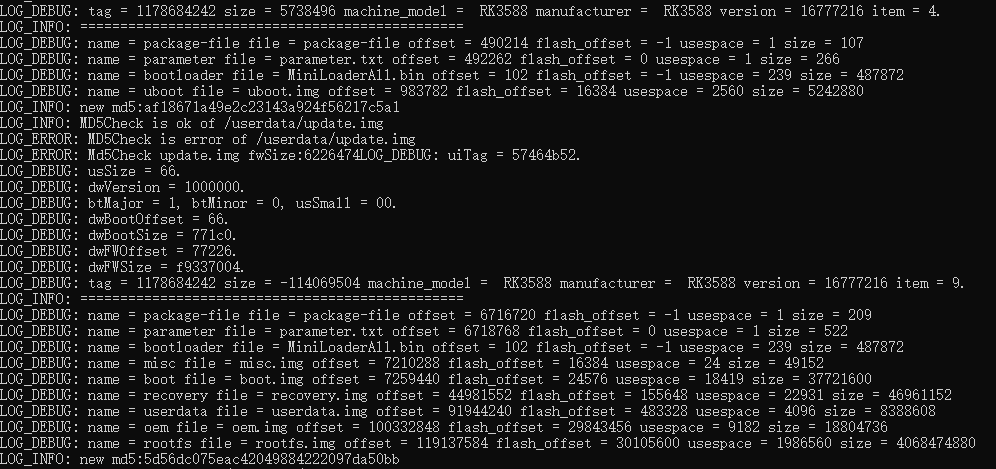

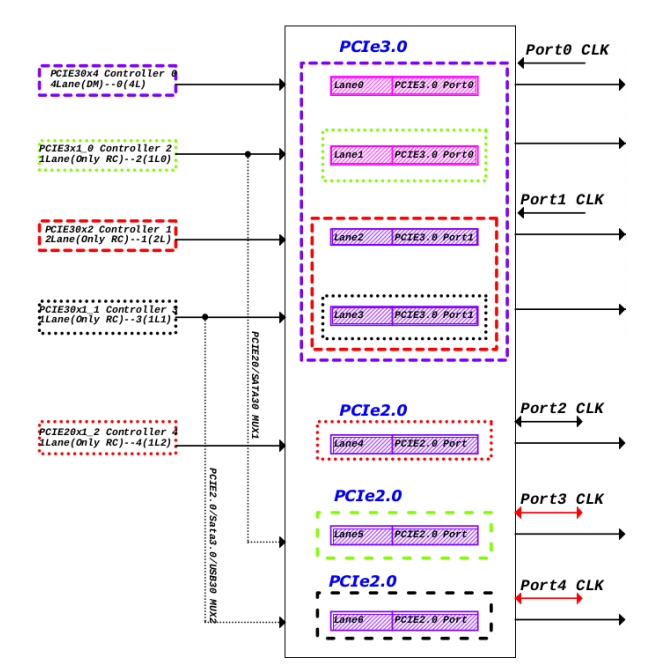

在嵌入式開發中,PCIE接口的SSD因高速讀寫特性,常作為RK(瑞芯微)平臺的核心存儲方案。但調試時難免遇到“詭異”問題——比如插入SSD時一切正常,不插SSD系統就直接起不來,甚至改了配置后還偶發啟動失敗。

今天結合實際調試文檔,拆解這兩個典型坑的排查過程與解決方案,幫你避開PCIe SSD調試的“隱形陷阱”。

一、初始坑:不插SSD,系統直接“罷工”

1.現象:插與不插,兩種命運

?正常場景:插入SSD后,系統啟動流暢,SSD能被正確識別并正常讀寫;

?異常場景:拔掉SSD,系統卡在啟動階段,無報錯日志,直接“死機”。

2.排查:從“時鐘”定位到“引腳配置”

一開始懷疑電源或PCIe鏈路問題,逐一排查后發現關鍵線索:

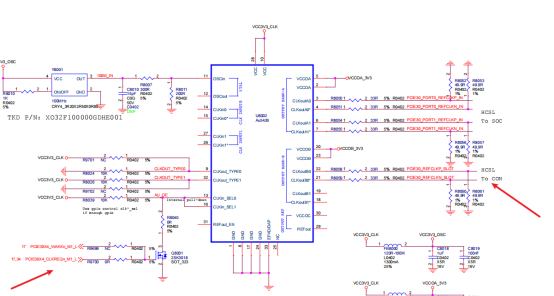

?測量PCIe相關電壓(如vpcie3v3):無論是否插SSD,電壓均穩定在3.3V,排除電源故障;

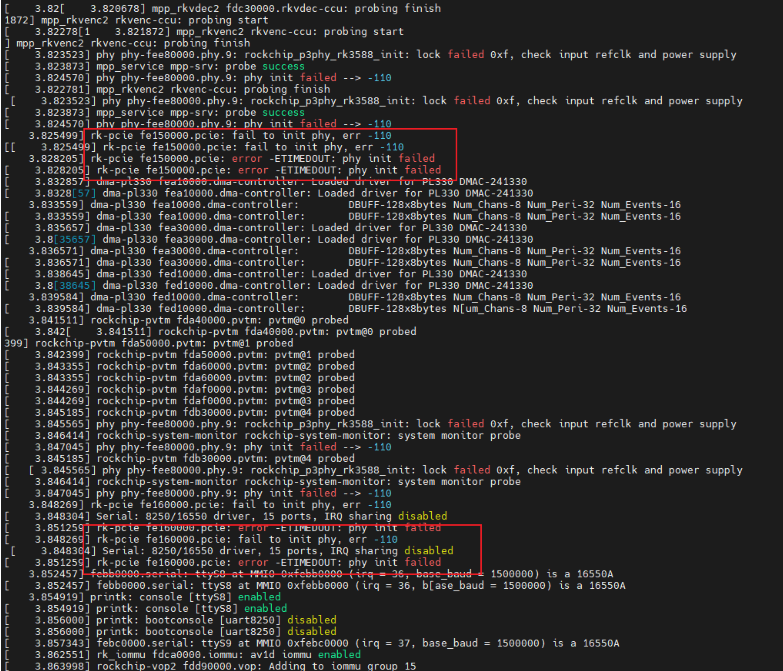

?用示波器測PCIe時鐘信號:不插SSD時,時鐘引腳無輸出,插入后時鐘恢復正常——問題出在時鐘使能的控制邏輯。

進一步核對DTS(設備樹)配置,發現核心控制引腳PCIE30X4_CLKREQn_M1(對應GPIO4 RK_PB4)的配置存在問題:

|

//初始錯誤配置

pcie20x1_0_clkreqn_m1: pcie20x1-0-clkreqn-m1 {

rockchip,pins = <4 RK_PB4 RK_FUNC_GPIO &pcfg_pull_none>; //浮空狀態

};

|

&pcfg_pull_none表示引腳處于浮空狀態:插入SSD時,SSD會主動拉低該引腳觸發時鐘輸出;不插SSD時,引腳電平懸空,無法觸發時鐘,導致系統啟動卡住。

3.解決方案:浮空→下拉,讓引腳“有個準信”

只需修改引腳的拉取狀態,將“浮空”改為“下拉”,確保即使不插SSD,引腳也能維持穩定電平以觸發時鐘:

|

//修改后正確配置

pcie20x1_0_clkreqn_m1: pcie20x1-0-clkreqn-m1 {

rockchip,pins = <4 RK_PB4 RK_FUNC_GPIO &pcfg_pull_down>; //下拉狀態

};

|

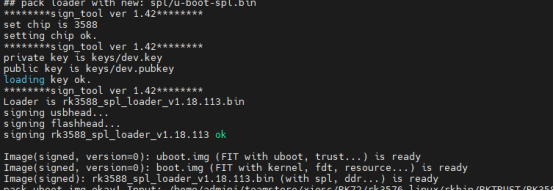

重新編譯燒錄后測試:不插SSD時,時鐘信號正常輸出,系統順利啟動——第一個坑解決!

二、二次坑:改了下拉,仍偶發“死機”

1.新現象:偶爾啟動失敗,無規律可循

解決初始問題后,測試中發現新情況:系統約有10%概率啟動失敗,重啟幾次又能恢復,無固定觸發條件,排查難度更高。

2.根因:驅動加載“干擾”引腳電平

再次核對DTS,發現&pcie3x4(PCIe控制器節點)中,將之前修改的引腳配置關聯到了驅動:

|

//存在問題的PCIe控制器配置

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

pinctrl-names = "default";

pinctrl-0 = <&pcie20x1_0_clkreqn_m1>; //引腳關聯驅動

status = "okay";

};

|

問題在于:驅動加載時,會動態調整關聯引腳的電平,導致PCIE30X4_CLKREQn_M1引腳有時高、有時低,電平不確定性觸發PCIe鏈路初始化失敗——這也是啟動失敗“無規律”的原因。

查閱RK官方原理圖與配置說明后確認:該引腳無需關聯PCIe驅動,需獨立控制以保證電平穩定。

3.終局解決方案:刪關聯+獨立配置,徹底穩電平

分兩步修改,徹底隔絕驅動對引腳的干擾:

步驟1:刪除PCIe驅動與引腳的關聯

修改&pcie3x4節點,注釋或刪除pinctrl-0配置,斷開驅動與引腳的綁定:

|

//修改后的PCIe控制器配置

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

pinctrl-names = "default";

//注釋關聯配置:避免驅動干擾引腳電平

// pinctrl-0 = <&pcie20x1_0_clkreqn_m1>;

status = "okay";

};

|

步驟2:單獨配置引腳為“固定電平調節器”

新增pcie3x4_clkreqn_m1節點,將引腳配置為regulator-fixed(固定調節器)類型,強制拉低并確保啟動階段穩定:

|

//獨立引腳配置(關鍵)

pcie3x4_clkreqn_m1: pcie3x4-clkreqn-m1{

compatible = "regulator-fixed"; //固定電平類型

gpio = <&gpio4 RK_PB4 GPIO_ACTIVE_LOW>; //低電平有效

pinctrl-names = "default";

pinctrl-0 = <&pcie20x1_0_clkreqn_m1>; //引用下拉配置

regulator-name = "pcie3x4_clkreqn_m1";

enable-active-low; //使能信號低電平有效

start-delays-us = <5000>; //啟動延遲5000微秒(避免沖擊)

off-on-delay-us = <5000>; //切換延遲5000微秒

regulator-always-on; //引腳始終保持使能

regulator-boot-on; //系統啟動階段即開啟

};

|

?start-delays-us與off-on-delay-us:避免引腳電平突變導致的鏈路誤判;

?regulator-always-on與regulator-boot-on:確保從系統上電到啟動完成,引腳始終維持穩定低電平。

修改后經過百次啟動測試:無論是否插SSD,系統均100%正常啟動,偶發故障徹底解決!

三、調試核心要點:3個“避坑準則”

1.引腳拉取狀態:拒絕浮空,優先下拉

PCIe的CLKREQn類控制引腳(如本文的GPIO4 RK_PB4),需避免&pcfg_pull_none(浮空),不插設備時會因電平不確定斷時鐘,下拉(&pcfg_pull_down)是更安全的選擇。

2.驅動關聯:控制引腳別綁驅動

非PCIe核心數據引腳(如時鐘控制、復位),無需在&pcie3x4等控制器節點中通過pinctrl-0關聯驅動,否則驅動加載會干擾電平穩定性。

3.獨立配置:用regulator-fixed穩電平

關鍵控制引腳建議按“固定調節器”配置,加上延遲參數(如5000us)和“始終開啟”屬性,從硬件層面杜絕電平波動。

結尾

PCIe調試常因“引腳電平”“驅動關聯”這類細節卡殼,看似詭異的故障,往往藏在DTS的幾行配置里。你在RK平臺調試PCIe設備時,還遇到過哪些“坑”?歡迎在評論區分享,一起避坑提效!

-

嵌入式

+關注

關注

5204文章

20562瀏覽量

336005 -

SSD

+關注

關注

21文章

3137瀏覽量

122412 -

引腳

+關注

關注

16文章

2115瀏覽量

55933 -

RK3588

+關注

關注

8文章

575瀏覽量

7490

發布評論請先 登錄

ROC-RK3588S-PC開發板支持SATA協議的SSD使用

RK3588S(Android 12) M.2接口的配置與使用手冊指南

RK3588與RK3399的區別

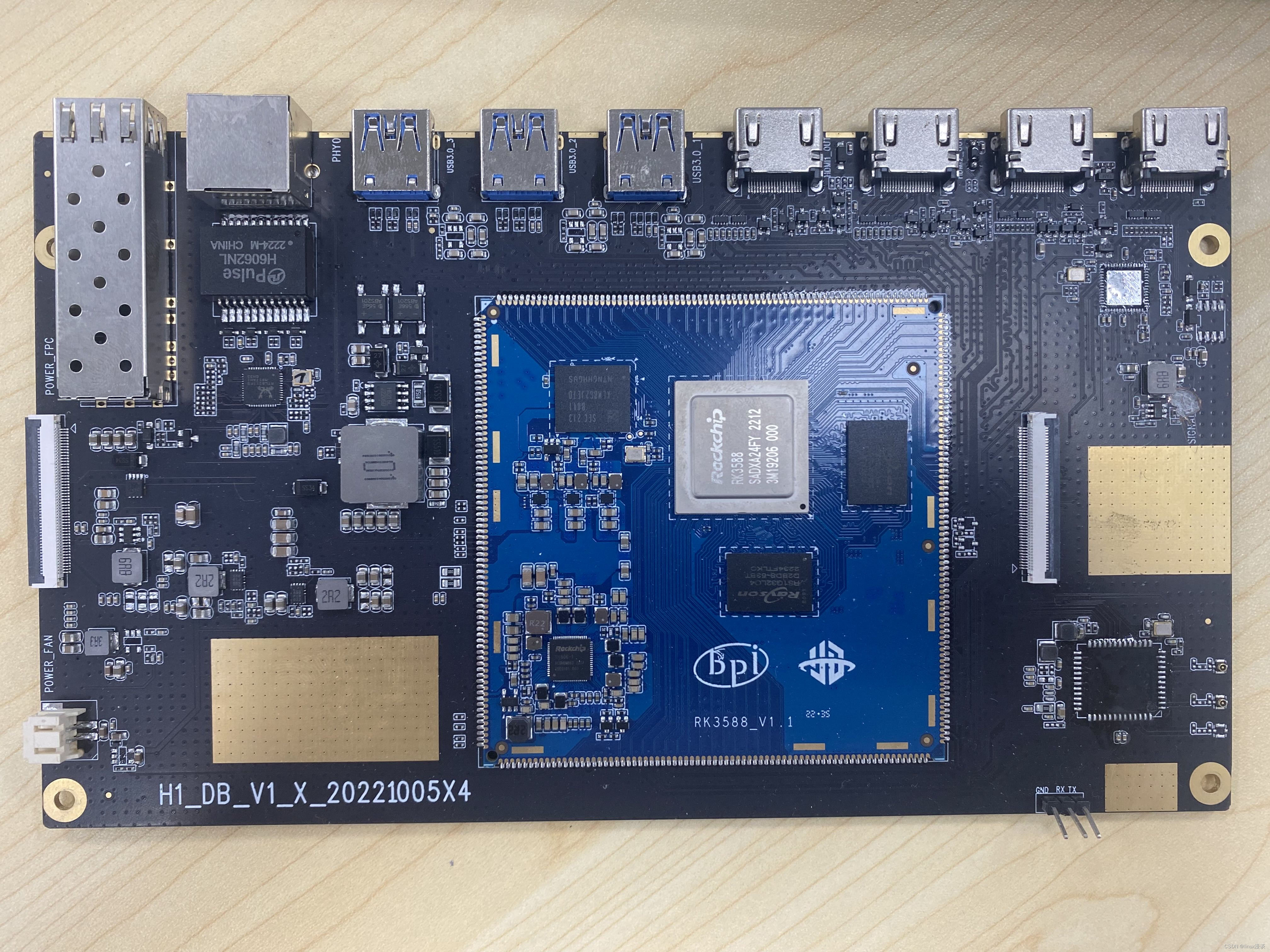

Banana Pi BPI-W3 RK3588平臺驅動調試篇 [ PCIE篇一 ] - PCIE的開發指南

![Banana Pi BPI-W3 <b class='flag-5'>RK3588</b><b class='flag-5'>平臺</b><b class='flag-5'>驅動</b><b class='flag-5'>調試</b>篇 [ <b class='flag-5'>PCIE</b>篇一 ] - <b class='flag-5'>PCIE</b>的開發指南](https://file1.elecfans.com//web2/M00/AB/FB/wKgaomVC-dmAdRZWAACj2N-ckc0705.jpg)

Banana Pi BPI-W3 RK3588平臺驅動調試篇 [ PCIE篇二 ] - PCIE的開發指南

![Banana Pi BPI-W3 <b class='flag-5'>RK3588</b><b class='flag-5'>平臺</b><b class='flag-5'>驅動</b><b class='flag-5'>調試</b>篇 [ <b class='flag-5'>PCIE</b>篇二 ] - <b class='flag-5'>PCIE</b>的開發指南](https://file1.elecfans.com//web2/M00/AB/FB/wKgaomVC-i-AZQiOAAJH8vK8vCE230.jpg)

RK3588 PCIe設備識別失敗?一招避坑“非法Class”陷阱

開發者必備,10 分鐘搞定 RK3588 PCIE 拆分!

RK3588平臺雙存儲(SPI+PCIE)OTA升級方案教學文檔

一文搞懂?RK3588 PCIe:從硬件資源到拆分配置?+?避坑指南(含腦圖)

實戰復盤:RK3588 SPI+PCIe3x4方案啟動修復,從節點配置到驅動適配全解析

保姆級教程!RK3588 Linux6.1?固件簽名完整實現方案(不含rootfs)

RK3588平臺SSD PCIE調試踩坑記:不插SSD就死機?兩步搞定引腳與驅動配置

RK3588平臺SSD PCIE調試踩坑記:不插SSD就死機?兩步搞定引腳與驅動配置

評論