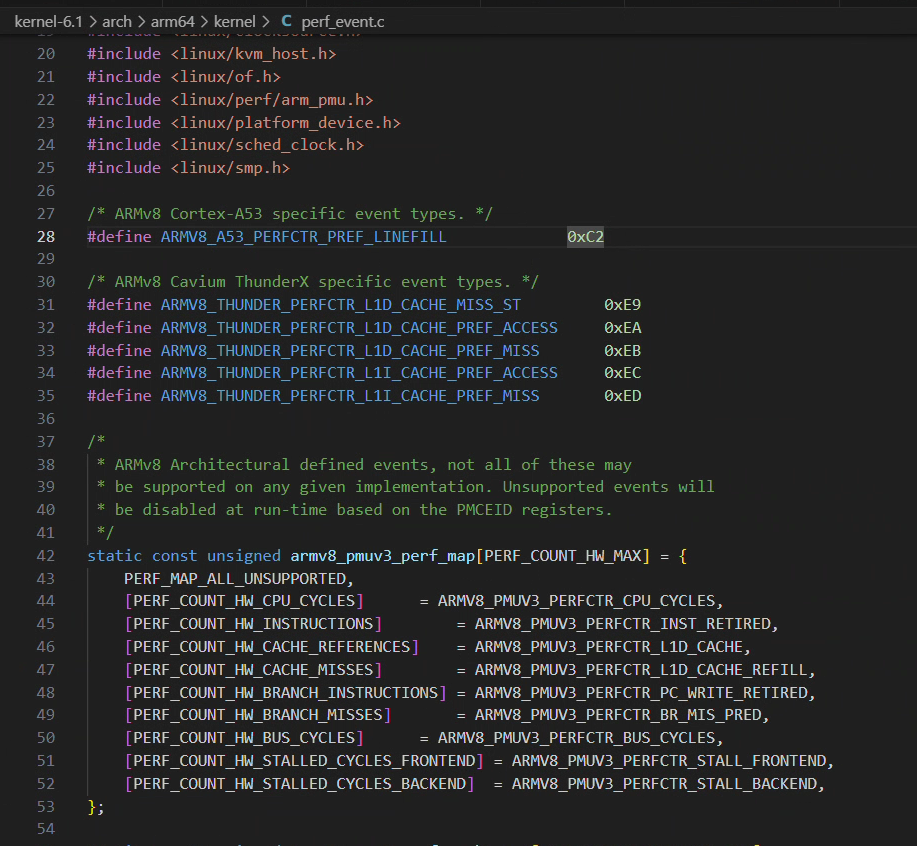

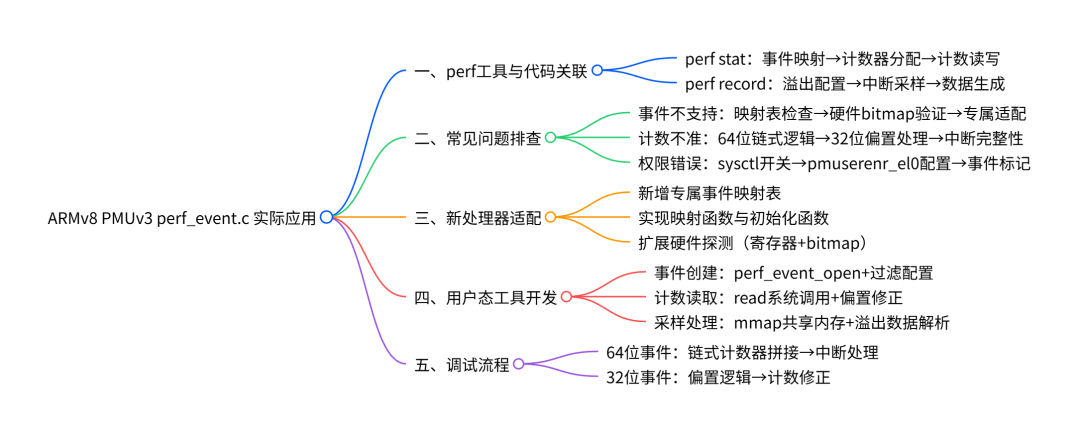

本文結(jié)合perf_event.c代碼片段,聚焦實際開發(fā)場景,將通過以下內(nèi)容展開:

1.perf工具與代碼的底層關(guān)聯(lián)邏輯及用法

2.常見問題(事件不支持、計數(shù)不準(zhǔn)等)的排查案例

3.新處理器適配與定制化監(jiān)控的實現(xiàn)方式

4.用戶態(tài)性能監(jiān)控工具開發(fā)要點

5.調(diào)試流程與代碼關(guān)聯(lián)的可視化解析(含流程圖)

6.核心內(nèi)容腦圖梳理

一、性能工具的“幕后推手”:perf如何依賴這段代碼?

perf工具的所有性能統(tǒng)計與采樣功能,均依賴perf_event.c實現(xiàn)的硬件交互邏輯,核心關(guān)聯(lián)場景如下:

1.perf stat:基礎(chǔ)性能計數(shù)

以perf stat -e cpu-cycles ./app為例,代碼執(zhí)行流程:

?事件映射:armv8_pmuv3_map_event將上層cpu-cycles(PERF_COUNT_HW_CPU_CYCLES)映射為硬件事件ARMV8_PMUV3_PERFCTR_CPU_CYCLES。

?計數(shù)器分配:armv8pmu_get_event_idx優(yōu)先為周期事件分配專屬64位計數(shù)器(ARMV8_IDX_CYCLE_COUNTER)。

?計數(shù)控制:armv8pmu_enable_event配置計數(shù)器類型(armv8pmu_write_event_type)并啟動計數(shù);程序結(jié)束后,armv8pmu_read_counter讀取值,經(jīng)armv8pmu_unbias_long_counter修正偏置后返回給perf。

2.perf record:采樣與熱點分析

以perf record -e instructions -c 1000000 ./app(每百萬條指令采樣)為例:

?溢出配置:armv8pmu_write_counter設(shè)置計數(shù)器初始值(0x1000000 - 1000000),確保觸發(fā)溢出中斷。

?中斷處理:計數(shù)器溢出后,armv8pmu_handle_irq讀取溢出狀態(tài)(pmovsclr_el0),暫停PMU避免數(shù)據(jù)skew,調(diào)用perf_event_overflow生成采樣數(shù)據(jù)(含指令地址、寄存器狀態(tài))。

?數(shù)據(jù)輸出:采樣數(shù)據(jù)寫入文件,后續(xù)可通過perf report解析熱點函數(shù)。

二、實際開發(fā)中的問題排查:從現(xiàn)象到代碼

案例1:perf提示“event not supported”(事件不支持)

現(xiàn)象

執(zhí)行perf stat -e l1d_cache_misses ./app報錯,事件無法識別。

排查流程

1.確認(rèn)事件映射:檢查armv8_pmuv3_perf_cache_map,L1D讀未命中事件是否映射為ARMV8_PMUV3_PERFCTR_L1D_CACHE_REFILL(代碼中[C(L1D)][C(OP_READ)][C(RESULT_MISS)]的配置)。

2.驗證硬件支持:armv8pmu_probe_pmu通過pmceid0_el0/pmceid1_el0寄存器生成pmceid_bitmap,若ARMV8_PMUV3_PERFCTR_L1D_CACHE_REFILL對應(yīng)的bit未置位,說明硬件不支持該事件。

3.處理器專屬適配:若為特定處理器(如Cortex-A53),檢查armv8_a53_perf_cache_map是否補充了該事件的非通用映射(部分處理器事件定義與標(biāo)準(zhǔn)不同)。

案例2:計數(shù)結(jié)果遠(yuǎn)小于預(yù)期(64位計數(shù)器異常)

現(xiàn)象

監(jiān)控長時間運行程序,cpu-cycles計數(shù)僅為1e6(遠(yuǎn)低于CPU頻率×運行時間)。

排查流程

1.64位事件判斷:通過armv8pmu_event_is_64bit確認(rèn)事件是否啟用64位計數(shù);若硬件不支持原生64位(armv8pmu_has_long_event返回false),需檢查“鏈?zhǔn)接嫈?shù)器”邏輯(armv8pmu_write_hw_counter中高低32位拼接是否正確)。

2.偏置處理驗證:armv8pmu_bias_long_counter需為32位計數(shù)器置位高32位(value |= GENMASK(63, 32)),若遺漏會導(dǎo)致高位丟失;armv8pmu_unbias_long_counter需清除高32位,確保上層讀取正確。

3.中斷完整性:armv8pmu_handle_irq需同時處理鏈?zhǔn)接嫈?shù)器的高低位溢出,若僅處理高位,會導(dǎo)致計數(shù)不連續(xù)。

案例3:用戶態(tài)程序無法讀取計數(shù)器(權(quán)限問題)

現(xiàn)象

自定義工具通過perf_event_open打開事件后,讀取計數(shù)返回0或權(quán)限錯誤。

排查流程

1.用戶訪問開關(guān):檢查sysctl_perf_user_access(通過sysctl kernel.perf_user_access查看),需設(shè)為1以允許用戶態(tài)訪問(對應(yīng)代碼中armv8_pmu_sysctl_table的配置)。

2.寄存器配置:armv8pmu_enable_user_access需設(shè)置pmuserenr_el0寄存器(ARMV8_PMU_USERENR_ER | ARMV8_PMU_USERENR_CR),若未配置,用戶態(tài)讀取會觸發(fā)陷阱。

3.事件標(biāo)記:事件需帶有PERF_EVENT_FLAG_USER_READ_CNT標(biāo)記(代碼中event->hw.flags設(shè)置),否則armv8pmu_user_event_idx會拒絕用戶態(tài)訪問。

三、新處理器適配:從代碼到落地

為新ARMv8處理器(如定制化Cortex-A78)適配性能監(jiān)控,需修改以下核心邏輯:

1.新增專屬事件映射

若處理器有特有事件(如“LLC預(yù)取命中”),需定義專屬映射表:

// 新處理器專屬緩存事件映射staticconstunsigned armv8_custom_perf_cache_map[][][] = {PERF_CACHE_MAP_ALL_UNSUPPORTED,[][C(OP_PREFETCH)][C(RESULT_HIT)] = CUSTOM_PERFCTR_LLC_PREFETCH_HIT,// 特有事件};

2.實現(xiàn)事件映射函數(shù)

關(guān)聯(lián)通用映射與專屬映射:

staticintarmv8_custom_map_event(structperf_event *event){return__armv8_pmuv3_map_event(event, NULL, &armv8_custom_perf_cache_map);}

3.注冊處理器初始化函數(shù)

通過宏PMUV3_INIT_SIMPLE綁定初始化邏輯:

PMUV3_INIT_SIMPLE(armv8_custom)// 生成armv8_custom_pmu_init函數(shù)staticintarmv8_custom_pmu_init(structarm_pmu *cpu_pmu){returnarmv8_pmu_init_nogroups(cpu_pmu,"armv8_custom", armv8_custom_map_event);}

4.擴展硬件探測邏輯

在__armv8pmu_probe_pmu中讀取處理器特有寄存器(如pmceid2_el0),擴展pmceid_bitmap以支持新事件:

// 新增特有寄存器讀取if(cpu_pmu->pmuver >= ID_AA64DFR0_EL1_PMUVer_V3P6) {u32pmceid2=read_sysreg(pmceid2_el0);bitmap_from_arr32(cpu_pmu->pmceid_bitmap +64, &pmceid2,32);// 擴展bitmap}

四、用戶態(tài)監(jiān)控工具開發(fā):基于代碼的能力擴展

若需開發(fā)輕量用戶態(tài)工具(替代perf部分功能),可基于以下代碼邏輯設(shè)計核心流程:

1.事件創(chuàng)建(perf_event_open)

?工具調(diào)用perf_event_open傳入事件類型(如PERF_COUNT_HW_CPU_CYCLES),內(nèi)核調(diào)用armv8pmu_get_event_idx分配計數(shù)器,armv8pmu_set_event_filter設(shè)置過濾條件(如僅監(jiān)控用戶態(tài):config_base |= ARMV8_PMU_EXCLUDE_EL1)。

2.計數(shù)讀取(read)

?工具通過read系統(tǒng)調(diào)用讀取計數(shù),內(nèi)核最終調(diào)用armv8pmu_read_counter,經(jīng)armv8pmu_unbias_long_counter修正后返回值。

3.采樣處理(mmap)

?若設(shè)置采樣周期(attr.sample_period),計數(shù)器溢出時,armv8pmu_handle_irq生成采樣數(shù)據(jù)并寫入mmap共享內(nèi)存,工具可實時讀取解析(如獲取熱點指令地址)。

五、調(diào)試流程可視化:從問題到代碼的映射

針對“計數(shù)偏小”這一高頻問題,結(jié)合代碼邏輯的調(diào)試流程如下,每個節(jié)點均標(biāo)注了需重點關(guān)注的函數(shù)與寄存器:

流程圖關(guān)鍵說明

1.64位事件判斷:armv8pmu_event_is_64bit通過事件類型(如PERF_COUNT_HW_CPU_CYCLES)和硬件能力(armv8pmu_has_long_event)決定是否啟用鏈?zhǔn)接嫈?shù)。

2.鏈?zhǔn)接嫈?shù)器拼接:armv8pmu_write_hw_counter需將64位周期值拆分為高低32位,分別寫入兩個通用計數(shù)器(如PMCCNTR_EL0的擴展計數(shù)器)。

3.中斷處理驗證:armv8pmu_handle_irq需讀取pmovsr(溢出狀態(tài)寄存器),確認(rèn)高低位計數(shù)器的溢出標(biāo)志均被處理,避免漏計。

4.32位偏置修正:armv8pmu_bias_long_counter置位高32位是為了防止32位計數(shù)器溢出時,符號擴展導(dǎo)致的數(shù)值錯誤(如0xFFFFFFFE被解析為- 2而非4294967294)。

六、核心內(nèi)容腦圖梳理

七、總結(jié)

perf_event.c不僅是perf工具的底層支撐,更是ARMv8性能監(jiān)控的“實操手冊”。其核心價值在于將硬件PMU的復(fù)雜特性(如64位計數(shù)、中斷溢出)封裝為上層可調(diào)用的接口,而調(diào)試的關(guān)鍵則是打通“現(xiàn)象→代碼→硬件”的鏈路——例如從“計數(shù)偏小”定位到armv8pmu_write_hw_counter的拼接邏輯,從“權(quán)限錯誤”關(guān)聯(lián)到pmuserenr_el0寄存器配置。

掌握這些細(xì)節(jié)后,開發(fā)者不僅能高效解決perf工具的使用問題,更能基于此實現(xiàn)定制化監(jiān)控(如新增處理器特有事件、開發(fā)輕量用戶態(tài)工具),最終從“工具使用者”升級為“性能調(diào)優(yōu)專家”,為ARMv8平臺的系統(tǒng)優(yōu)化提供堅實支撐。

-

中斷處理

+關(guān)注

關(guān)注

0文章

96瀏覽量

11488 -

代碼

+關(guān)注

關(guān)注

30文章

4972瀏覽量

74142 -

ARMv8

+關(guān)注

關(guān)注

1文章

37瀏覽量

14725

發(fā)布評論請先 登錄

請問如何理解ARMv8內(nèi)存屬性device

一文幫你梳理Cortex與ARMv8等基礎(chǔ)概念

ARMv8架構(gòu)資料分享

ARMv8架構(gòu)概述

ARMv8 Vector table問題該如何更好地去理解呢

ARM推新品:ARMv8首次支援64位元指令集

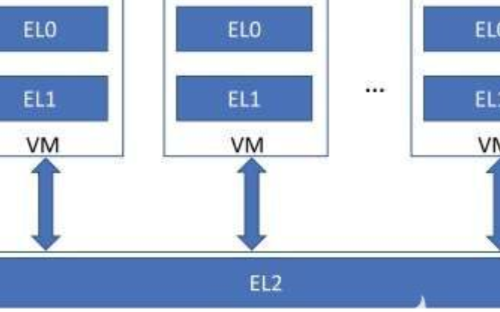

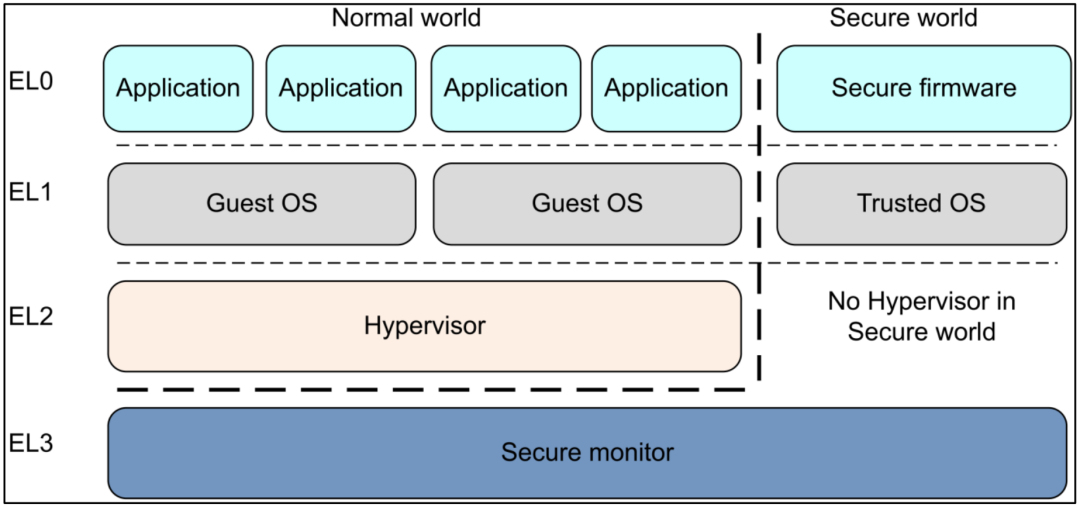

從軟件開發(fā)的角度概述ARMv8處理器架構(gòu)中的虛擬化操作

ARMv8處理器體系結(jié)構(gòu)中的虛擬化功能

Armv8架構(gòu)及虛擬化介紹

ARMv8工作模式有哪些

armv8 u-boot的啟動介紹

u-boot armv8鏈接腳本

ARMv8體系結(jié)構(gòu)入門(附流程圖+腦圖)

從代碼到實踐:ARMv8 PMUv3性能監(jiān)控的實際應(yīng)用解析

從代碼到實踐:ARMv8 PMUv3性能監(jiān)控的實際應(yīng)用解析

評論