高速先生成員--黃剛

過孔對于高速鏈路的重要性不言而喻,之前的很多文章中,高速先生主要介紹過孔本身的優化方式和遇到的問題,感覺大家都有點審美疲勞了。那今兒,Chris換點別的來講講,那換啥好呢?額,還是過孔。。。

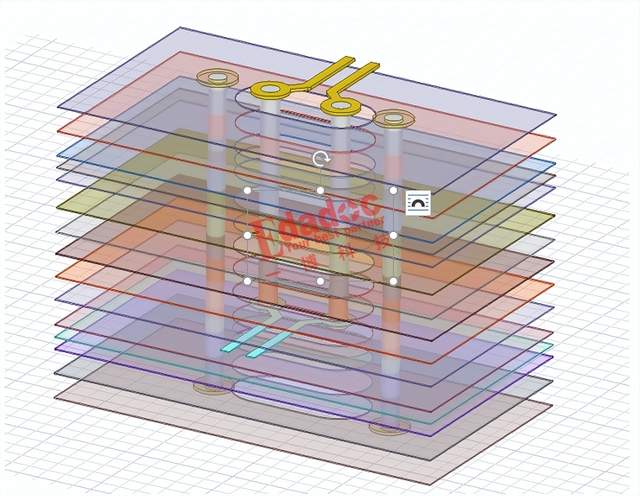

別急嘛,雖然也還是過孔,但是角度是不同的嘛。今天我們來講講兩對高速過孔之間的串擾怎么通過合理的規劃隔離地過孔放的位置來減少。說白了,我們這篇文章想研究的是兩對高速信號的過孔位置定了之后,到底地過孔要放在哪個位置能最大程度的減小串擾哈!例如下面這個設計圖,兩對信號過孔位置固定后,要怎么加地過孔的效果最好呢?

當然一些極端主義的朋友肯定第一時間跳出來,像下面那樣,我全部塞滿那肯定就很好啊!!!

額,當然的確也沒錯,只是有點不切實際而已。如果我們結合到實際項目的空間限制,每對信號過孔旁邊只能加2個隔離地過孔的時候呢?那到底放在哪個位置,過孔間的串擾更好呢?這次Chris給你們幾種選擇,分別是下圖的A,B,C三個方案。

相信大部分會選擇方案A的方式吧,把地過孔打在信號過孔水平方向的左右兩邊。對比方案A,方案B就是在豎直分別往上下遠離點來打,方案C就是在豎直方向分別往上下靠近點來打。各位設計工程師你們覺得上面三種方案的串擾到底哪種好呢?

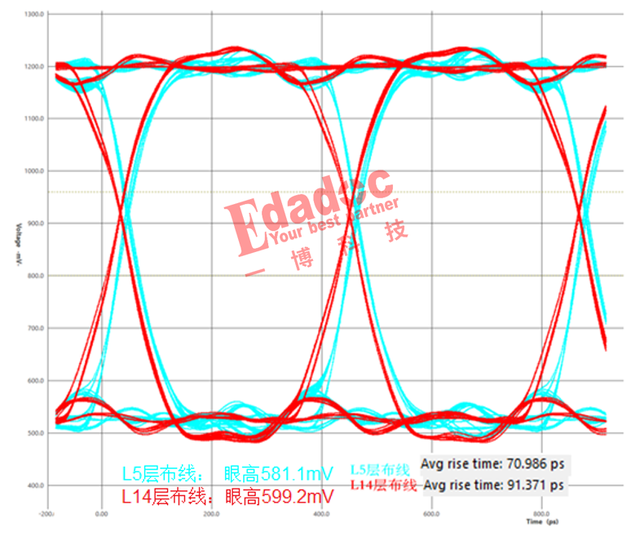

罷了罷了,各位感性的朋友們,Chris還是通過相對比較理性的仿真結果來告訴你們吧。我們從方案B的遠離的方案慢慢的往方案C的靠近的方案去掃描,仿真結果告訴我們的是,方案C的地過孔靠近的方案串擾是最好的,如下圖:

不服?那Chris再考大家一題唄,同樣也還是這兩對信號過孔,我們在兩對信號過孔中間只允許加2個隔離地過孔,同樣Chris給大家三種選擇的方案,那你們又覺得以下的哪種方案串擾是最好的呢?

這次還要硬撐不,要不結合上面的那個case好好想想?經過一系列的動腦筋和對比分析后,是不是大家一致覺得方案B是最好的呢?

主要是上面第一個case之后得到的靈感,也就是隔離地過孔越靠近,串擾越好。然而,仿真掃描后的結果又會讓大家再跌一次眼鏡。對從近到遠的地過孔位置進行掃描,發現靠近的是最差的(紅色曲線),遠離的這種反而是串擾最好的設計。

還來不?要不算了吧,大家先消化消化上面2個case先吧,想想為什么不是我們想象的那種情況是串擾最好的設計。同時也再一次的證明了過孔的優化真的沒那么簡單,絕對不是簡單的拍個腦袋就能得到最好的方案。無論是高速過孔本身的優化,還是過孔間串擾的優化,其實都是很難通過經驗甚至常規理論去解決,目前看起來,仿真絕對是更好的選擇了哈!

問題:根據你們的經驗,提出幾種有效的改善高速信號過孔串擾的PCB設計方法?

審核編輯 黃宇

-

過孔

+關注

關注

2文章

223瀏覽量

22716 -

PCB

+關注

關注

1文章

2342瀏覽量

13204

發布評論請先 登錄

PCB過孔STUB對DDRX地址信號的影響

技術資訊 I Allegro設計中的過孔陣列設計

PCB反焊盤的樣子越詭異,高速過孔的性能越好?

高速AC耦合電容挨得很近,PCB串擾會不會很大……

PCB設計中過孔為什么要錯開焊盤位置?

這下真的EMO了:過孔阻抗越匹配,信號衰減反而越大!

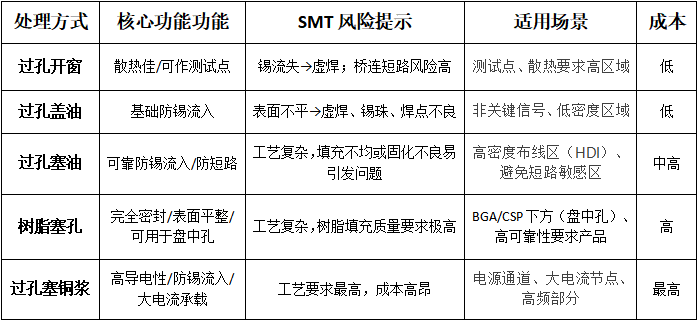

過孔處理:SMT訂單中的隱形裁判

過孔處理:SMT訂單中的隱形裁判

Allegro Skill布線功能-改變過孔網絡介紹與演示

Allegro Skill布線功能-添加差分過孔禁布區

隔離地過孔要放哪里,才能最有效減少高速信號過孔串擾?

隔離地過孔要放哪里,才能最有效減少高速信號過孔串擾?

評論